目录

一.ARP简介

1.1ARP概述

ARP(Address Resolution Protocol),即地址解析协议,是根据 IP 地址(逻辑地址)获取 MAC 地址的一种 TCP/IP 协议。在以太网中,一个主机和另一个主机进行通信,必须要知道目的主机的 MAC 地址(物理地址),而目的 MAC 地址的获取由 ARP 协议完成。1.2ARP映射

MAC 地址在网络中表示网卡的 ID,每个网卡都需要并有且仅有一个 MAC 地址。在获取到目的 MAC 地址之后,将目的 MAC 地址更新至 ARP 缓存表中,称为 ARP 映射。ARP 映射是指将 IP 地址和 MAC 地址映射起来,分为静态映射和动态映射。静态映射:静态映射指手动创建一张 ARP 表,把 IP 地址和 MAC 地址关联起来。手动绑定之后,源主机在通信之前,就可以直接从 ARP 表中直接找到 IP 地址对应的 MAC 地址。

动态映射:动态映射指使用协议来获取相对应的物理地址,之所以用动态这个词是因为这个过程是自动完成的,一般应用程序的用户或系统管理员不必关心。已经设计出用于实现动态映射协议的有 ARP 和 RARP(逆地址解析协议)两种。

1.3ARP工作方式

ARP请求: 源主机发起查询目的 MAC 地址的报文称为 ARP 请求。 ARP应答:目的主机响应源主机并发送包含本地 MAC 地址的报文称为 ARP 应答。 免费ARP:源主机向目的主机发送的报文中的MAC和IP都为源主机。 作用是检查是否存在主机冲突。1.4以太网ARP数据包格式

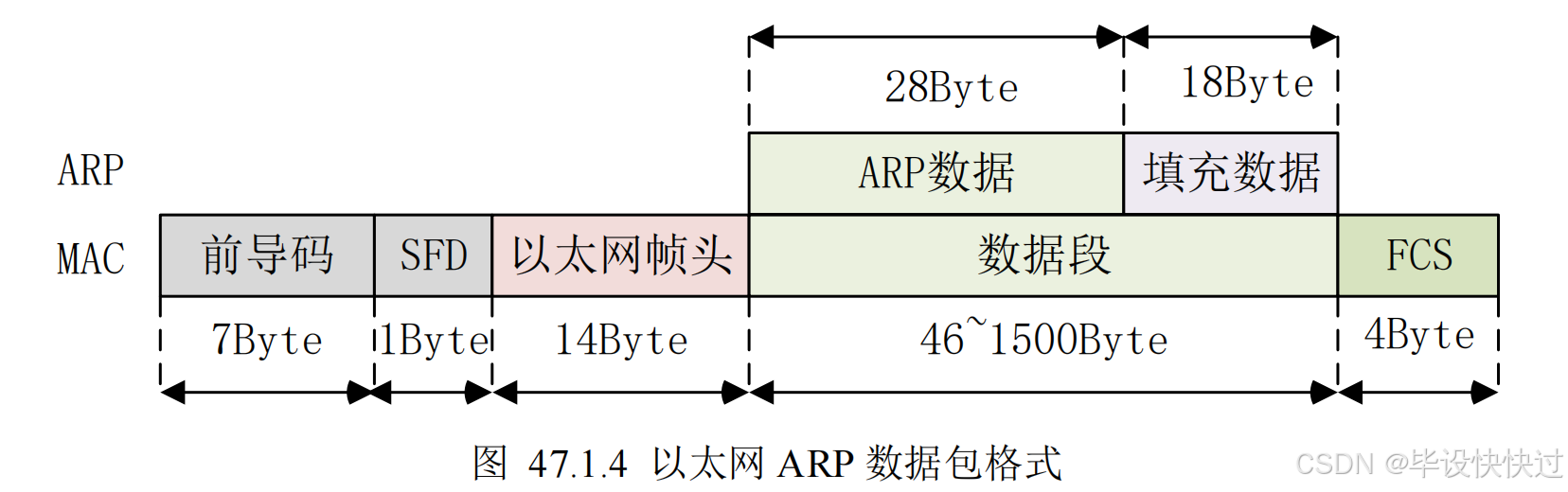

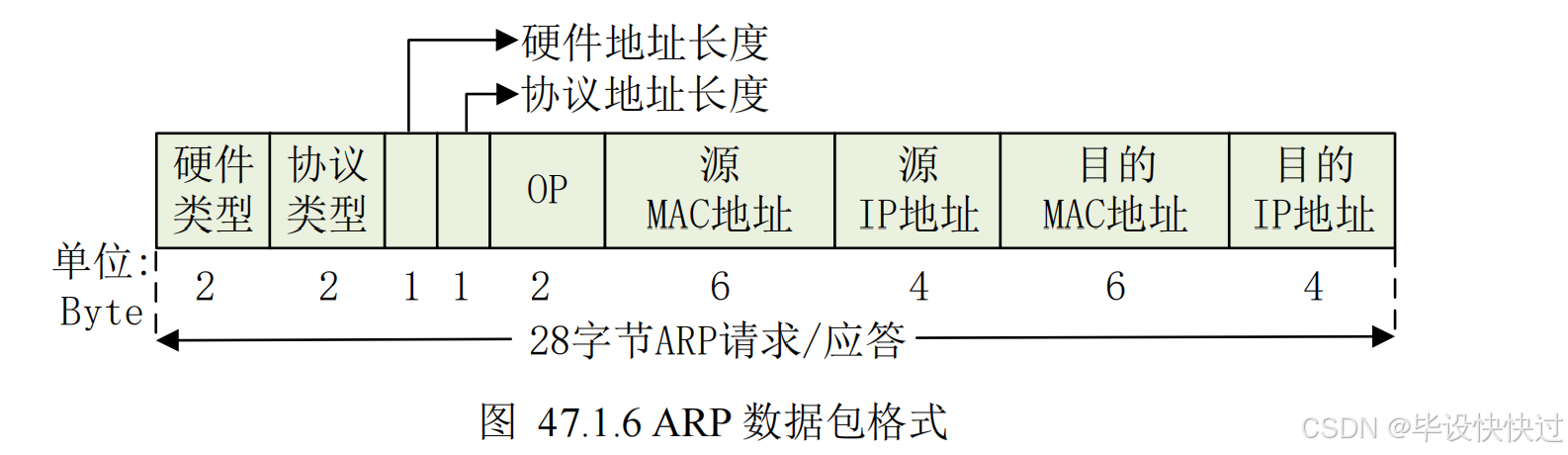

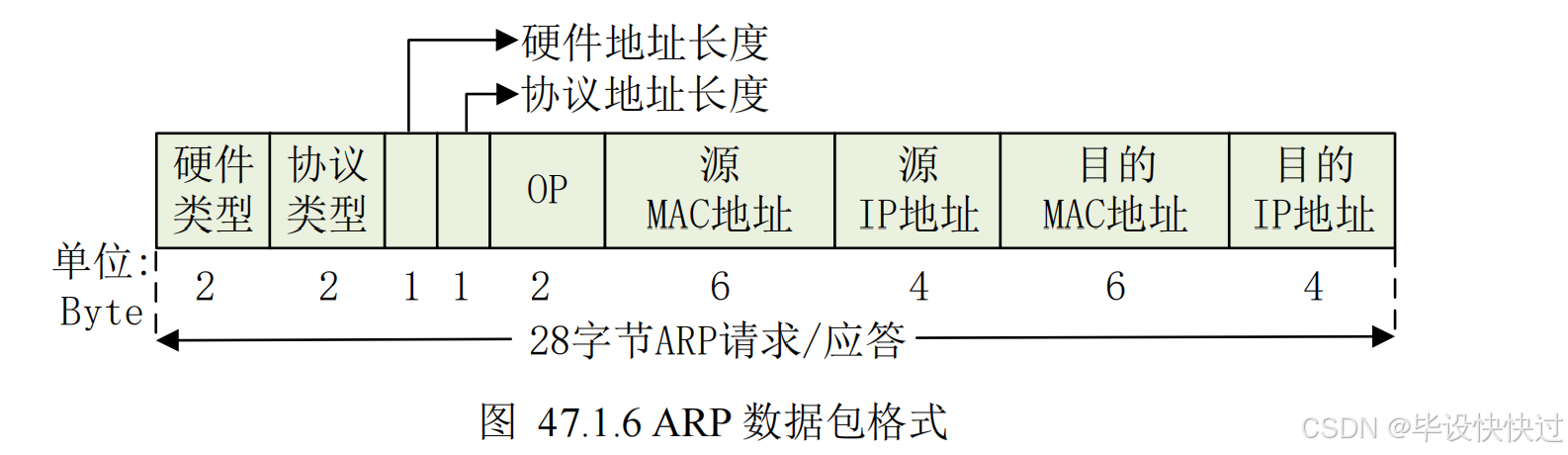

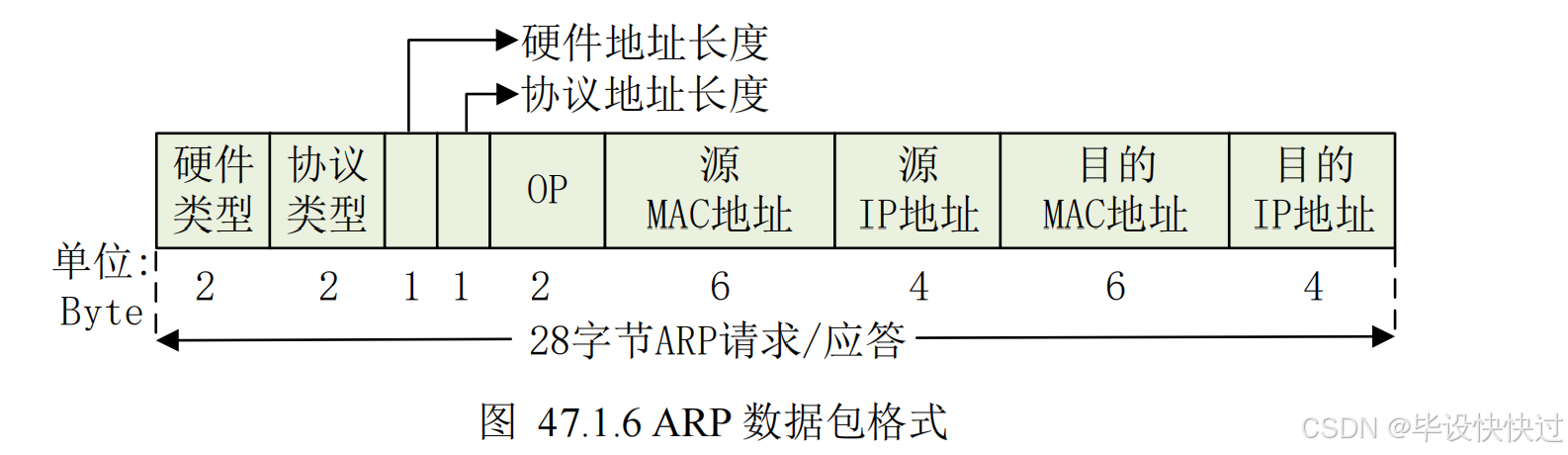

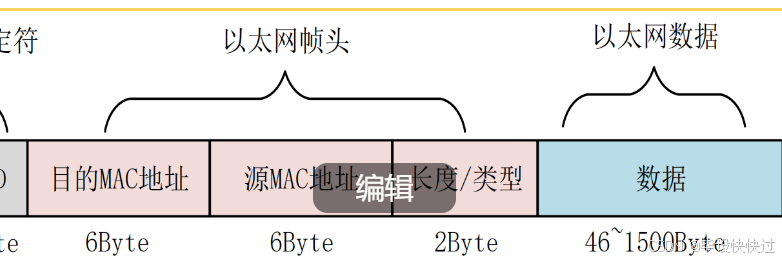

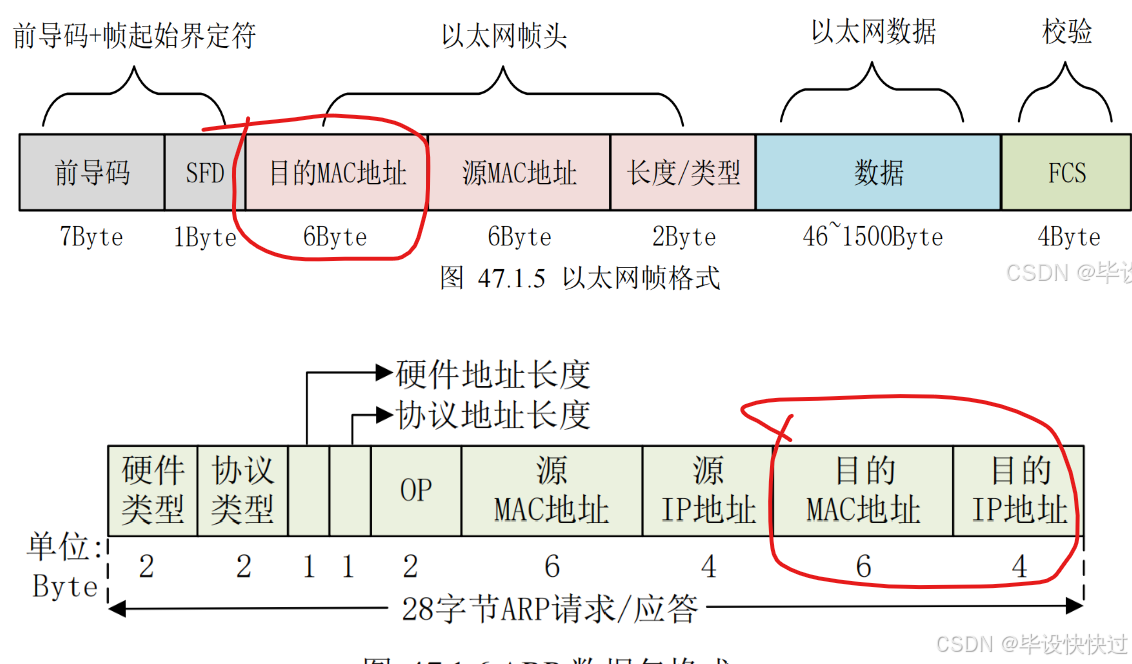

ARP 协议通过以太网进行传输,那么必须也要按照以太网所规定的格式进行传输,以太网通信是以数据包的形式传输,由下图可以看出,ARP 数据位于以太网帧格式的数据段。 以太网后三段(以太网帧头、数据段、FCS)需要传输64Byte,填充数据len=64-14-28-4=18Byte。

以太网后三段(以太网帧头、数据段、FCS)需要传输64Byte,填充数据len=64-14-28-4=18Byte。 1.5ARP协议

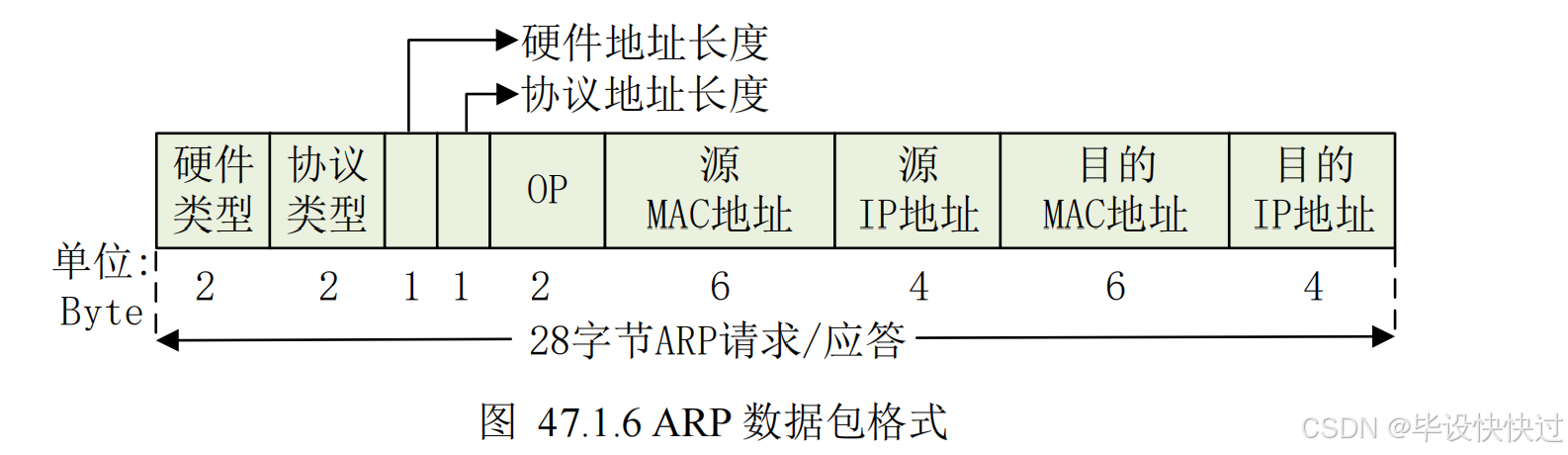

TCP/IP 是网络使用中最基本的通信协议,它包括上百个各种功能的协议,如:TCP、IP、 ARP、UDP 等。而 TCP 协议和 IP 协议是保证数据完整传输的两个重要的协议,因此 TCP/IP 协议用来表示Internet 协议簇。 ARP 协议属于 TCP/IP 协议簇的一种。 硬件类型(Hardware type):硬件地址的类型,1 表示以太网地址。 协议类型(Protocol type):要映射的协议地址类型,ARP 协议的上层协议为 IP 协议,因此该协议类型为 IP 协议,其值为 0x0800。 硬件地址长度(Hardware size):硬件地址(MAC 地址,长度为6)的长度,以字节为单位。 协议地址长度(Protocol size):IP 地址的长度,IP地址是32位,32/8=4,以字节为单位。 OP(Opcode):操作码,用于表示该数据包为 ARP 请求或者 ARP 应答。1 表示 ARP 请求,2 表示 ARP应答。 源 MAC 地址:发送端的硬件地址。 源 IP 地址:发送端的协议(IP)地址。 目的 MAC 地址:接收端的硬件地址,在 ARP 请求时由于不知道接收端 MAC 地址,因此该字段为广播地址,即 48’hff_ff_ff_ff_ff_ff。 目的 IP 地址:接收端的协议(IP)地址。

硬件类型(Hardware type):硬件地址的类型,1 表示以太网地址。 协议类型(Protocol type):要映射的协议地址类型,ARP 协议的上层协议为 IP 协议,因此该协议类型为 IP 协议,其值为 0x0800。 硬件地址长度(Hardware size):硬件地址(MAC 地址,长度为6)的长度,以字节为单位。 协议地址长度(Protocol size):IP 地址的长度,IP地址是32位,32/8=4,以字节为单位。 OP(Opcode):操作码,用于表示该数据包为 ARP 请求或者 ARP 应答。1 表示 ARP 请求,2 表示 ARP应答。 源 MAC 地址:发送端的硬件地址。 源 IP 地址:发送端的协议(IP)地址。 目的 MAC 地址:接收端的硬件地址,在 ARP 请求时由于不知道接收端 MAC 地址,因此该字段为广播地址,即 48’hff_ff_ff_ff_ff_ff。 目的 IP 地址:接收端的协议(IP)地址。二.以太帧简介

2.1 以太帧概述

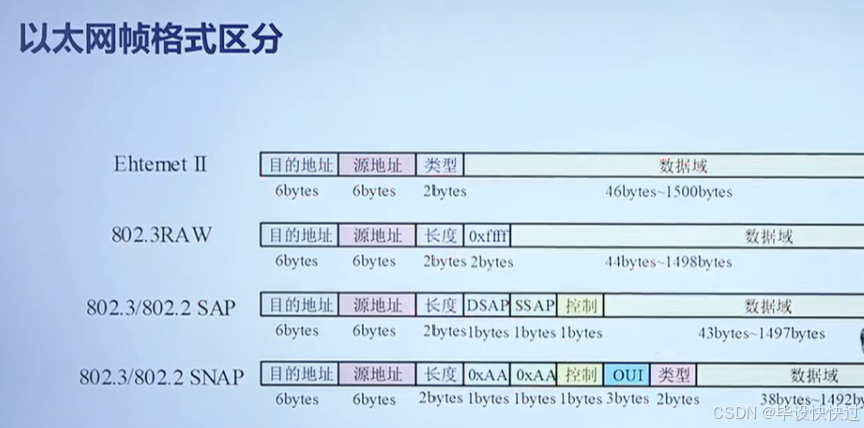

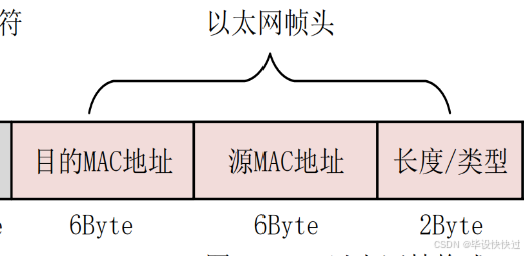

在以太网链路上的数据包称作以太帧,常见的以太网帧格式有Ethernet II、Ethernet802.3 RAW等。

2.2以太帧传输方式

单播:值从单一的源端发送到单一的目的端。单播地址:第一个字节的最低位为 0,比如 00-00-00-11-11-11。

广播:表示帧从单一的源发送到共享以太网上的所有主机。组播地址:第一个字节的最低位为 1,比如 01-00-00-11-11-11。

组播:组播可以理解为选择性的广播。广播地址:所有 48bit 全为 1,即 FF-FF-FF-FF-FF-FF。

2.3以太网帧格式

2.4以太网帧间隙

以太网相邻两帧之间的时间间隔,即帧间隙(IFG,Interpacket Gap)。帧间隙的时间就是网络设备和组件在接收一帧之后,需要短暂的时间来恢复并为接收下一帧做准备的时间。IFG 的最小值是 96 bit time。

10Mbit/s 最小时间为:96*100ns = 9600ns;

100Mbit/s 最小时间为:96*10ns = 960ns;

1000Mbit/s 最小时间为:96*1ns = 96ns。三.PHY芯片通信接口:MII

3.1概述

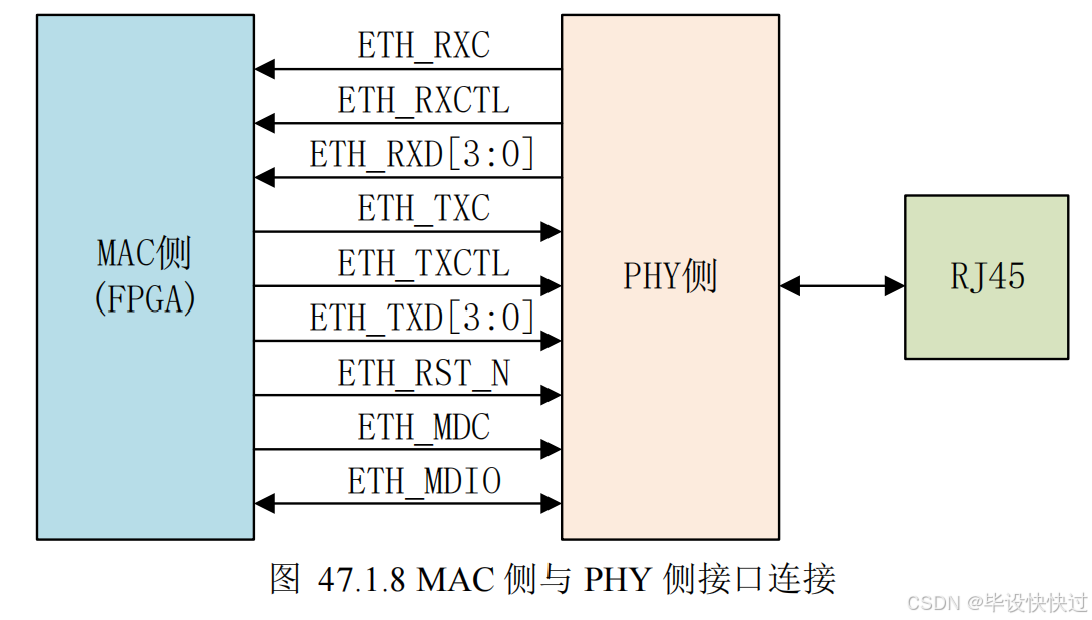

MII(Medium Independent Interface)介质独立接口,该接口一般应用于以太网硬件平台的MAC层和PHY层之间,MII接口类型有MII、RMII、GMII、RGMII等。 MII(Medium Independent Interface,媒体独立接口):MII 支持 10Mbps 和 100Mbps 的操作,数据位宽为 4 位,在 100Mbps 传输速率下,时钟频率为 25Mhz。 RMII(Reduced MII简化媒体独立接口):RMII 是 MII 的简化版,数据位宽为 2 位,在 100Mbps 传输速率下,时钟频率为 50Mhz。 GMII(Gigabit MII千兆比特媒体独立接口):GMII 接口向下兼容 MII 接口,支持 10Mbps、100Mbps 和 1000Mbps 的操作,数据位宽为 8 位,在 1000Mbps 传输速率下,时钟频率为 125Mhz。 RGMII(Reduced GMII简化千兆比特媒体独立接口):RGMII 是 GMII 的简化版,数据位宽为 4 位,在 1000Mbps 传输速率下,时钟频率为 125Mhz,在时钟的上下沿同时采样数据。在 100Mbps 和 10Mbps 通信速率下,为单个时钟沿采样。3.2RGMII接口连接图

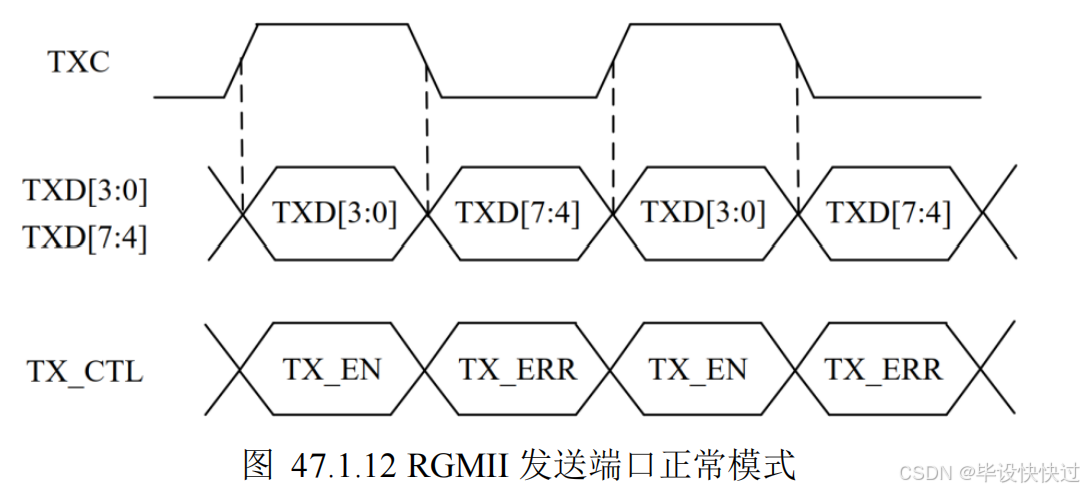

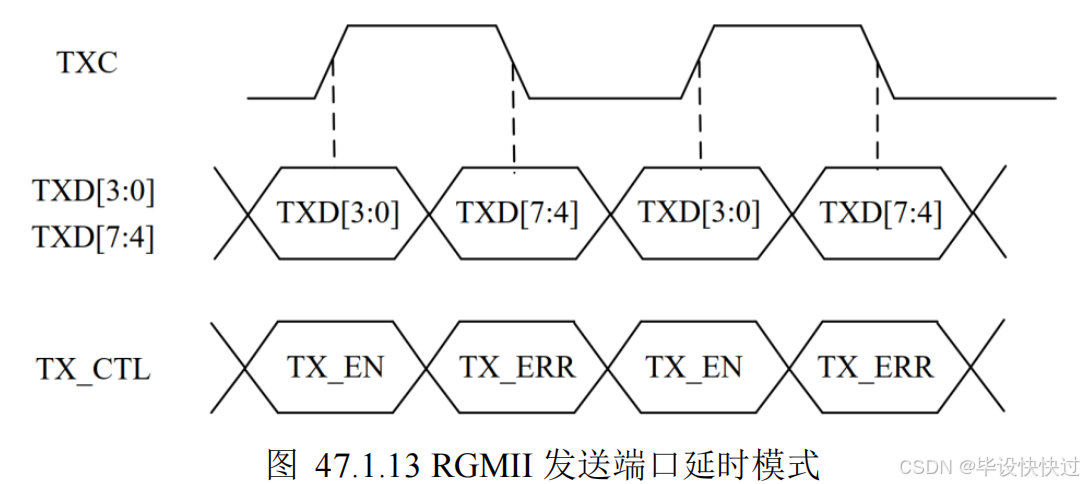

ETH_RXC:接收数据参考时钟,1000Mbps 速率下,时钟频率为 125MHz,时钟为上下沿同时采样; 100Mbps 速率下,时钟频率为 25MHz;10Mbps 速率下,时钟频率为 2.5MHz,ETH_RXC 由 PHY 侧提供。 ETH_RXCTL(ETH_RX_DV):接收数据控制信号。 ETH_RXD:四位并行的接收数据线。 ETH_TXC:发送参考时钟,1000Mbps 速率下,时钟频率为 125MHz,时钟为上下沿同时采样;100Mbps速率下,时钟频率为 25MHz;10Mbps 速率下,时钟频率为 2.5MHz,ETH_TXC 由 MAC 侧提供。 ETH_TXCTL(ETH_TXEN):发送数据控制信号。 ETH_TXD:四位并行的发送数据线。 ETH_RESET_N:芯片复位信号,低电平有效。 ETH_MDC:数据管理时钟(Management Data Clock),该引脚对 ETH_MDIO 信号提供了一个同步的时钟。 ETH_MDIO:数据输入/输出管理(Management Data Input/Output),该引脚提供了一个双向信号用于传递管理信息。 ETH_MDC 和 ETH_MDIO 为 MDIO 接口引脚,用于配置 PHY 芯片内部寄存器;由于 PHY 芯片的内部寄存器在默认配置下也可以正常工作,因此本次实验没有对 MDIO 接口进行读写操作,只用到了以太网的 RGMII 接口信号和复位信号。 ETH_TXCTL 和 ETH_RXCTL 控制信号同样采用 DDR (DDR在一个CLK周期传输两次数据,分别在上升沿和下降沿各传输一次数据。)的方式在一个时钟周期内传输两位控制信号,即上升沿发送/接收数据使能(TX_EN/RX_ DV)信号,下降沿发送/接收使能信号与错误信号的异或值(TX_ERR xor TX_EN、RX_ERR xor RX_DV)。当 RX_DV 为高电平(表示数据有效),RX_ERR 为低电平(表示数据无错误),则异或的结果值为高电平,因此只有当 ETH_RXCTL 和 ETH_TXCTL 信号的上下沿同时为高电平时,发送和接收的数据有效且正确。

ETH_RXC:接收数据参考时钟,1000Mbps 速率下,时钟频率为 125MHz,时钟为上下沿同时采样; 100Mbps 速率下,时钟频率为 25MHz;10Mbps 速率下,时钟频率为 2.5MHz,ETH_RXC 由 PHY 侧提供。 ETH_RXCTL(ETH_RX_DV):接收数据控制信号。 ETH_RXD:四位并行的接收数据线。 ETH_TXC:发送参考时钟,1000Mbps 速率下,时钟频率为 125MHz,时钟为上下沿同时采样;100Mbps速率下,时钟频率为 25MHz;10Mbps 速率下,时钟频率为 2.5MHz,ETH_TXC 由 MAC 侧提供。 ETH_TXCTL(ETH_TXEN):发送数据控制信号。 ETH_TXD:四位并行的发送数据线。 ETH_RESET_N:芯片复位信号,低电平有效。 ETH_MDC:数据管理时钟(Management Data Clock),该引脚对 ETH_MDIO 信号提供了一个同步的时钟。 ETH_MDIO:数据输入/输出管理(Management Data Input/Output),该引脚提供了一个双向信号用于传递管理信息。 ETH_MDC 和 ETH_MDIO 为 MDIO 接口引脚,用于配置 PHY 芯片内部寄存器;由于 PHY 芯片的内部寄存器在默认配置下也可以正常工作,因此本次实验没有对 MDIO 接口进行读写操作,只用到了以太网的 RGMII 接口信号和复位信号。 ETH_TXCTL 和 ETH_RXCTL 控制信号同样采用 DDR (DDR在一个CLK周期传输两次数据,分别在上升沿和下降沿各传输一次数据。)的方式在一个时钟周期内传输两位控制信号,即上升沿发送/接收数据使能(TX_EN/RX_ DV)信号,下降沿发送/接收使能信号与错误信号的异或值(TX_ERR xor TX_EN、RX_ERR xor RX_DV)。当 RX_DV 为高电平(表示数据有效),RX_ERR 为低电平(表示数据无错误),则异或的结果值为高电平,因此只有当 ETH_RXCTL 和 ETH_TXCTL 信号的上下沿同时为高电平时,发送和接收的数据有效且正确。 3.3RGMII接口时序

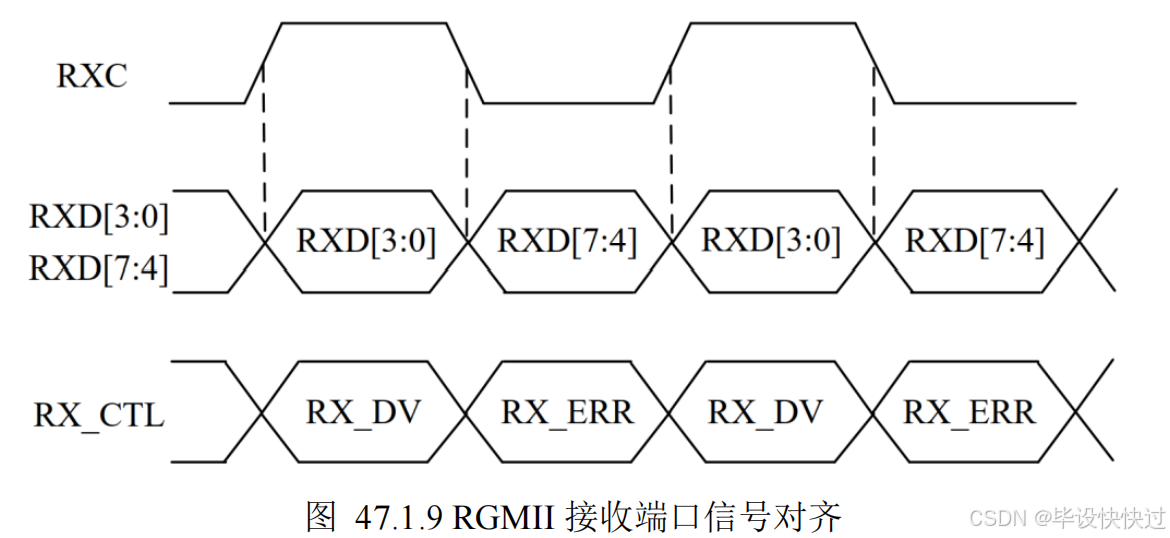

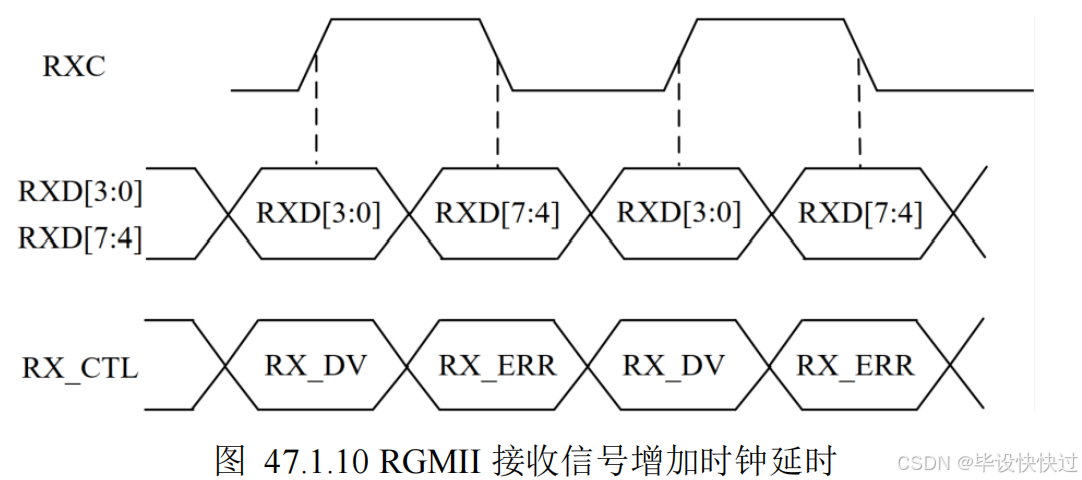

RXC 的上下边沿与 RXD 和 RX_CTL 信号对齐,相位相同。

因为上下沿采样时,数据也在更新,因此采集的数据容易有误,采用接收时钟延迟部分,使得在数据更新的中间进行采样,从而保证采样数据的准确性。

四.Xilinx原语

4.1原语概述

原语是 Xilinx 器件底层硬件中的功能模块,它使用专用的资源来实现一系列的功能。相比于 IP 核,原语的调用方法更简单,但是一般只用于实现一些简单的功能。本章主要用到了 BUFG、BUFIO、IDDR、ODDR、IDELAYE2 和 IDELAYCTRL。

以Xilinx为例,共分为10类:计算组件、IO端口组件、寄存器/锁存器、时钟组件、处理器组件、移位寄存器、配置和检测组件、RAM/ROM组件、Slice/CLB组件以及G-tranceiver。

4.2时钟组件

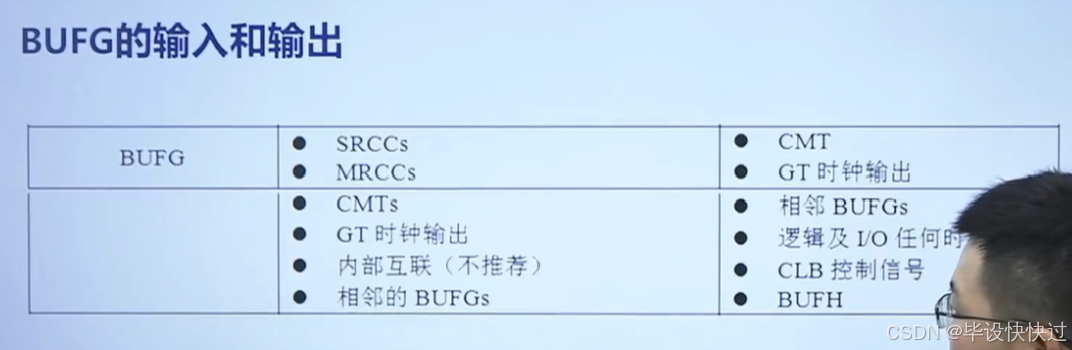

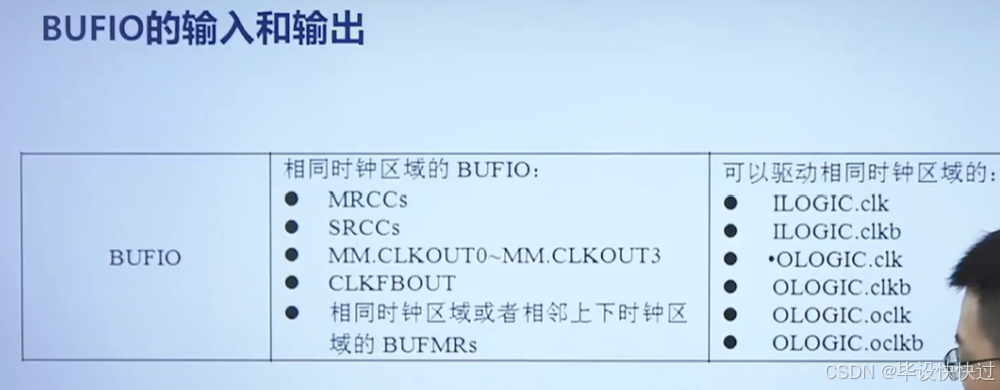

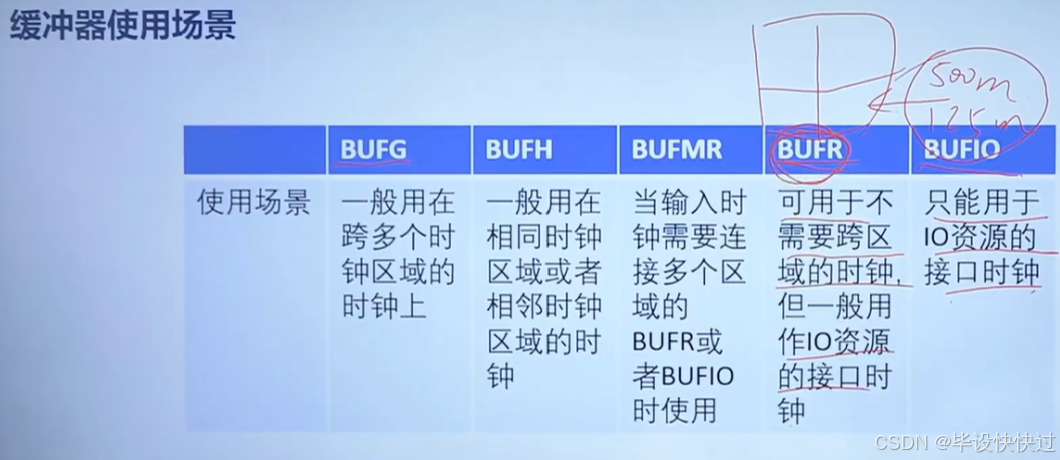

时钟组件包括各种全局时钟缓冲器、全局时钟复用器、普通I/O本地的时钟缓冲器以及高级时钟管理模块。与其相关的原语包括BUFG、BUFR、BUFH、BUFIO、BUFGCE、BUFGDLL和DCM等。

下图中包含4个BUFIO,4个BUFR,2个BUFMR。

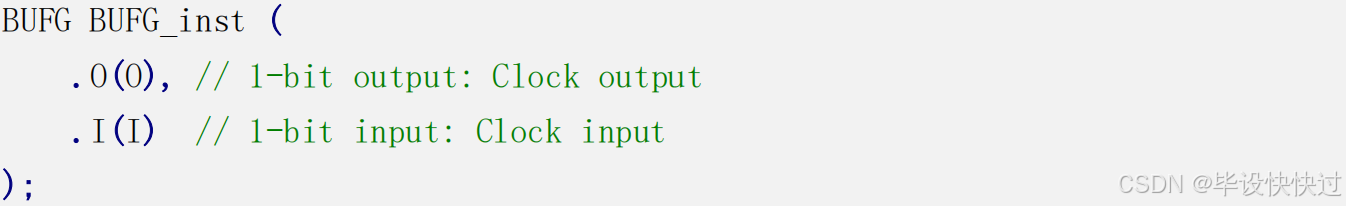

4.2.1BUFG

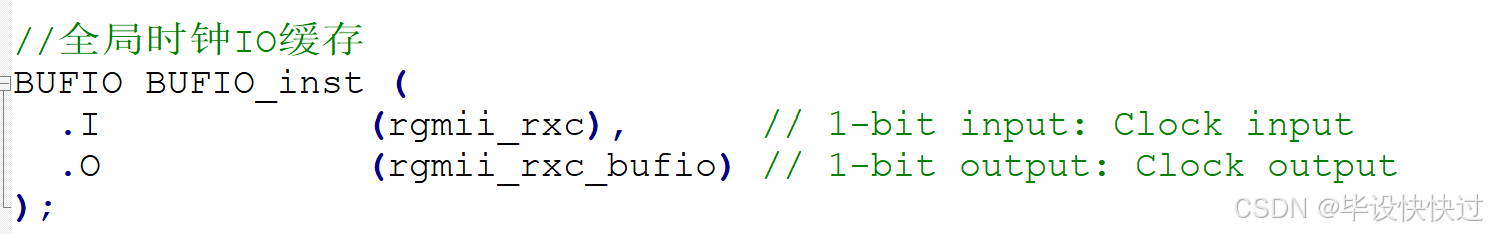

BUFG:全局缓冲,BUFG 的输出到达 FPGA 内部的 IOB、CLB、块 RAM 的时钟延迟和抖动最小。BUFG原语模板如下:

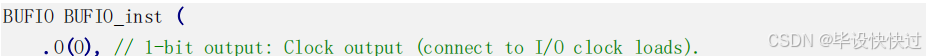

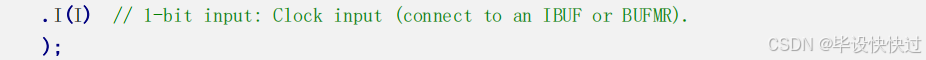

4.2.2 BUFIO

BUFIO:IO时钟缓冲器,其独立于全局时钟资源,适合采集源同步数据。它只能驱动 IO Block里面的逻辑,不能驱动 CLB 里面的 LUT,REG 等逻辑。BUFIO 原语模板如下:

4.2.3缓冲器使用场景

4.3I/O端口组件

I/O组件提供了标准单端I/O缓存(IBUF/OBUF)、DDR专用I/O信号缓存(IDDR/ODDR)、可变抽头延迟链(IDELAY/ODELAY)、上拉(PULLUP)、下拉(PULLDOWN)以及单端信号和差分信号之间的相互转换(IBUFDS/OBUFDS)等。

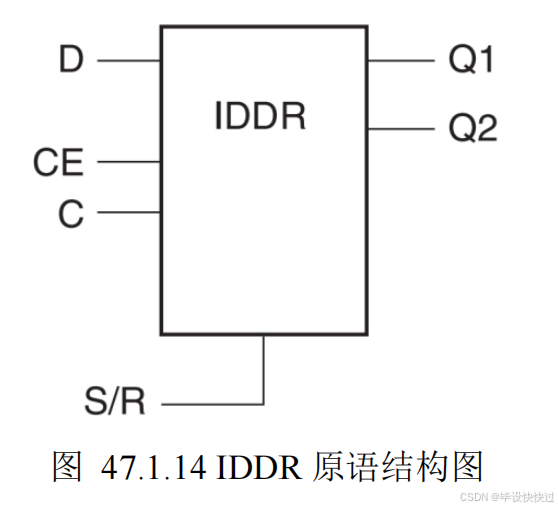

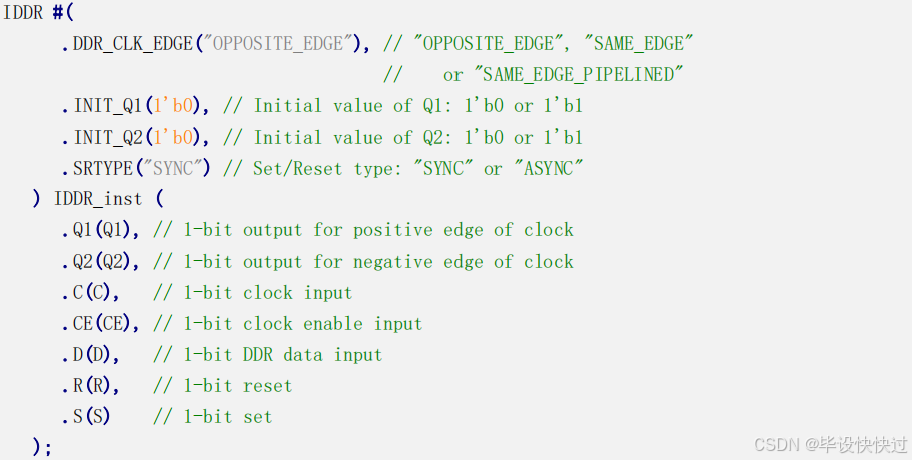

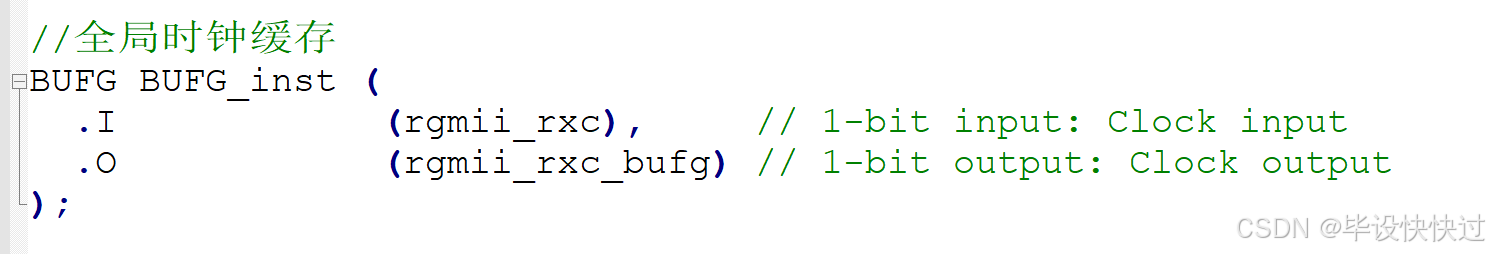

4.3.1IDDR

IDDR概述:输入数据的双沿采样,是ILOGIC块中专用的寄存器,用于实现输入数据双沿采样,将输入的上下边沿 DDR 信号,转换成两位单边沿 SDR 信号在 7 系列设备的 ILOGIC block 中有专属的 registers 来实现 input double-data-rate(IDDR) registers。

IDDR原语结构图如下:

IDDR原语模板如下:

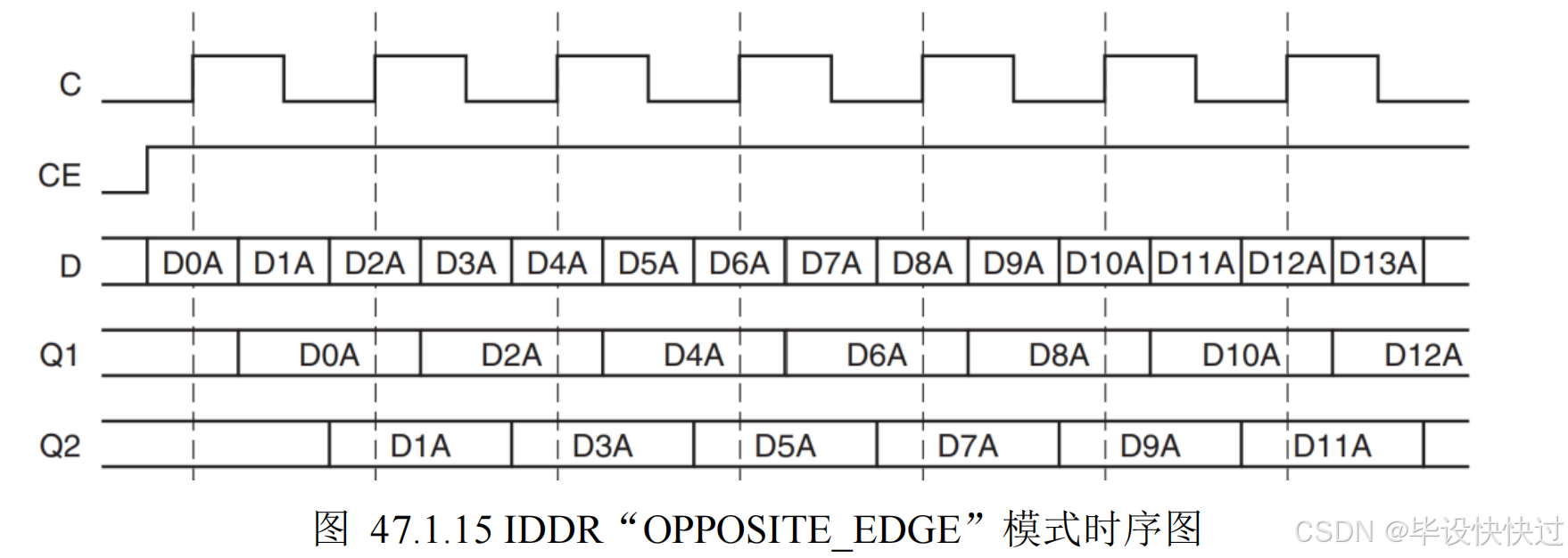

OPPOSITE_EDGE模式下:

Q1在上升沿采样数据,Q2在下降沿采样数据。

SAME_EDGE模式下:

Q1和Q2都为上升沿采样数据。但此时Q1和Q2错位不利于采集。

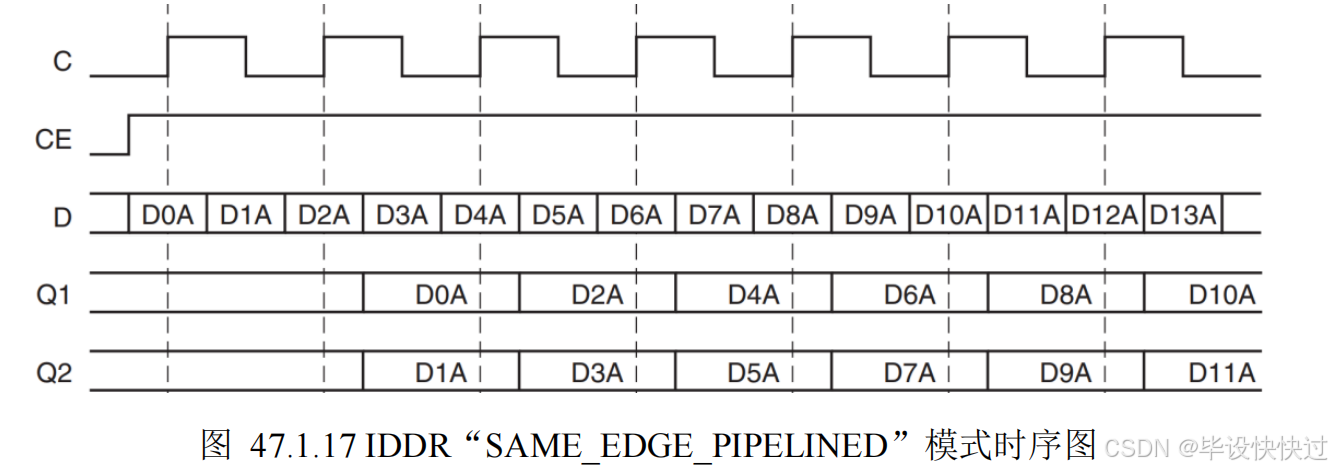

SAME_EDGE_PIPELINED模式下 :

相当于Q1在上面模式下打一拍,这样Q1和Q2数据对齐,利于采样。

4.3.2ODDR

ODDR:输出数据的双沿采样,是OLOGIC块中专用的寄存器 ,用于实现输出数据双沿采样。

ODDR原语结构图如下:

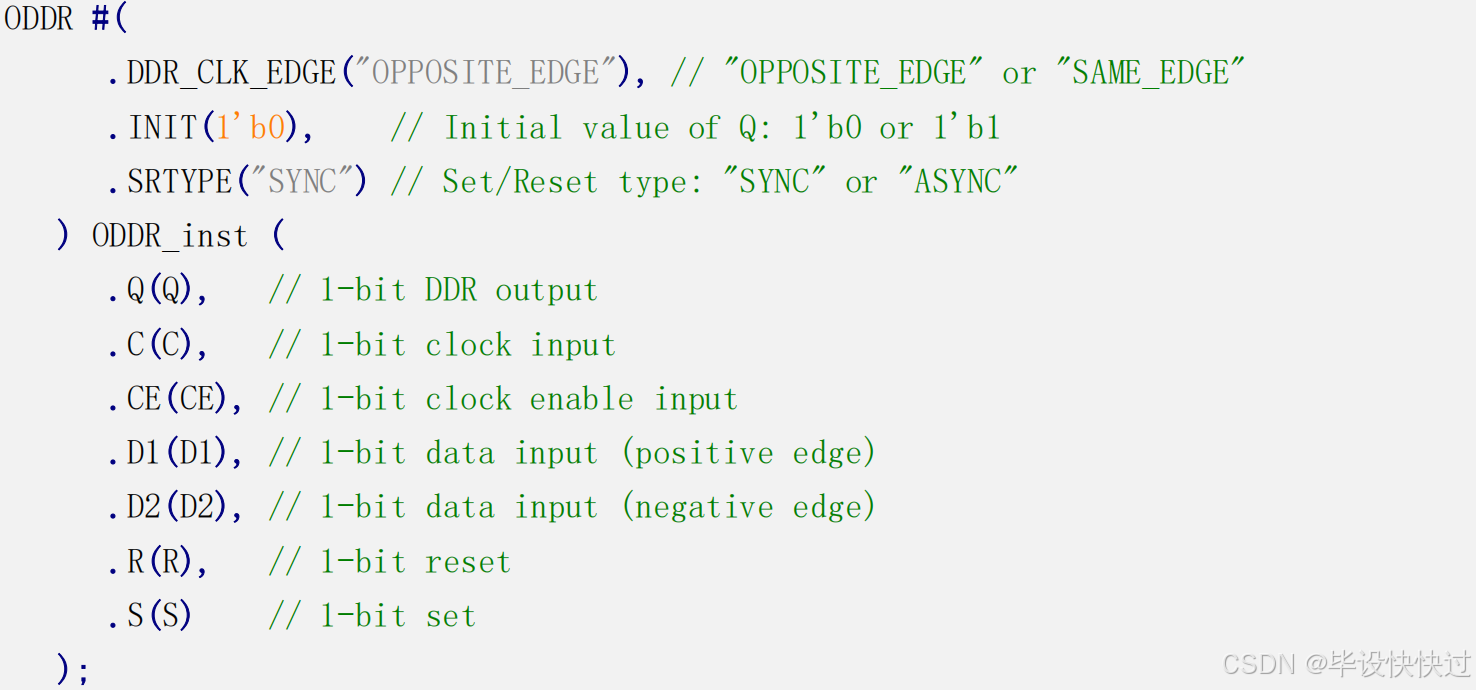

ODDR原语模板如下:

OPPOSITE_EDGE 模式下:

D1下降沿更新数据,D2上升沿更新数据,OQ上升沿采样D1,下降沿采样D2。

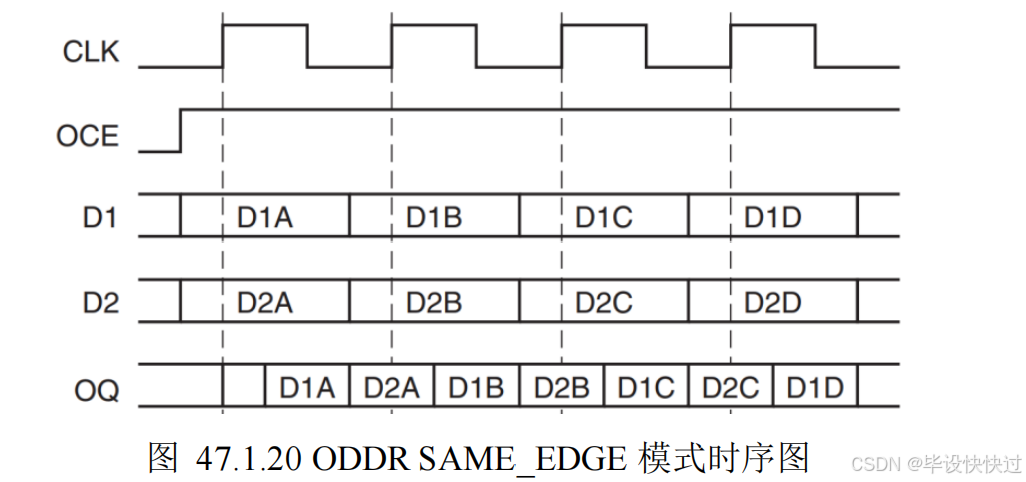

SAME_EDGE 模式下:

D1和D2都为上升沿更新数据,OQ上升沿采样D1,下降沿采样D2。

4.3.3IDELAY

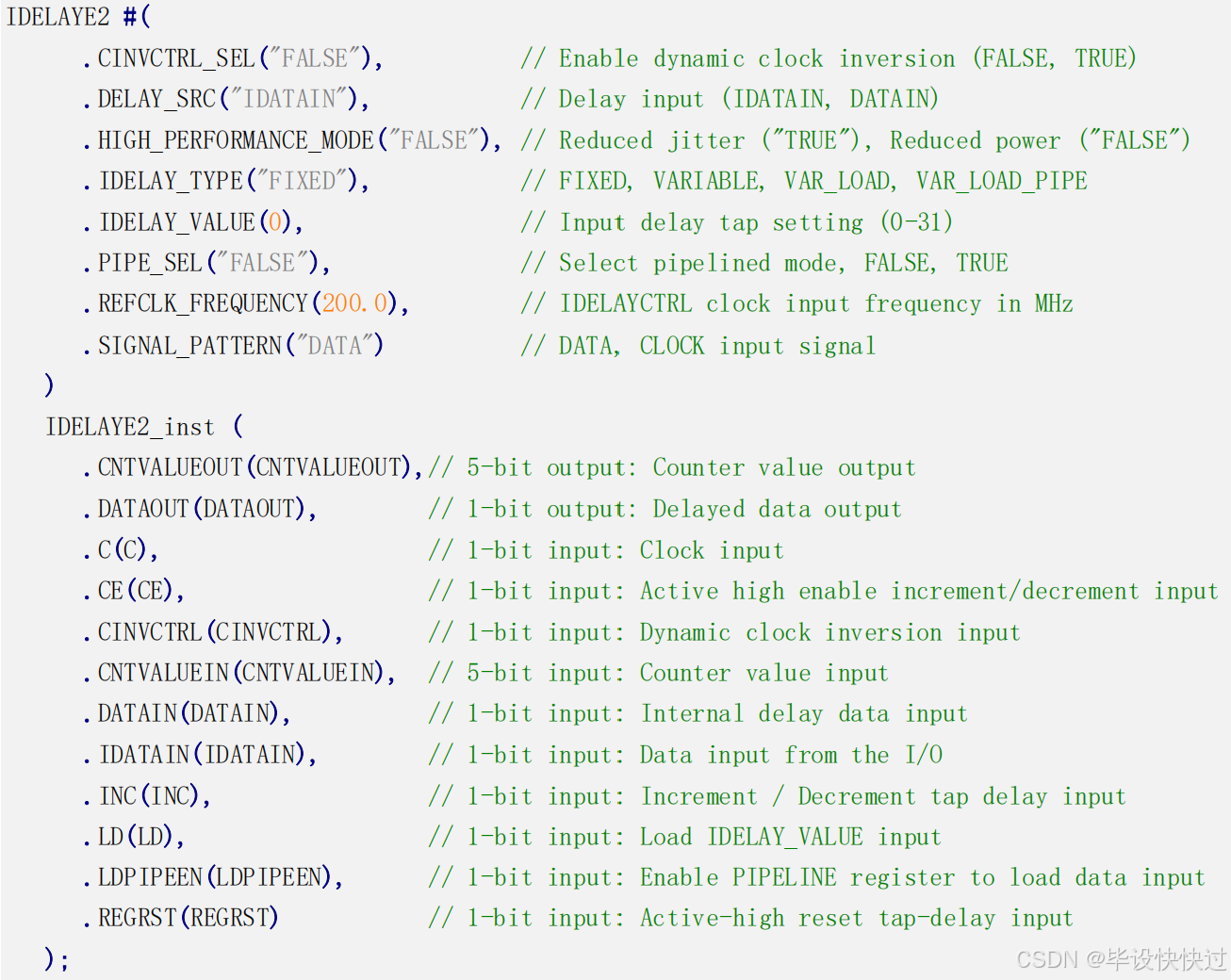

IDELAYL:每个I/O模块都包含了一个可编程的延迟原语,称作IDELAYE2。IDELAY2是一个可编程的31阶延迟原语,它既可以应用于组合逻辑也可以应用于时序逻辑或者同时用于两者。用于在信号通过引脚进入芯片内部之前,进行延时调节。

IDELAYE2 原语模板如下:

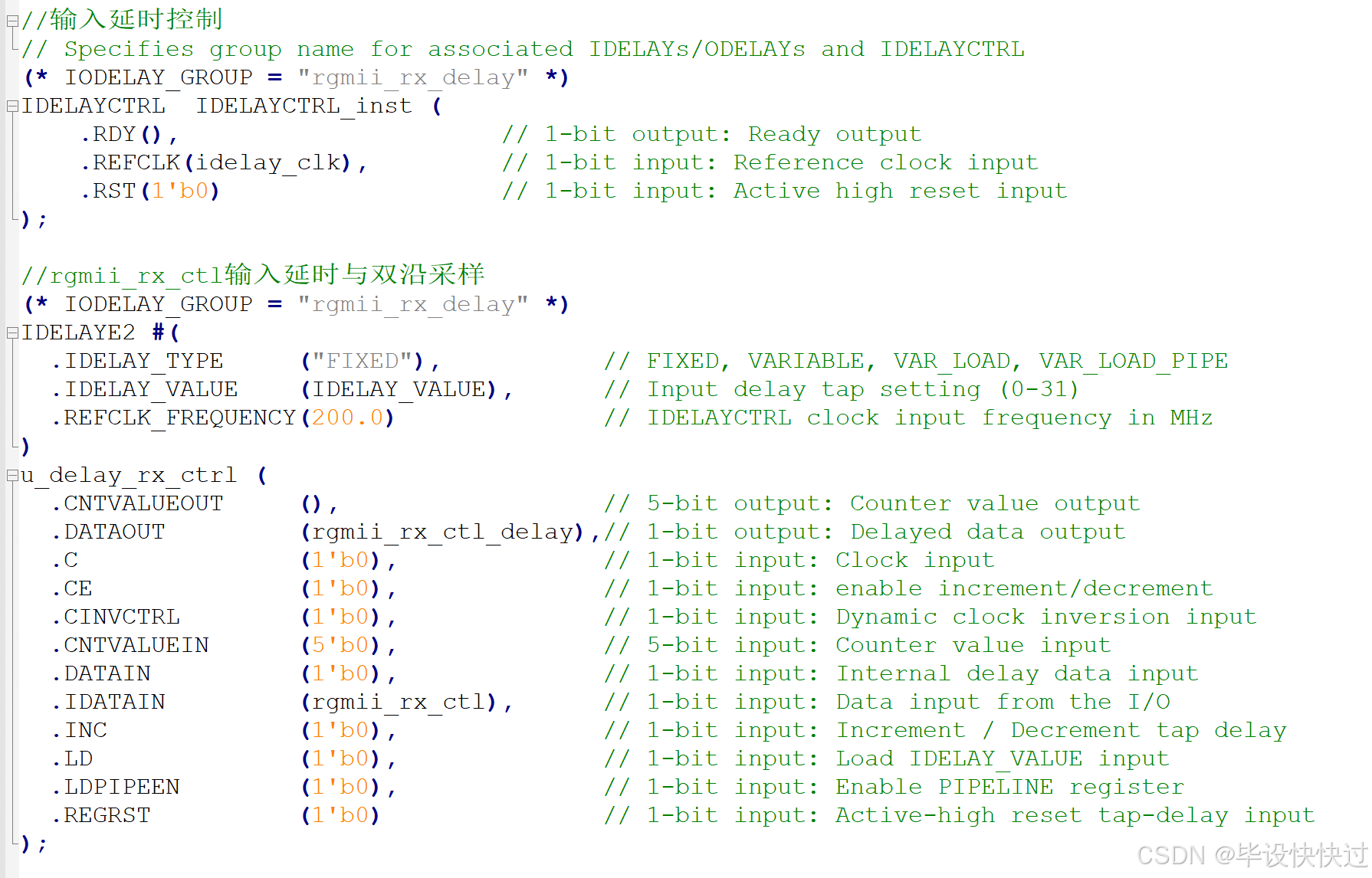

4.3.4IDELAYCTRL

IDELAYCTRL模块连续校准其区域内的各个IDELAY/ODELAY,以减少工艺、电压和温度变化的影响。IDELAYCTRL模块使用用户提供的REFCLK校准IDELAY和ODELAY。

IDELAYCTRL 原语如下:

五.实验任务

本节实验任务是使用领航者 ZYNQ 开发板上的 PL 端以太网接口,和上位机实现 ARP 请求和应答的功能。当上位机发送 ARP 请求时,开发板返回 ARP 应答数据。当按下开发板的触摸按键时,开发板发送 ARP请求,此时上位机返回应答数据。六.模块代码解析

6.1整体模块设计

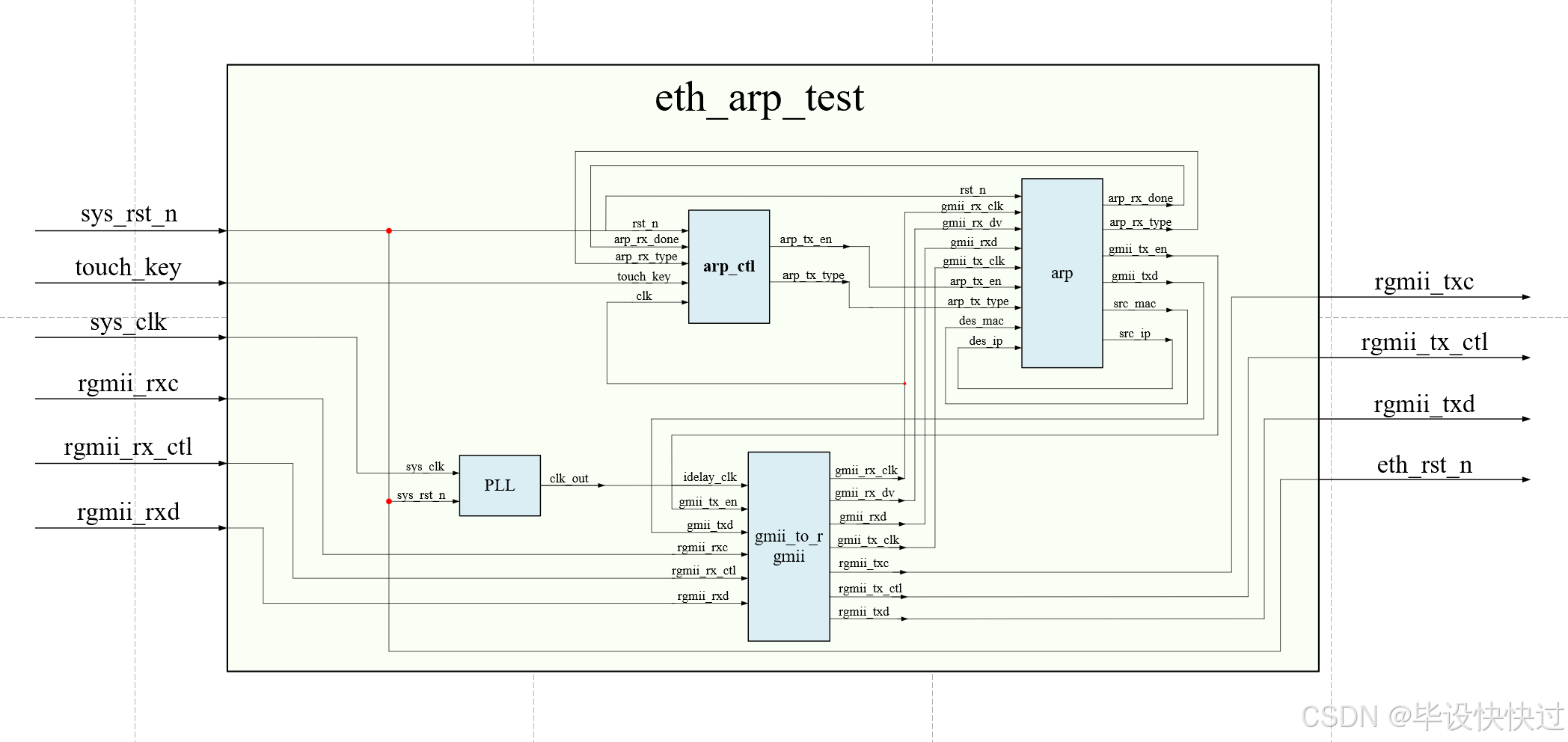

PLL模块:该模块对系统时钟进行倍频,输出 200Mhz 的时钟,用于 IDELAYCTRL 原语的参考时钟 。

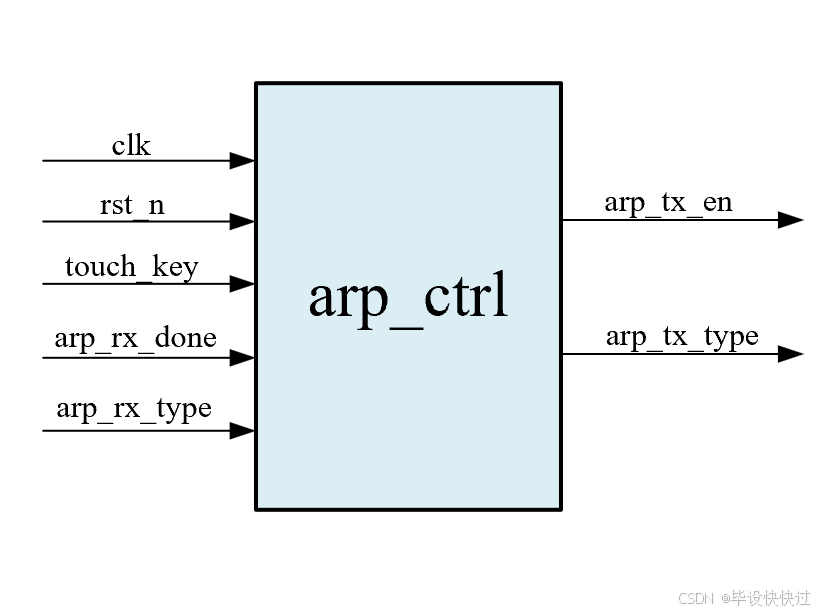

arp_ctrl模块:该模块负责检测输入的触摸按键是否被按下,从而判断出arp的类型是arp请求还是arp应答,进而控制 ARP 顶层模块发起请求与产生应答等操作。

gmii_to_rgmii模块:因为FPGA不能处理双沿信号,因此需要进行双沿(DDR)数据和单沿(SDR)数据之间的转换。

arp顶层模块:该模块实现了以太网 ARP 数据包的接收、发送以及 CRC 校验的功能。

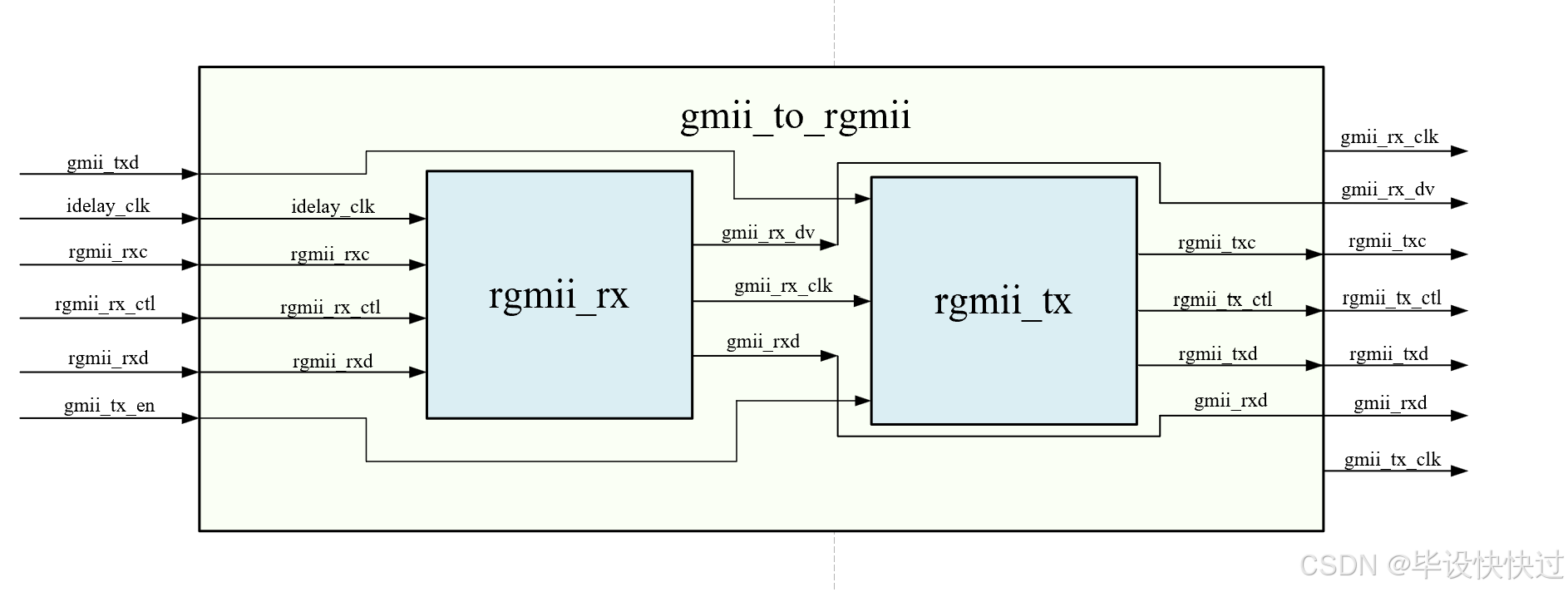

6.2gmii_to_rgmii模块

6.2.1整体模块图

该模块实现了双沿(DDR)数据和单沿(SDR)数据之间的转换。

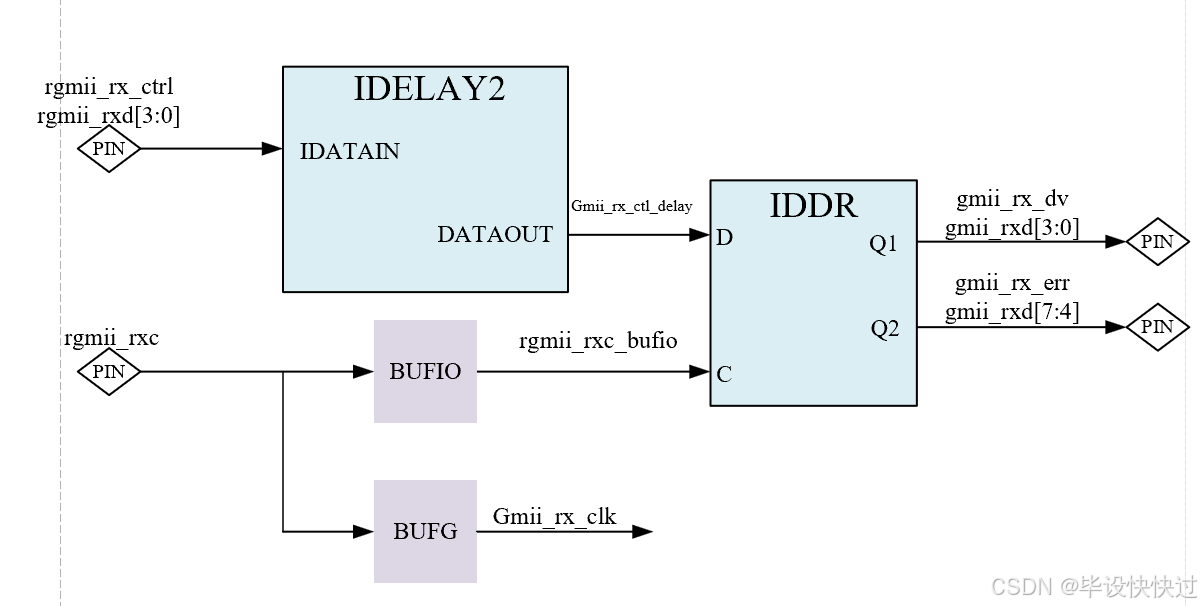

6.2.2rgmii_rx 模块

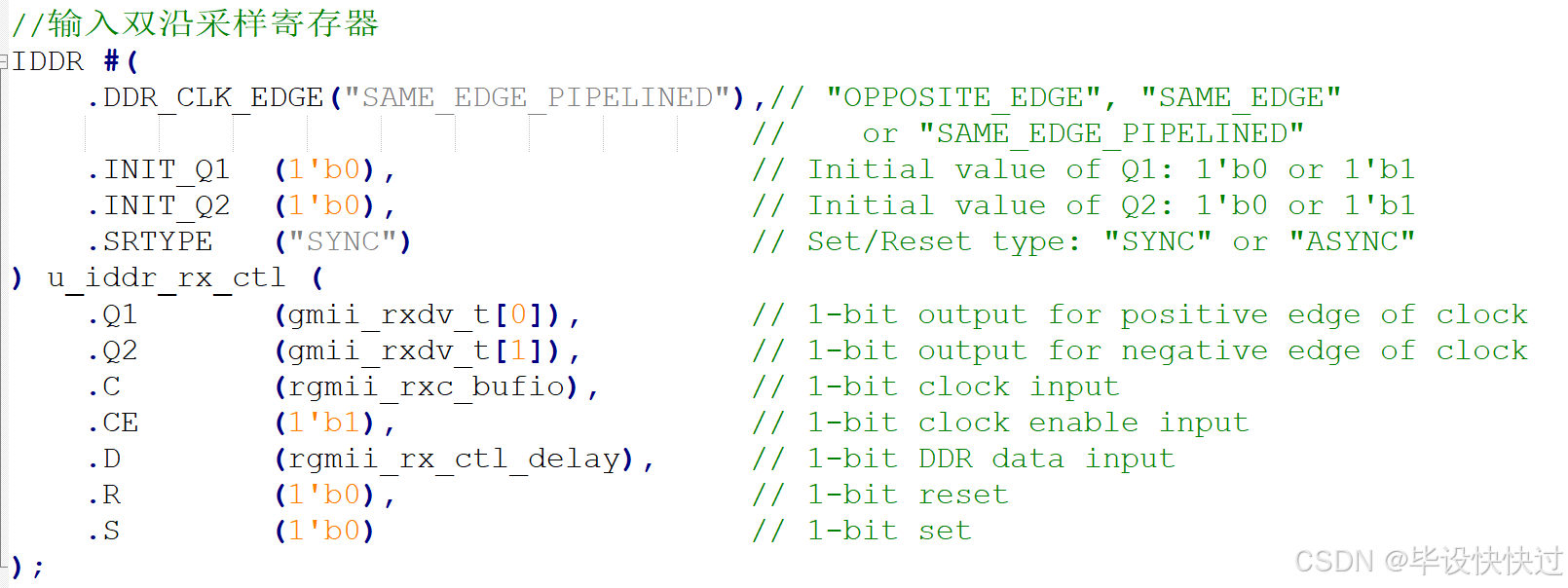

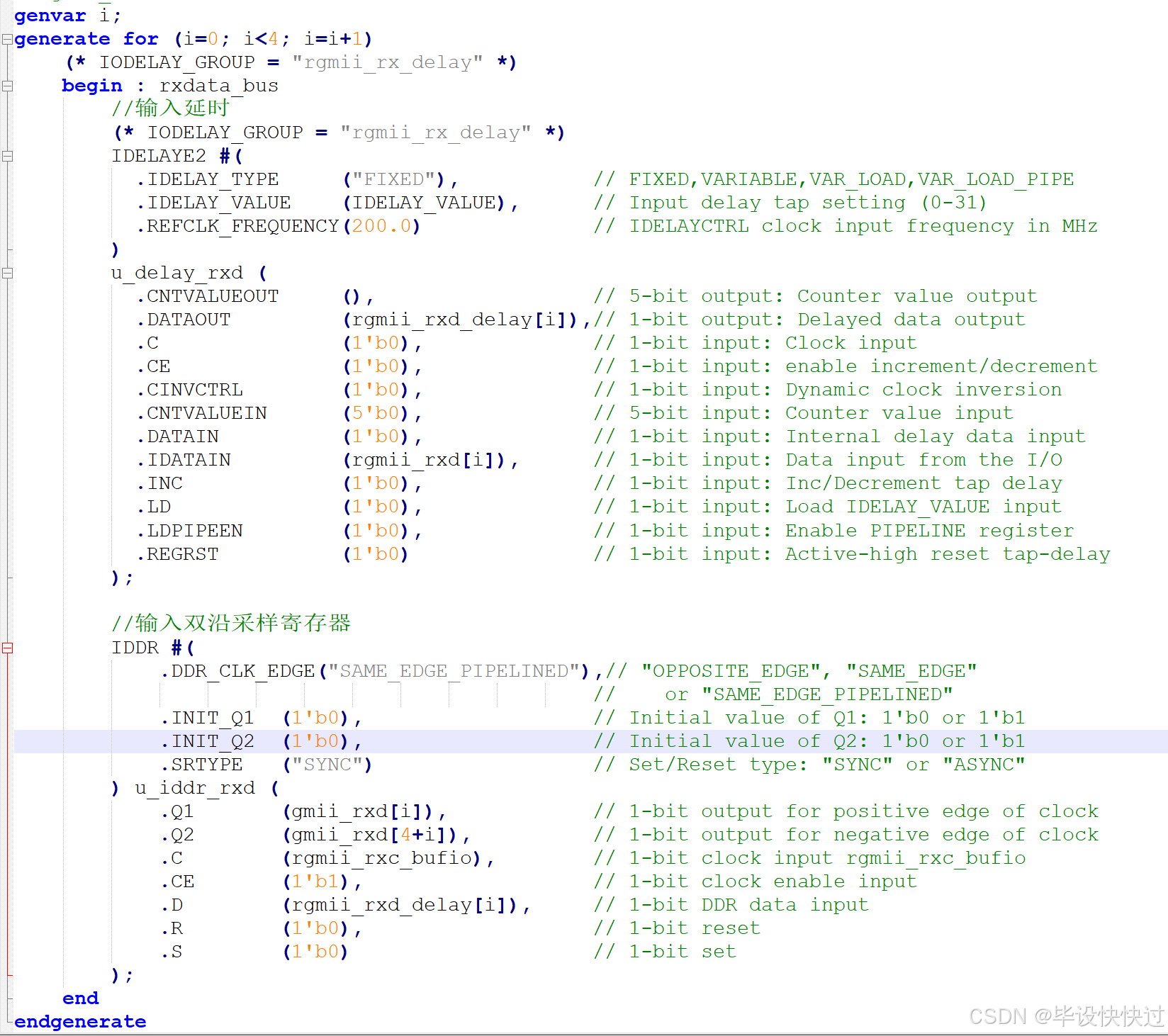

IDELAY2模块:rgmii_rx_ctl 控制信号和 4 位 rgmii_rxd 数据先经过 IDELAY2 进行延时,这里3.3节中提到过,进行数据延迟是为了保证采样数据的准确性 。IDELAY2 原语必须搭配 IDELAYCTRL 原语进行使用。

下面的idelay_clk就是PLL倍频输出的200MHZ时钟。

BUFIO模块:因为通过BUFIO连接产生的延迟比通过BUFG产生的延迟要小。

BUFG模块:时钟专用引脚输入的 rgmii_rxc 时钟经过 BUFG 后,得到 rgmii_rxc_bufg(gmii_rx_clk),该时钟为全局缓冲时钟,其到达 FPGA 内部的 IOB、CLB、块 RAM 的时钟延迟和抖动非常小,为其他模块提供操作时钟;

IDDR模块:IDDR 将双沿 1 位数据转换成单沿两位数据。

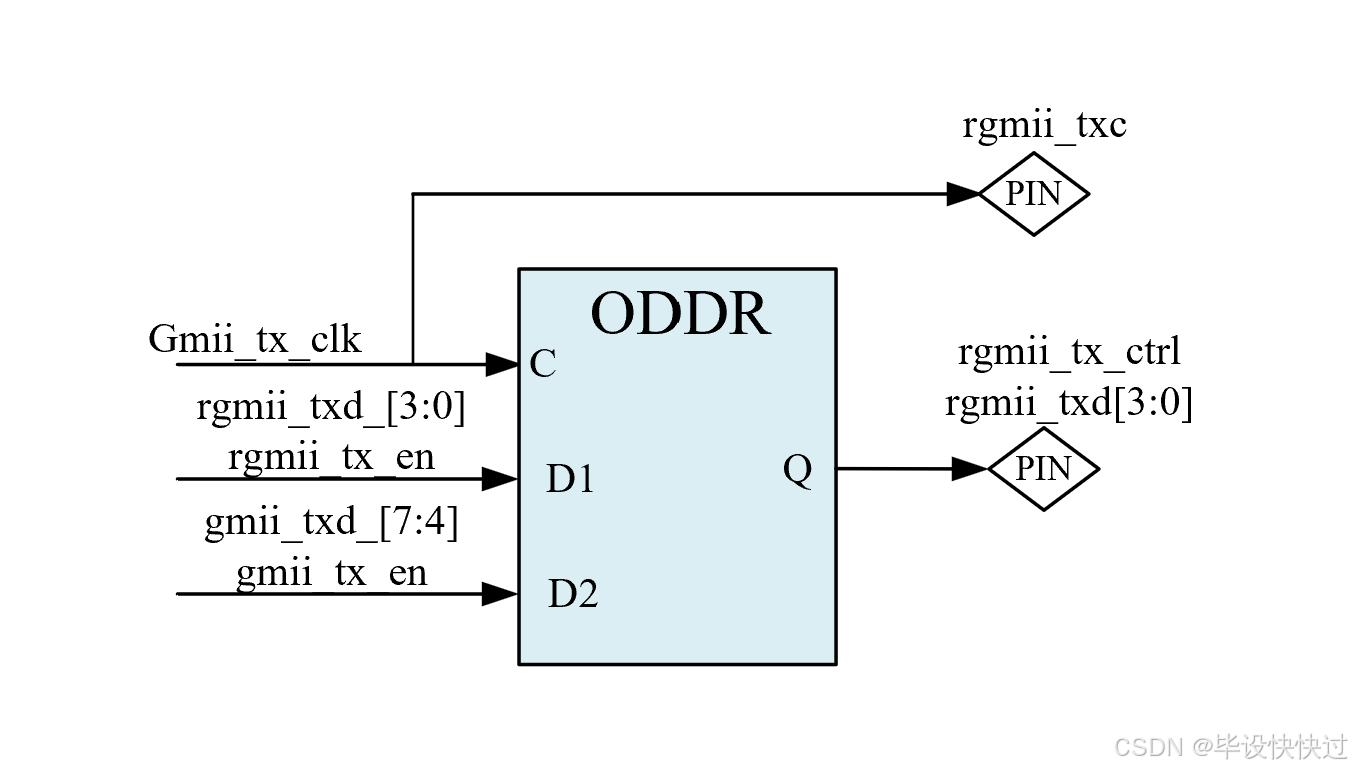

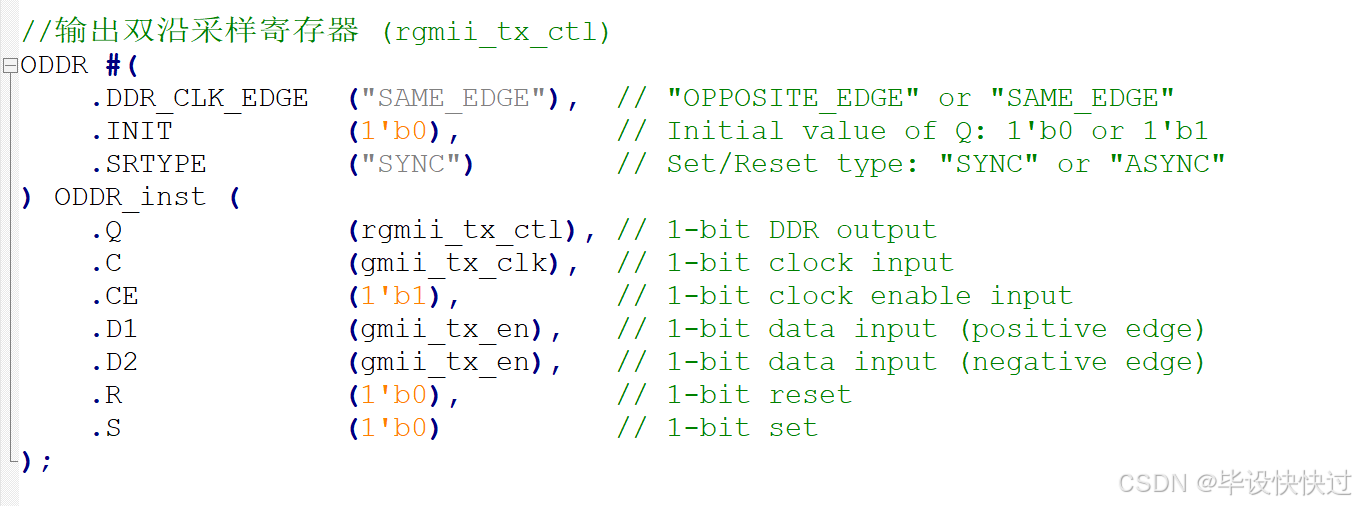

6.2.3rgmii_tx 模块

TX模块没有delay部分,因为由于 A7 系列没有 ODELAYE2 原语,所以这里直接接ODDR。

首先使用ODDR原语将单沿两位使能数据转换成双沿单位数据。

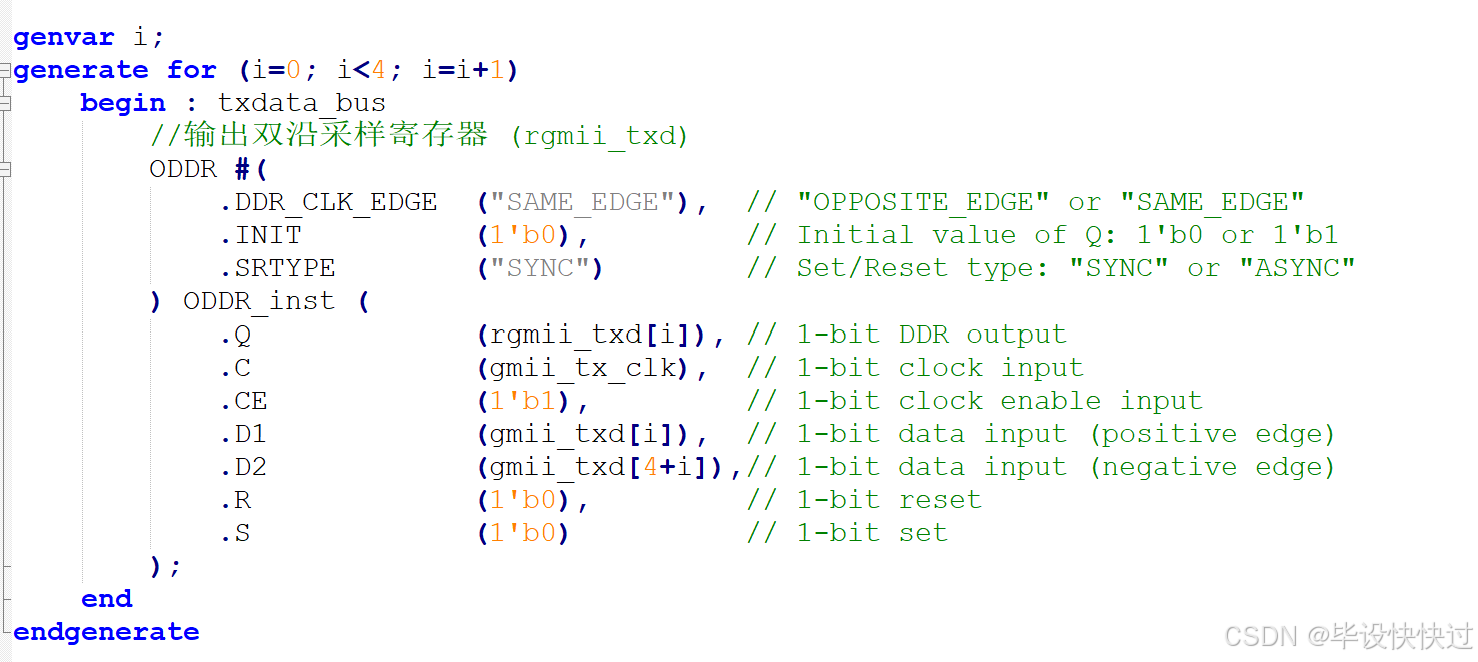

接着使用generate for 语句实现对 ODDR 的例化,由于输出的数据引脚为 4 位数据,因此这里共例化了 4 次。

接着使用generate for 语句实现对 ODDR 的例化,由于输出的数据引脚为 4 位数据,因此这里共例化了 4 次。

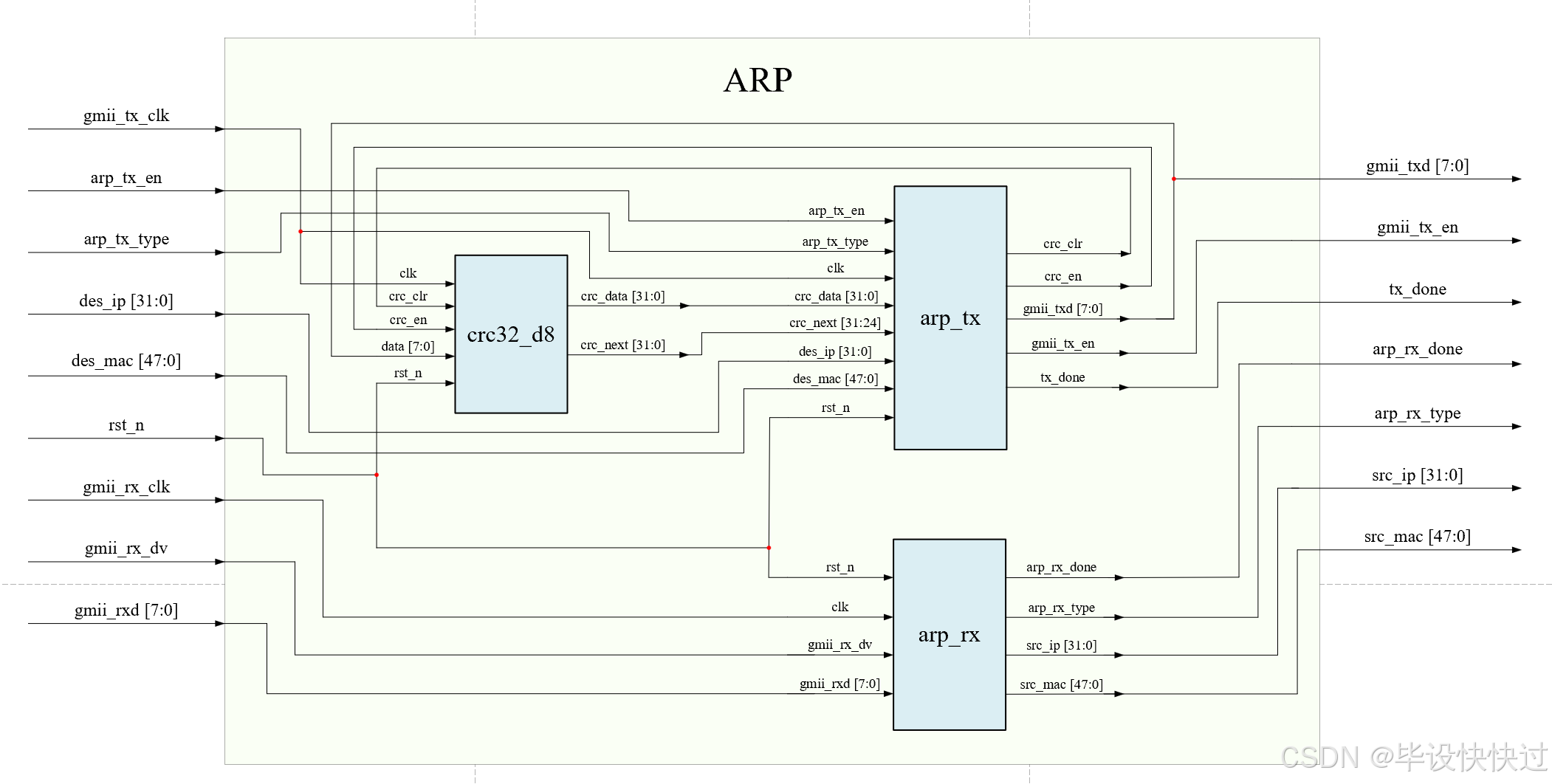

6.3arp模块

6.3arp模块

6.3.1整体模块图

crc32_d8模块:本次实验只对发送模块做校验,没有对接收模块做校验。这是由于我们可以直接通过解析出的数据来大致判断接收是否正确,而发送模块必须发送正确的校验数据,否则发送的数据直接被电脑的网卡丢弃,导致 ARP 请求或者应答失败。

arp_tx模块:ARP 发送模块根据以太网帧格式和 ARP 协议发送 ARP 请求或者 ARP 应答

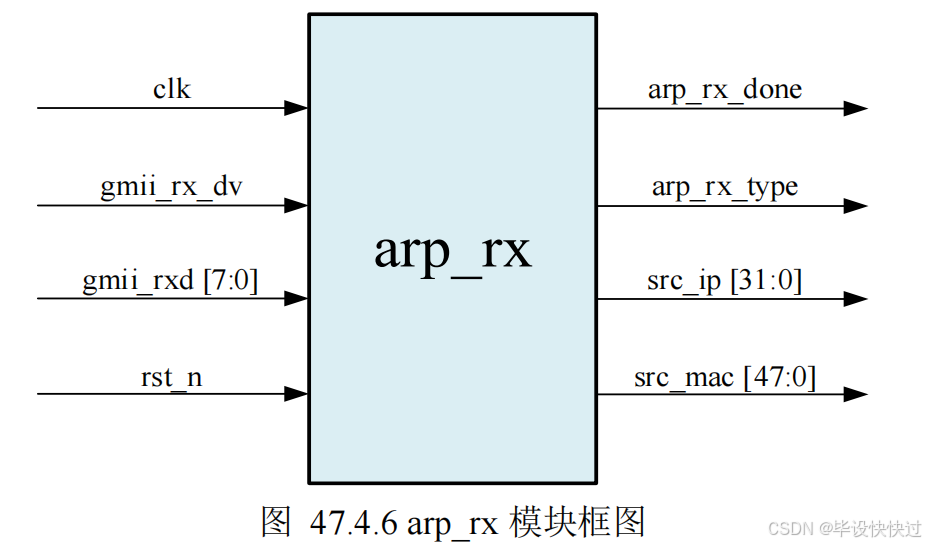

数据。 arp_rx模块:ARP 接收模块负责解析以太网的数据,判断目的 MAC 地址和目的 IP 地址 是否为开发板的地址,然后按照 ARP 协议将数据解析出来。6.3.2arp_rx 模块

clk:接收的rxc时钟信号;

rst_n: 复位信号,低电平有效

gmii_rxd_dv: GMII输入数据有效信号

gmii_rxd[7:0]: GMII输入数据

arp_rx_done: ARP接收完成信号

arp_rx_type: ARP接收类型 0:请求 1:应答

src_mac: 接收到的源MAC地址

src_ip: 接收到的源IP地址

该模块作用:第一:检查前导码、目的MAC、0806ARP协议、目的IP、ARP类型是否有误。

第二:从ARP报文中解析出源MAC和源IP(比如电脑发给开发板的ARP请求,开发板解析出电脑的MAC和IP),还有ARP一包报文接收完成信号,ARP类型。

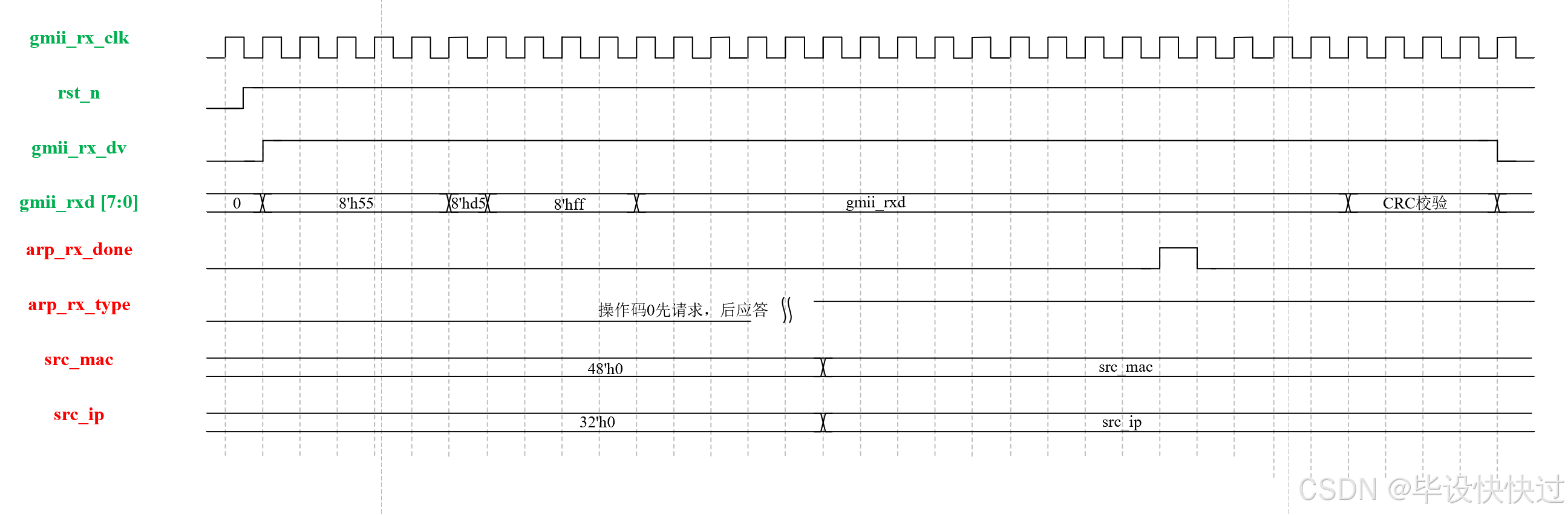

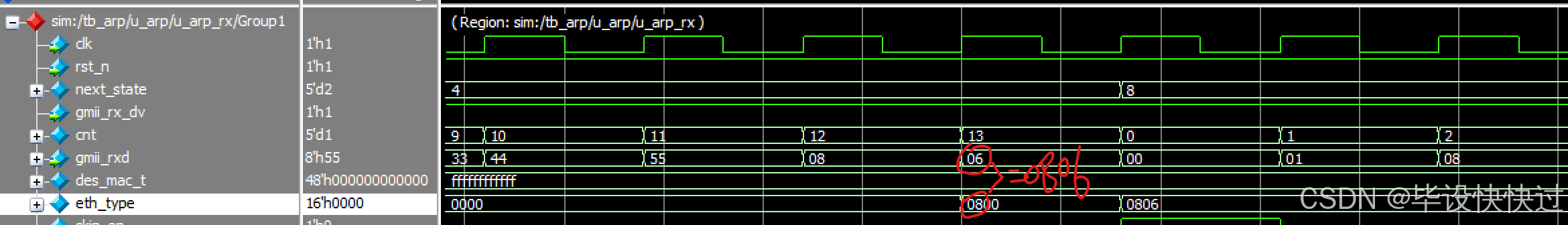

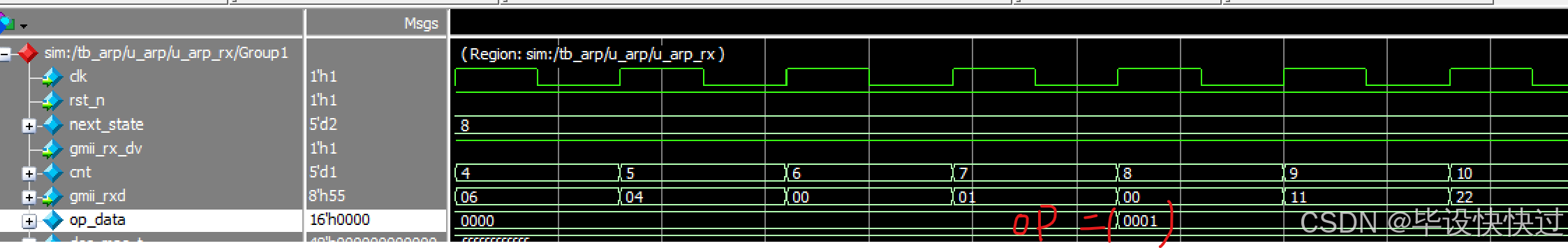

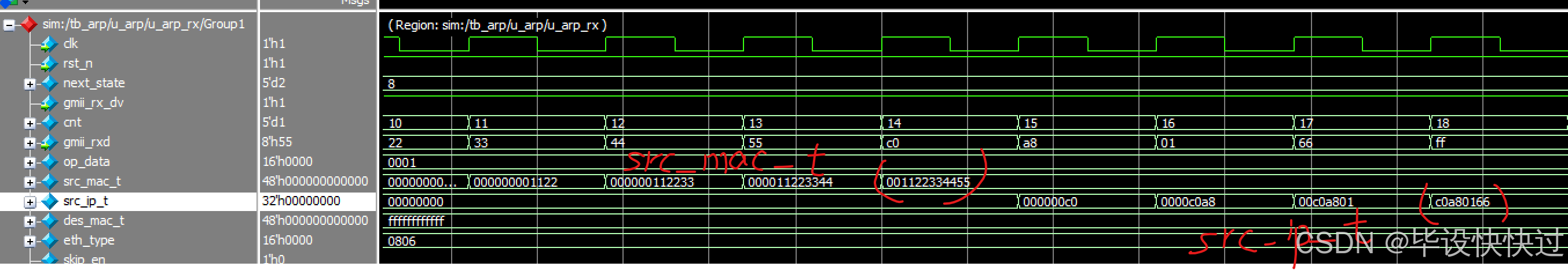

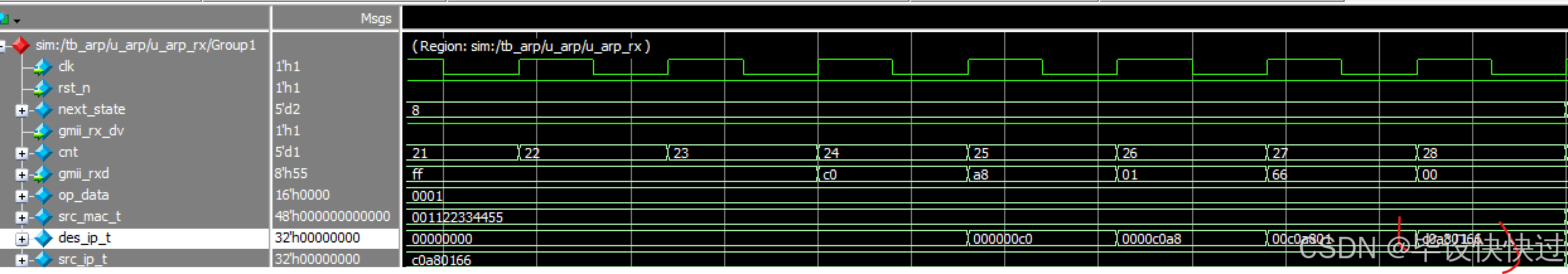

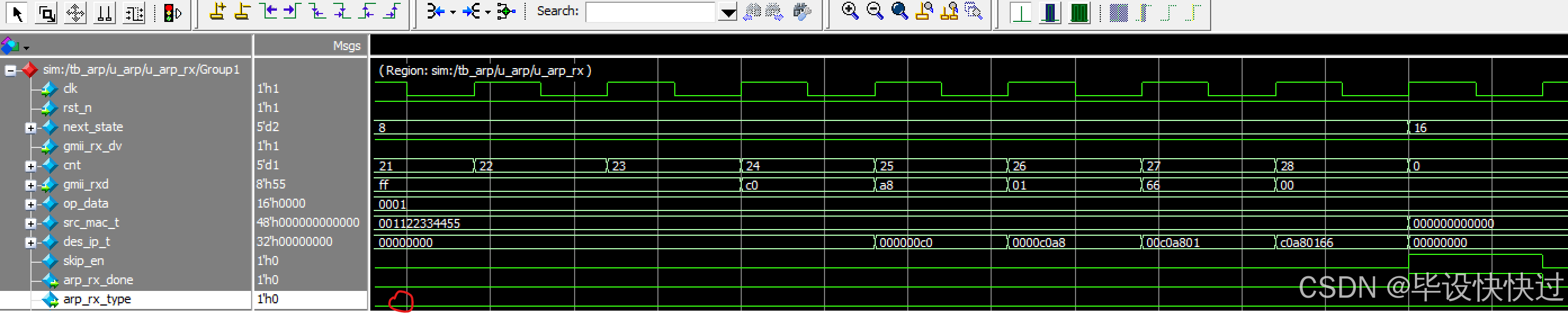

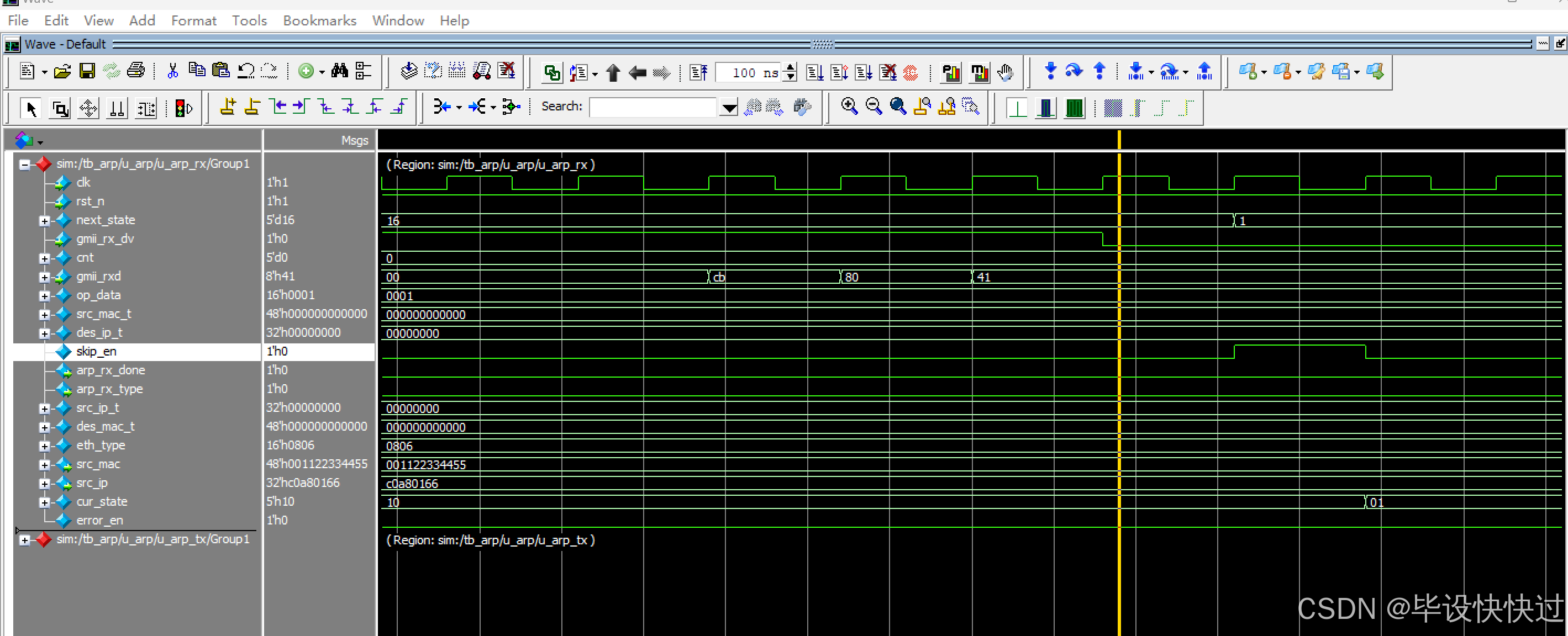

6.3.2.1波形图

gmii_rx_dv:当复位信号消失后,gmii_rx_dv开始拉高传入有效数据。gmii_rx_dv的持续长度就是一帧以太网数据,如上所示,从前导码开始,到CRC校验结束。

gmii_rxd[7:0]:传输的以太网数据包,依次是前导码,SFD,目的MAC地址,源MAC地址,长度/类型,数据,FCS。

arp_done:当发送完28byte的ARP数据之后,18byte填充数据之前,拉高arp_done,表示arp接收完成。

arp_rx_type:当接收28byte的arp数据时,接收到上图中的OP时,即可判断接收的arp种类,0代表请求,1代表应答。

src_mac:解析出的源mac地址。

src_ip:解析出来的源ip地址。

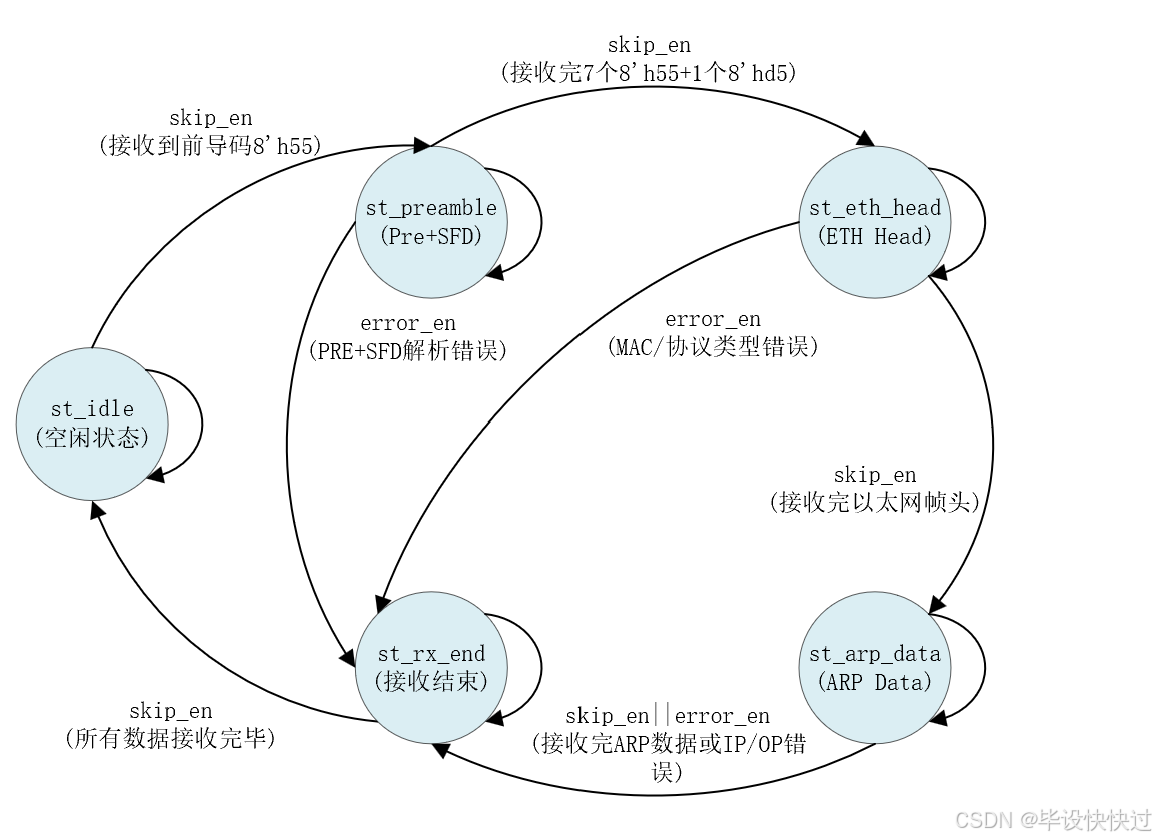

6.3.2.2状态转换图

解析arp数据包可以用以上状态机。

st_idle:表示当无arp请求或者arp应答数据传来,或者已经解析完毕时。当跳转使能skip_en来临,代表接收到第一个前导码8’h55。若是无跳转使能,则回到本状态。

st_preamble:表示正在接收前导码和SFD。当skip_en来临,代表前导码和SFD接收完毕。若接收码中有误,则跳转到st_rx_end。若没接收完,则回到本状态。

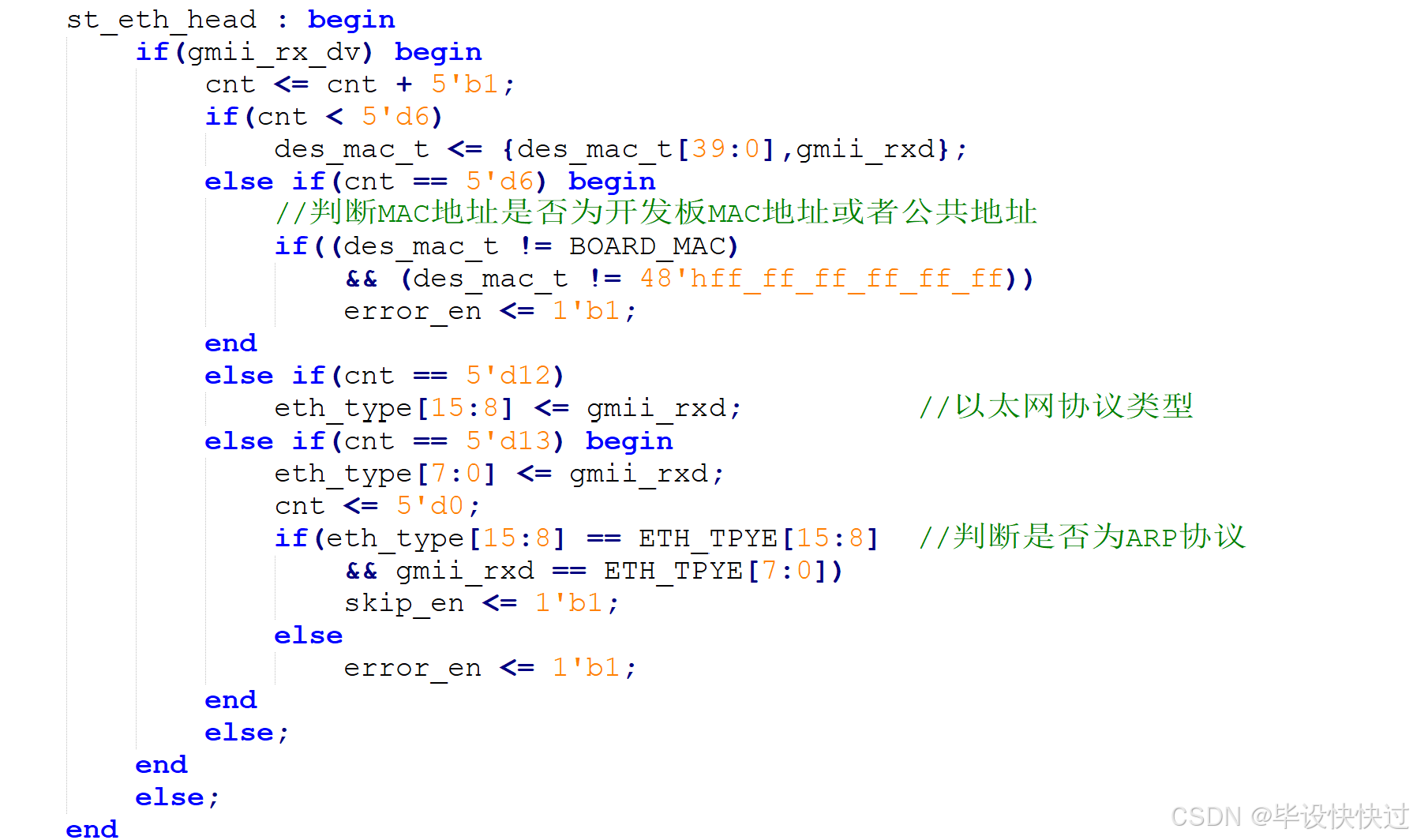

st_eth_head:表示正在接收以太网帧头(目的MAC地址,源MAC地址,长度/类型)。skip_en来临,表示准确无误接收完以太网帧头数据。接收错误则跳转到st_rx_end。未接收完,则回到本状态。

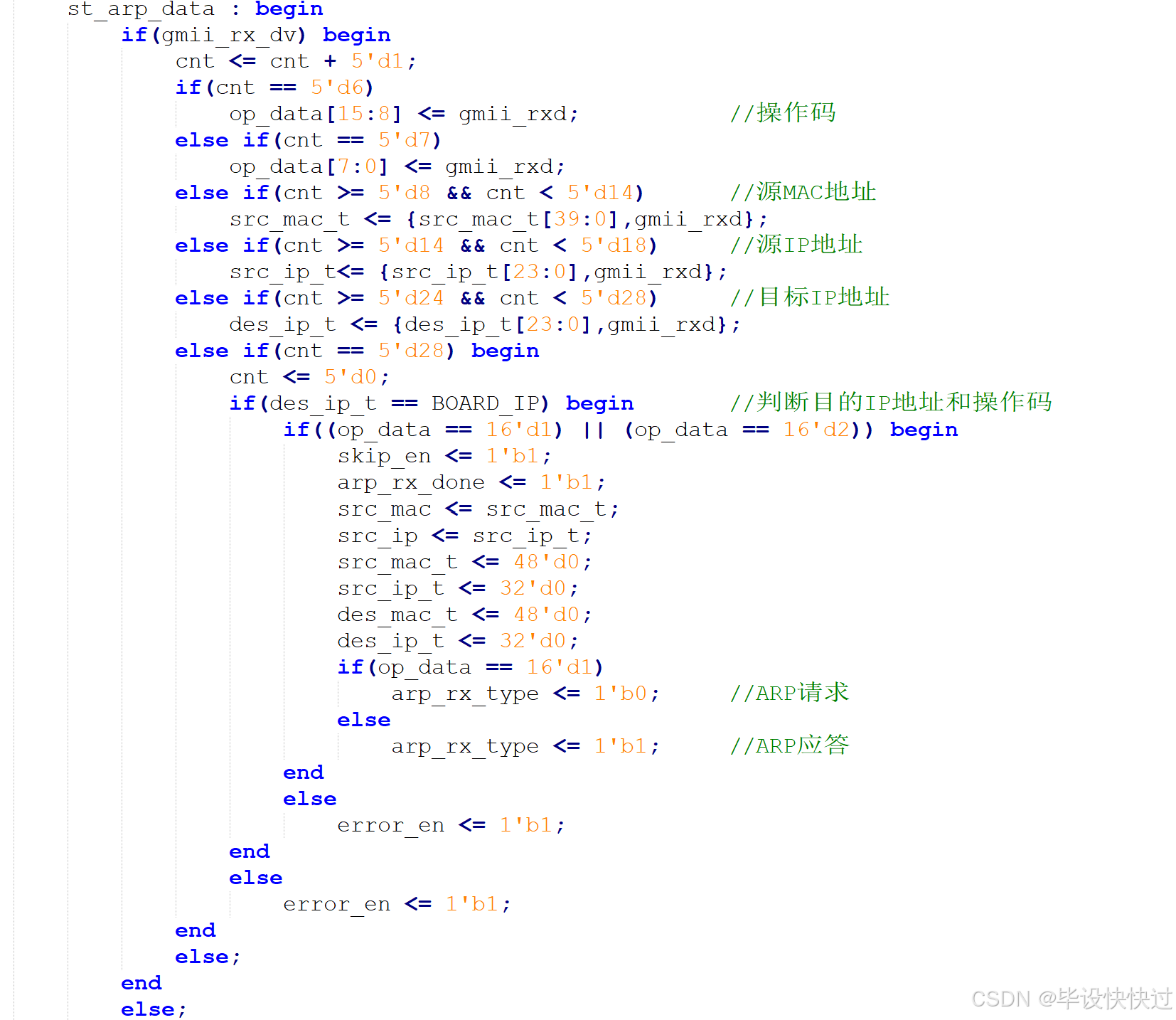

st_arp_data:表示正在接收arp应答/arp请求数据。skip_en表示准确无误接收完arp数据,error_en表示接收arp数据有误,都跳转到st_rx_end。若没接收完,则回到本状态。

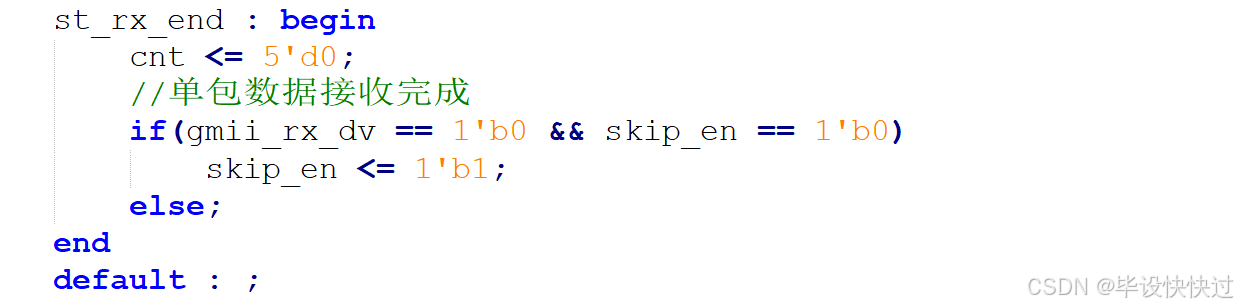

st_rx_end:只要接收以太网数据中有数据接收出错,立马终止接收,当所有数据准确无误接收后跳转回st_idle状态。

6.3.2.3代码解析

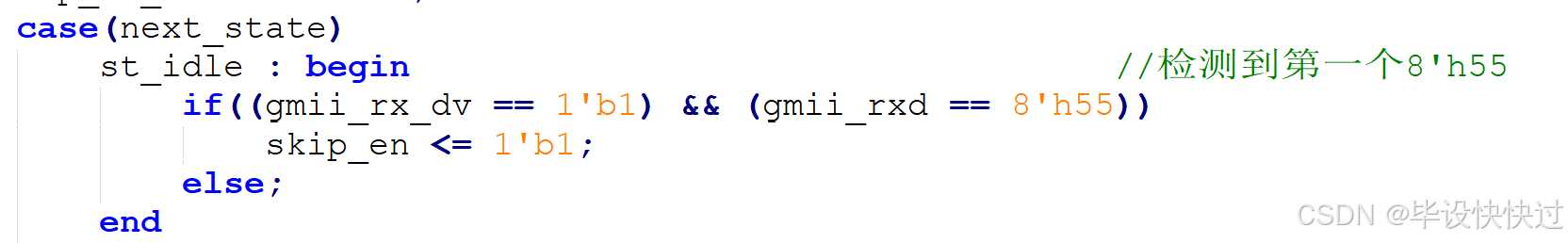

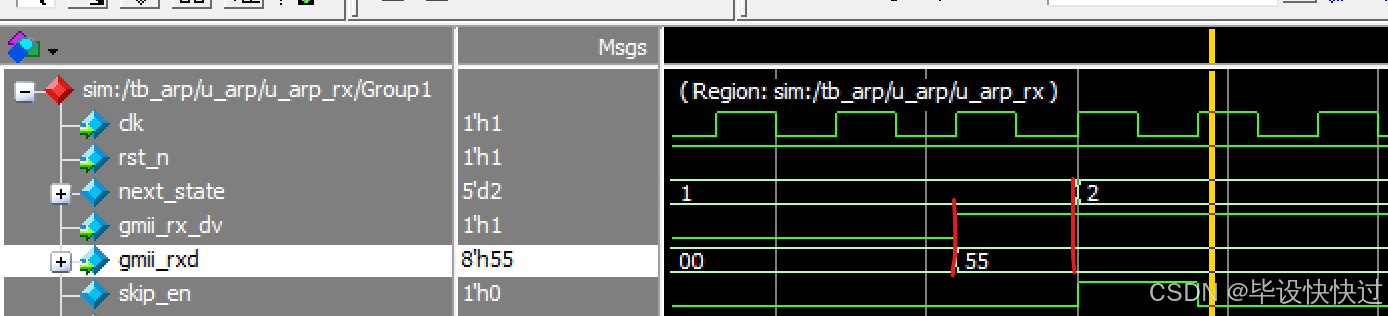

空闲状态时,只要GMII输入数据有效信号gmii_rx_dv来临并且第一个前导码传来,立即跳转至下一状态。

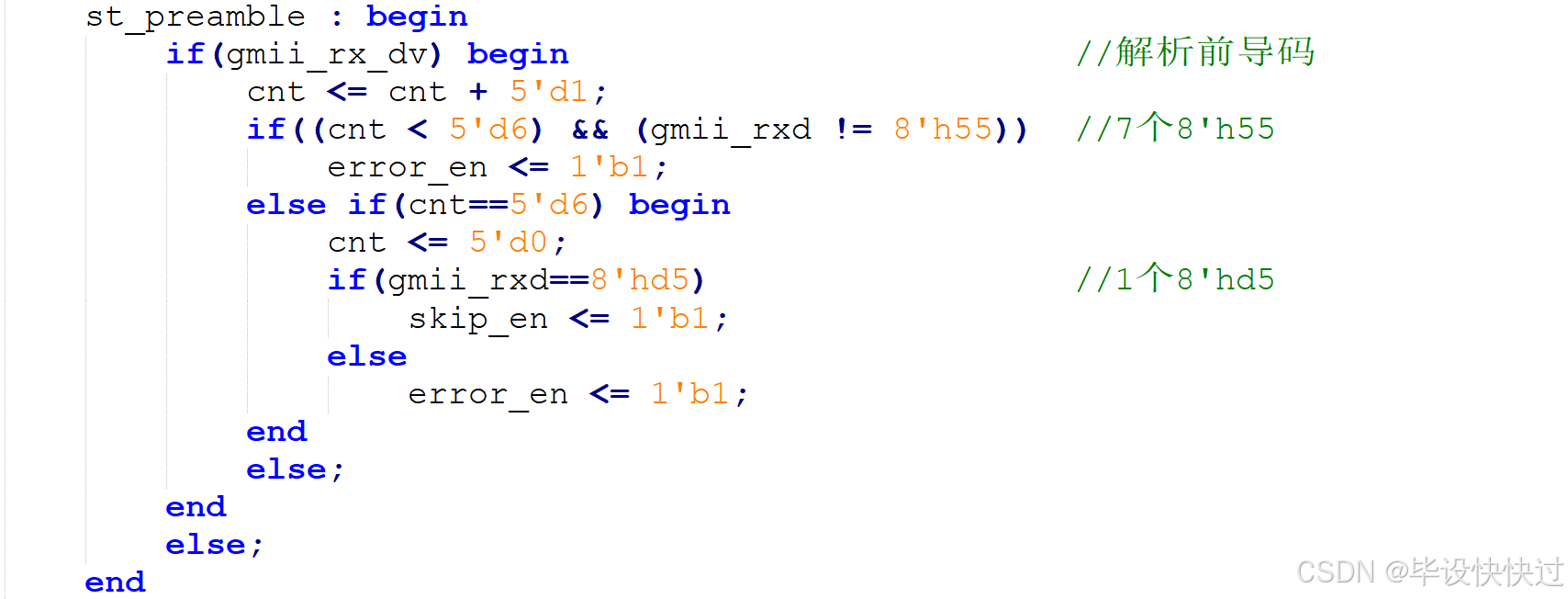

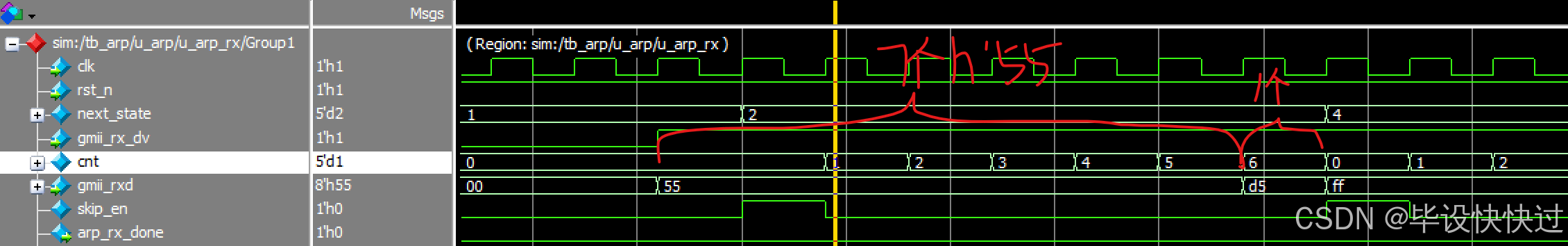

接收前导码状态时,因为前导码是7个8'h55,而空闲状态时已经检测出一个8'h55,因此这里只要检测6个就行。故只要这6个前导码中有一个不是8'h55就代表前导码错误,终止接收。

若7个前导码接收均准确,则继续检查SFD(8‘h05)是否准确,若准确,则跳转至下一状态;若错误,则终止接收。

接着接收以太网帧头,首先将6Byte的目的MAC地址寄存起来,然后判断该数据知否为开发板的MAC地址或者为广播地址,若都不是,终止接收,若是,则继续接收后面数据。

由于cnt=6~11时代表时源MAC地址,未知,故这里不操作。

当cnt=12~13时,暂存2Byte长度/类型数据,接着判断该以太网中的数据属于哪个上层协议,例如 0x0800 代表 IP 协议(网际协议)、0x0806 代表 ARP 协议(地址解析协议)等。这里是判断是否为ARP协议(ETH_TYPE=0806)。若是,则继续接收后面数据,若不是,则终止接收。

接着到接收28Byte ARP数据。 这里硬件类型、协议类型、硬件地址长度、协议地址长度无需判断其是否有误。

cnt=6~7时,接收OP数据,这里将OP数据暂存起来。

cnt=8~13时,接收源MAC地址,这里将MAC数据暂存起来。

cnt=14~17时,接收源IP地址,这里将IP数据暂存起来。

cnt=18~23时,因为目的MAC地址未知,因此这里不操作。

cnt=24~27时,接收目的IP地址,这里将IP数据暂存起来。

cnt=28时,表示arp所有数据接收完毕,接下来进行判断以上数据是否有误。首先判断目的IP是否正确,若正确,再判断是否是arp请求/应答信号,若是,则skip_en和arp_rx_done拉高,代表接收信号完成(为什么这里不判断接收信号中的MAC,IP地址是否正确就直接发送接收完成信号,因为可以在接收端数据进行人眼识别)。接下来将源mac地址和源ip地址解析出来,则根据操作码判断是arp信号种类。

GMII输入数据有效信号拉低,代表以太网数据接收完毕,则可以跳转至空闲状态。

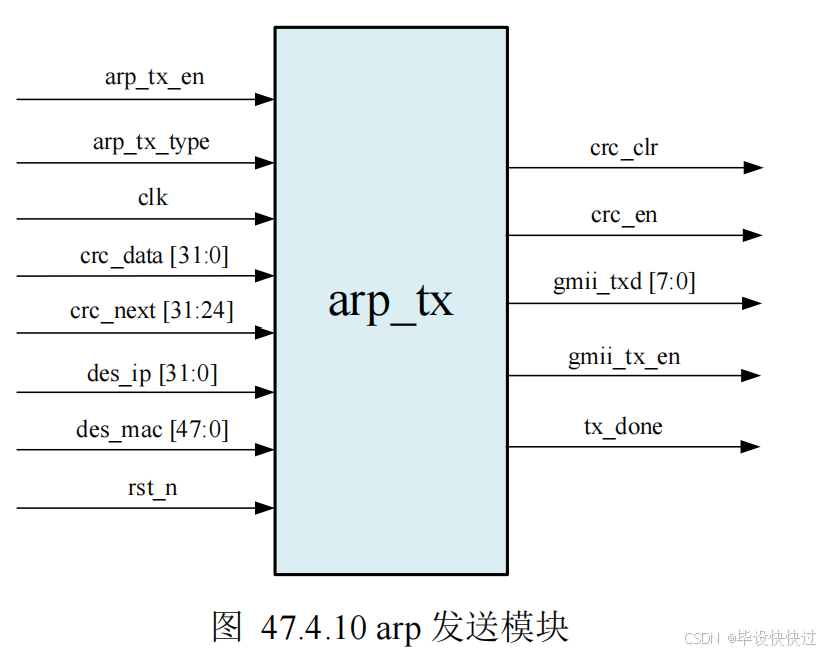

6.3.3arp_tx 模块

clk:rxc时钟信号。

rst_n:复位信号,低电平有效。

arp_tx_en:ARP发送使能信号。

arp_tx_type:ARP发送类型 0:请求 1:应答。

des_mac:发送的目标MAC地址。

des_ip:发送的目标IP地址。

crc_data:CRC校验数据。

crc_next:CRC下次校验完成数据.

tx_done:以太网发送完成信号

gmii_tx_en:GMII输出数据有效信号

gmii_txd:GMII输出数据

crc_en:CRC开始校验使能

crc_clr:CRC数据复位信号

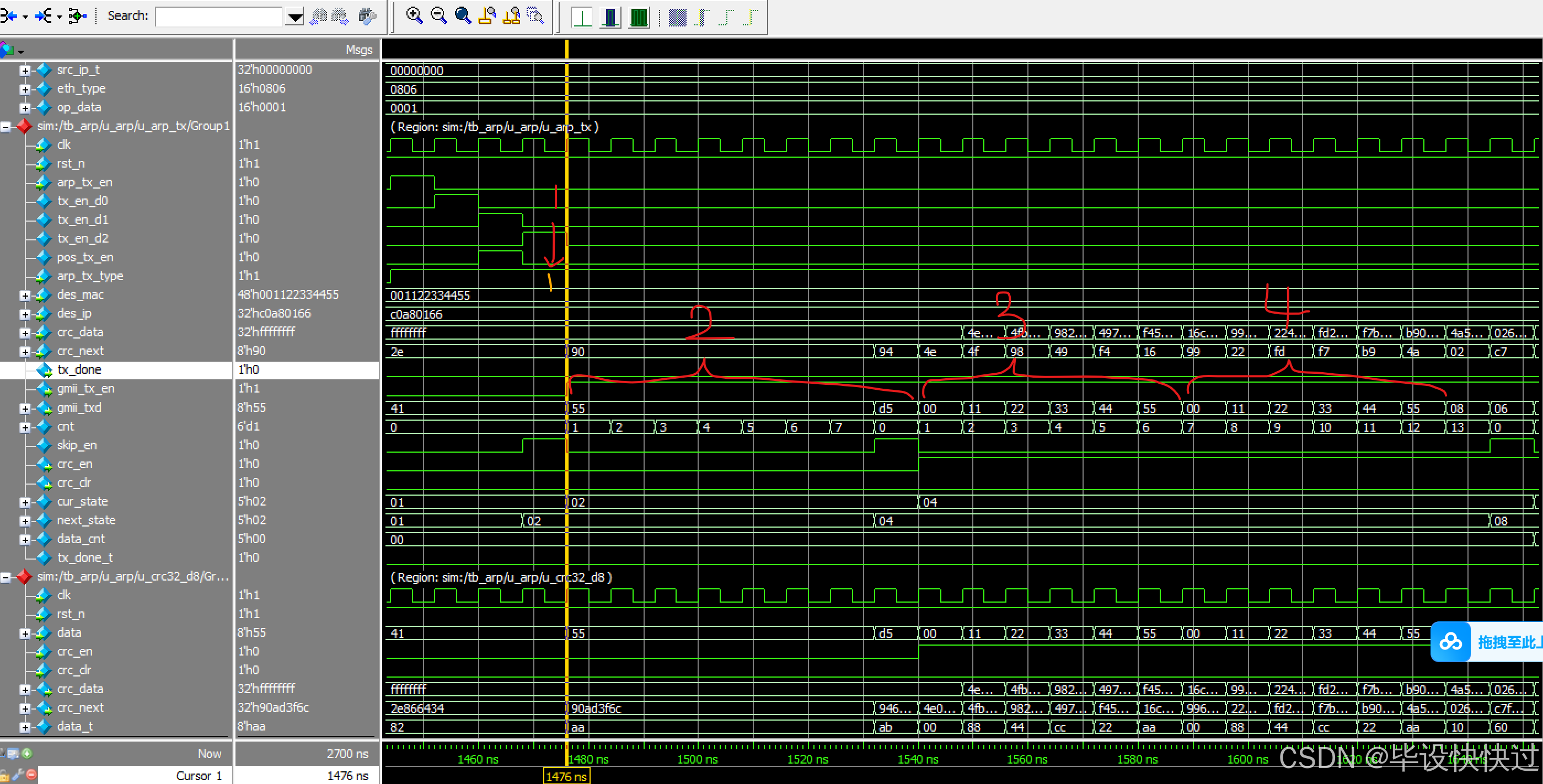

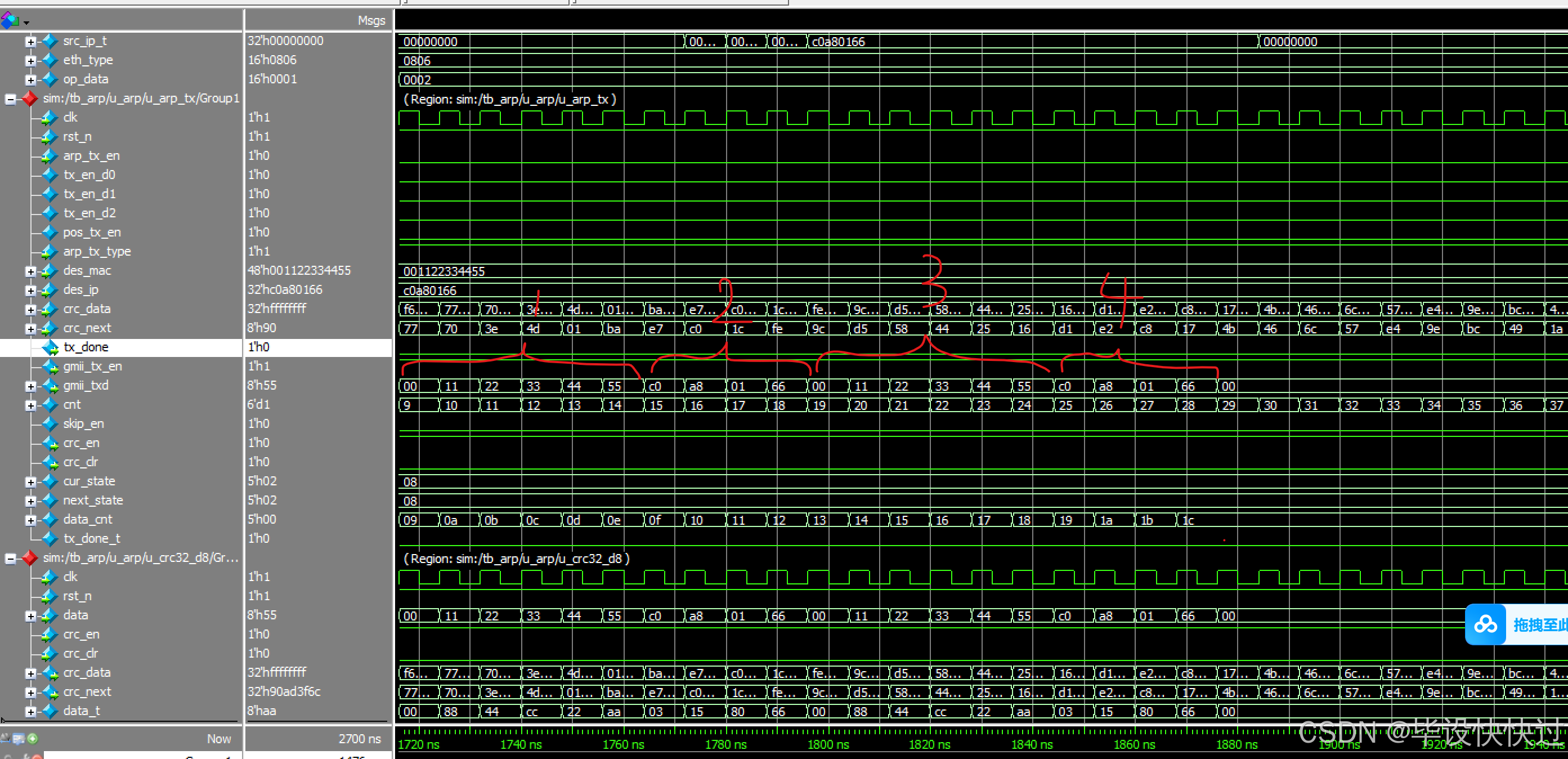

6.3.3.1波形图

arp_en:复位信号结束后,该信号拉高一个时钟周期,代表开始发送arp信号。

arp_tx_type:arp信号类型,0代表arp请求,1代表arp应答。

des_mac、des_ip:目标mac地址和目标ip地址。

crc_data:校验数据。

crc__next:下次校验完成数据。

gmii_tx_en:拉高代表GMII开始发送数据,拉低代表数据发送完成。

gmii_txd:代表GMII输出数据。

tx_done:代表一帧以太网数据发送完毕。

crc_en:如下图,在以太网帧头+以太网数据器件拉高,进行crc校验。

crc_clr:以太网数据发送完毕,crc清零。

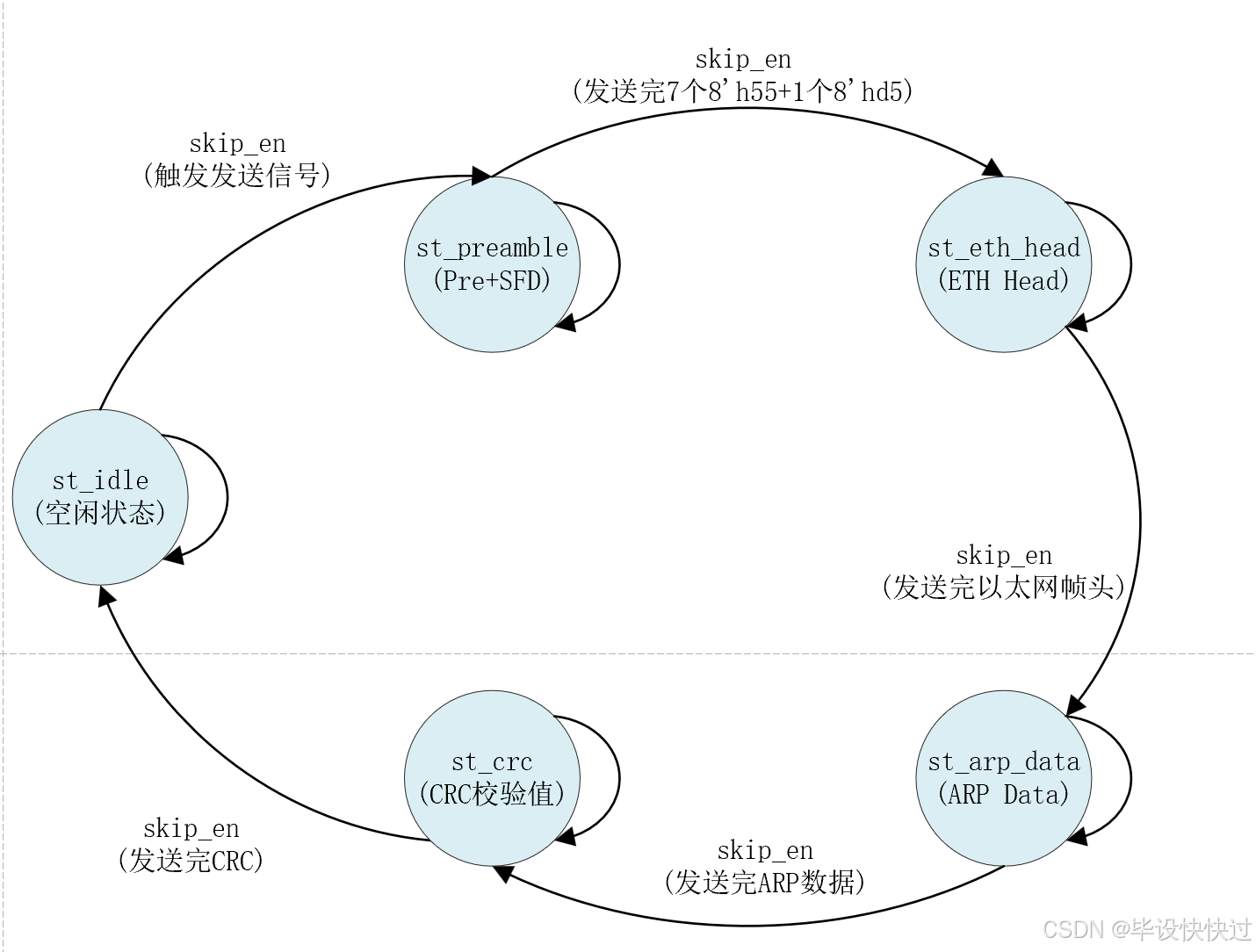

6.3.3.2状态转换图

st_ilde:不发送以太网信号或者已经发送完一帧以太网数据。

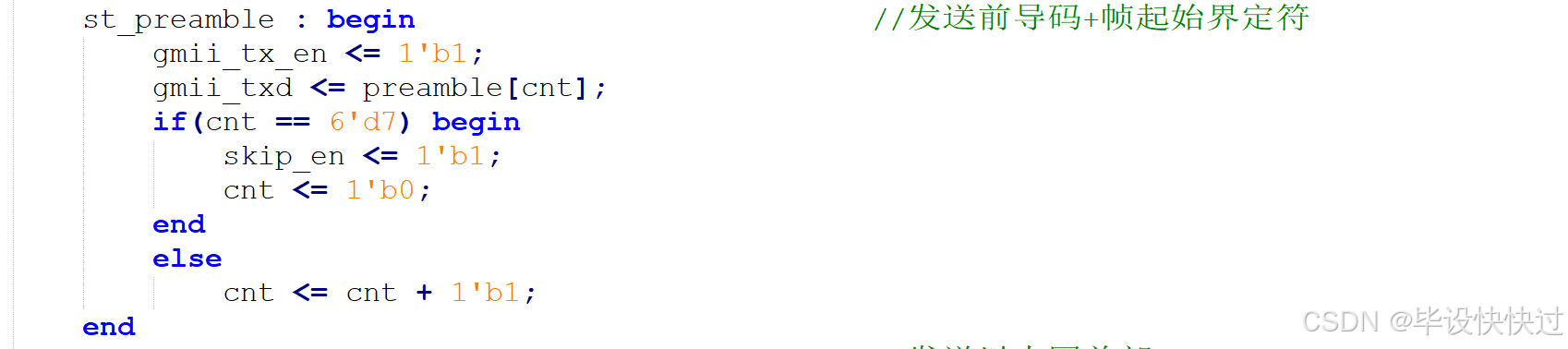

st_preamble:当skip_en来临,进入发送前导码和SFD状态。发送完进入发送以太网帧头 状态,未发送完回到本状态。

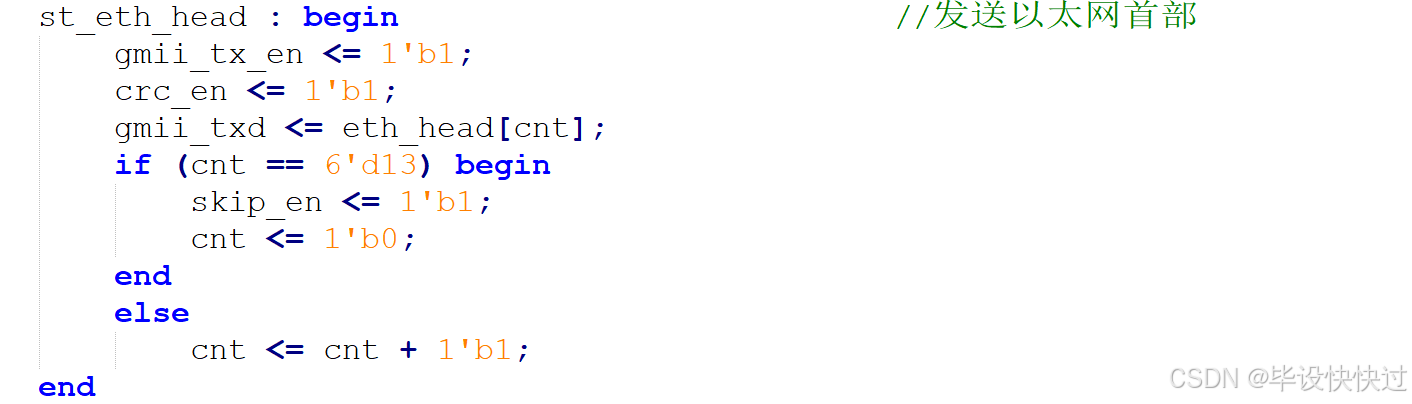

st_eth_head:当skip_en来临,进入发送以太网帧头数据状态。发送完进入发送arp数据状态,未发送完回到本状态。

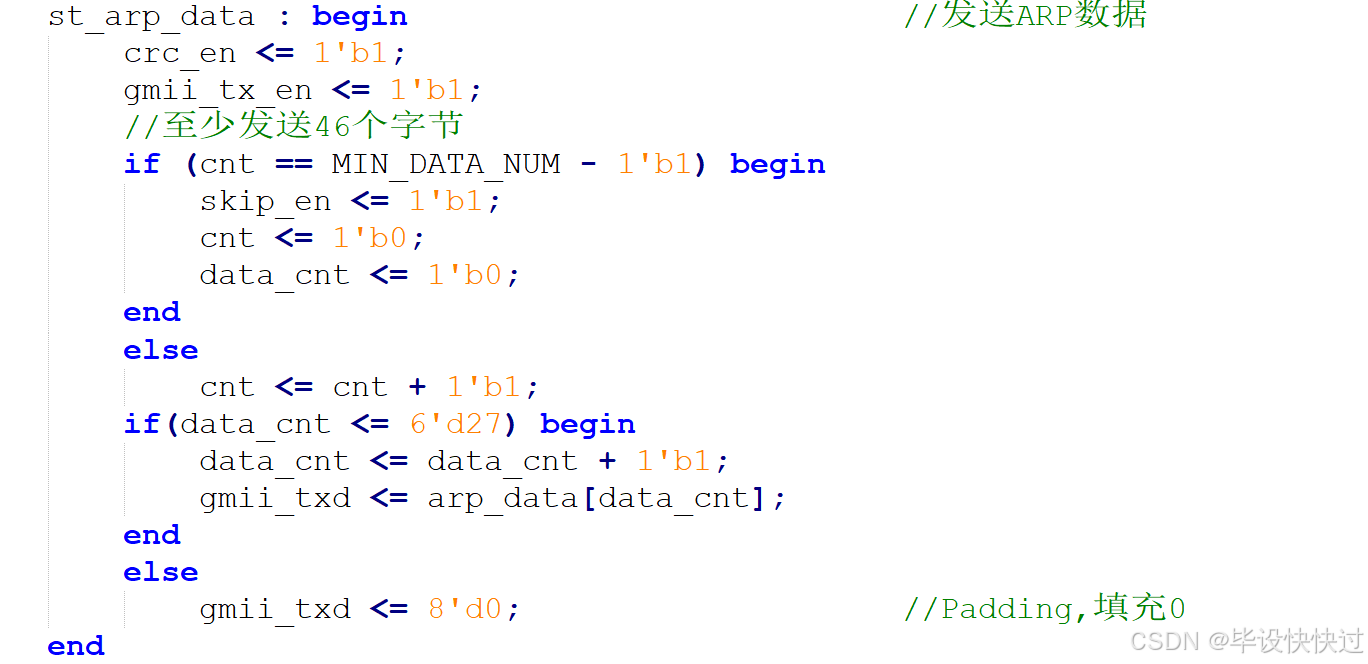

st_arp_data:当skip_en来临,进入发送arp数据状态。发送完进入发送crc数据状态,未发送完回到本状态。

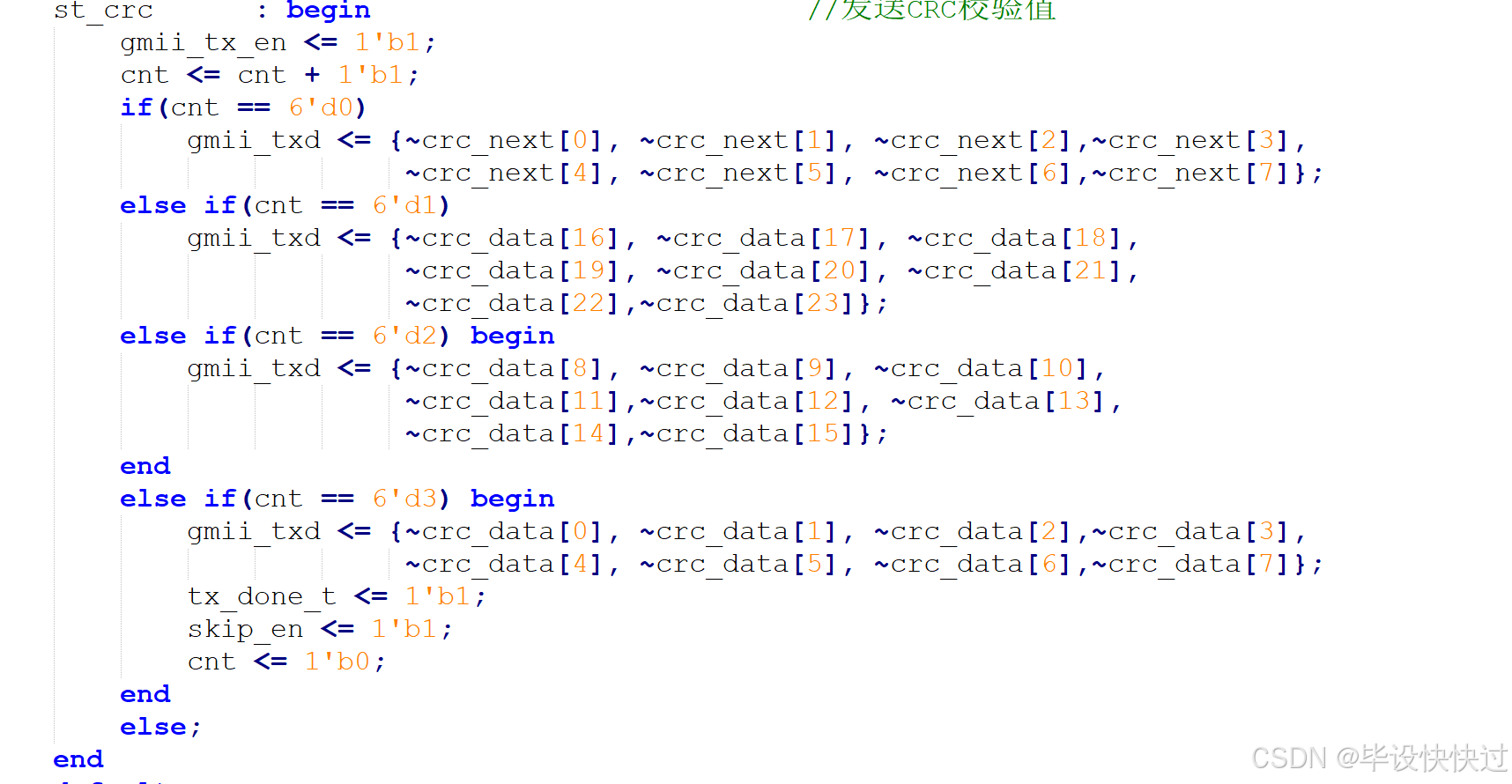

st_crc:当skip_en来临,表示数据全部发送完毕,进入空闲状态。未发送完回到本状态。

6.3.3.3代码解析

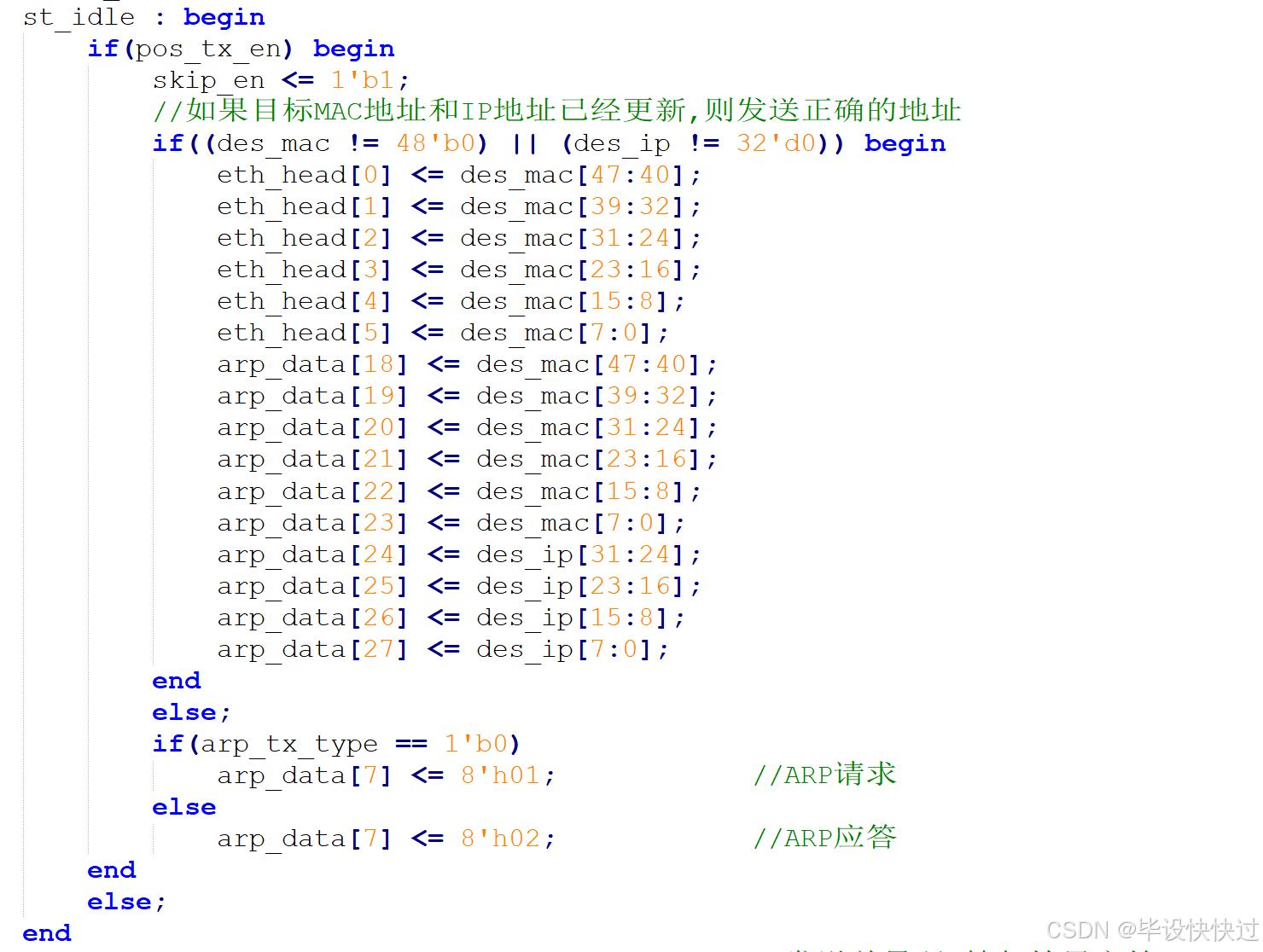

pos_tx_en:因为arp_tx_en是异步信号,这里要捕捉其上升沿,所以打两拍,得到arp_tx_en的上升沿信号未pos_tx_en。则该信号来临,代表可以发送一帧以太网数据。

因为dex_mac,des_ip是输入信号,故当这两个信号更新时,需要同时将数据更新到以太网数据中的eth_head处和arp数据中的arp_data处。

同时根据输入信号arp_tx_type判断arp中的OP值。

gmii_tx_en拉高,开始发送以太网数据。7个8’h55+1个8‘h05,一共8个数据。

gmii_tx_en拉高,开始发送以太网数据。7个8’h55+1个8‘h05,一共8个数据。

当发送到以太网帧头时,立马拉高crc_en,开始进行crc校验。6Byte目的MAC地址+6Byte源MAC地址+2Byte长度/类型,一共14Byte.

第一个if控制cnt累加,当发送完46个字节重新归零,进入下一状态。

第一个if控制cnt累加,当发送完46个字节重新归零,进入下一状态。

第二个if控制arp发送的数值,cnt<28,发送arp真实数据,剩余18个字节全填充为0.

发送crc校验值。

6.3.4arp_ctrl模块

该模块作用:当检测到触摸按键来临时,给出发送arp请求包信号,此时arp_en=1,arp_tx_type=0;

当检测到arp包接收完成并且接收的是arp请求是, 给出发送arp应答包信号,此时arp_en=1.arp_tx_type=1。

七.modelsim仿真验证

7.1arp_tx仿真

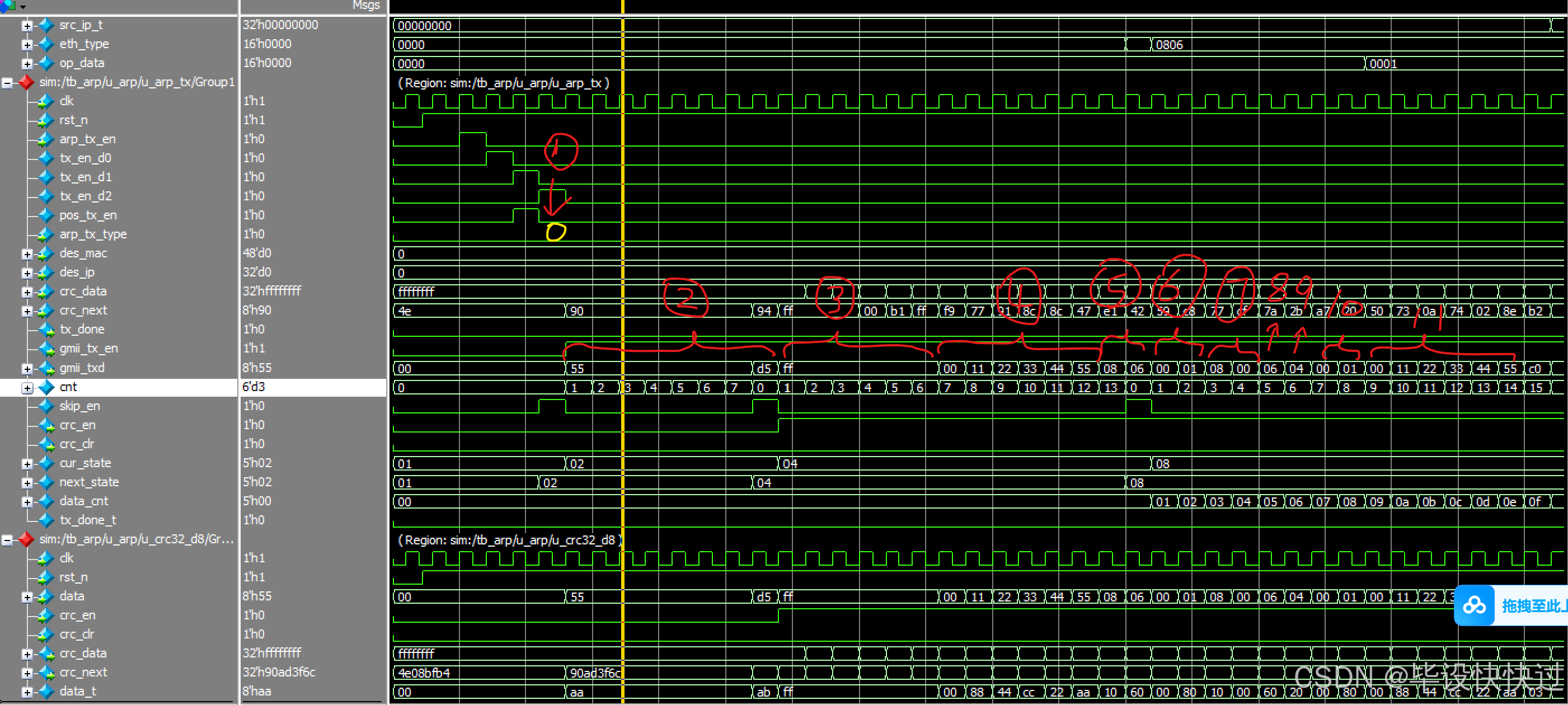

7.1.1arp请求发送

1:当arp_tx_en拉高,检测到该信号上升沿时, 输入信号des_mac和des_ip无变化,还保持默认值0 。与此同时检测arp类型,1处为0,故为arp请求信号。

2:发送7Byte前导码和1ByteSFD。

3:发送目的MAC地址。这里为ff,因为是板子向PC发送arp请求,所以板子是源(源MAC和源IP已知),PC是目的(目的IP已知,目的MAC未知)。在目的MAC未知的情况下采用广播形式。

4:发送源MAC地址001122334455。

5:因为是发送arp协议,故为0806.

6:硬件地址的类型,1 表示以太网地址。

7:ARP 协议的上层协议为 IP 协议,因此该协议类型为 IP 协议,其值为 0x0800。

8:硬件地址长度6.

9:IP地址长度4.

10:1 表示 ARP 请求,2 表示 ARP应答。这里是arp请求故为0001.

11:源MAC地址001122334455.

1:源IP地址192_168_001_102.

2:目的MAC地址未知,为广播形式。

3:目的IP地址192_168_001_102.

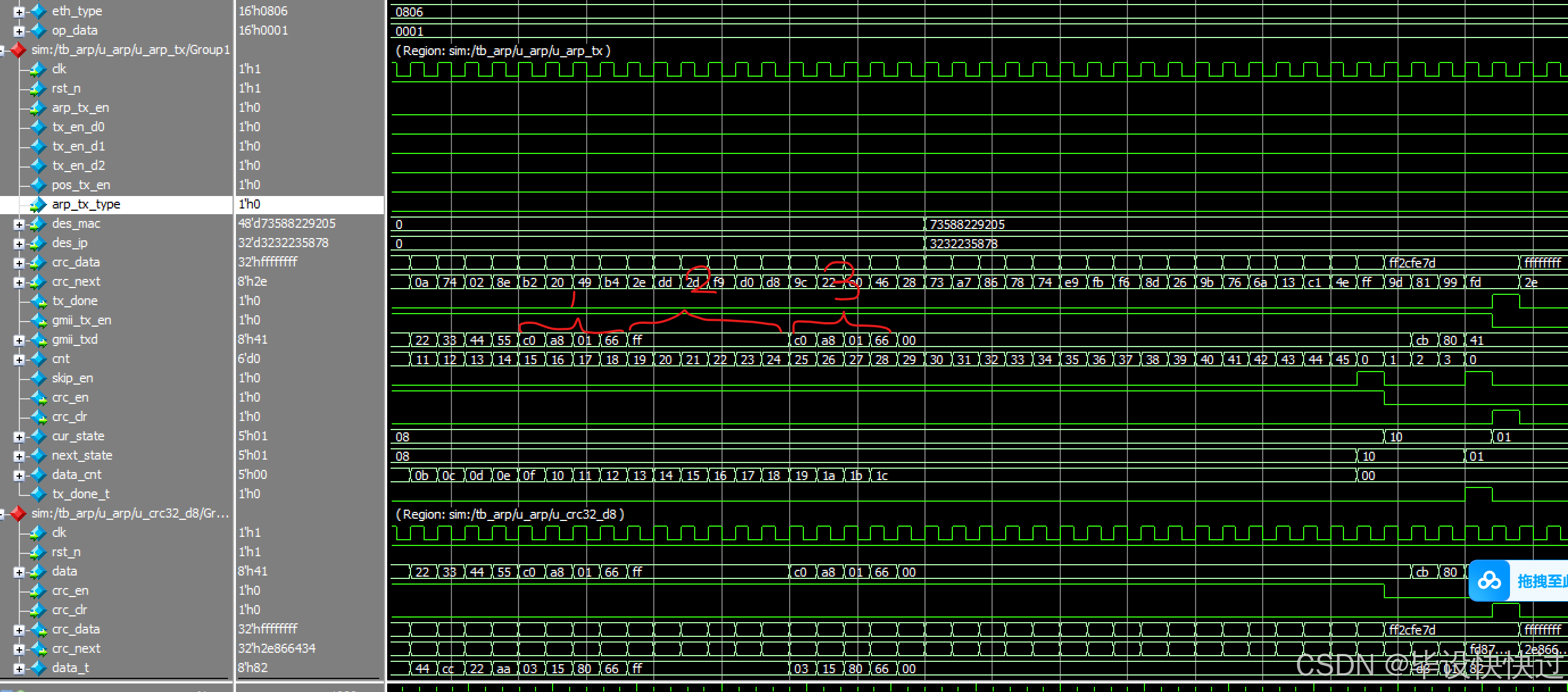

7.1.2arp应答发送

1:arp_tx_type为1,为arp应答信号。

2:发送前导码+SFD。

3:目的MAC地址,因为des_mac数值已经更新为001122334455,故此处已知目的MAC地址也为001122334455.

4:源MAC地址,也是开发板的MAC地址001122334455.

1:源MAC地址

2:源IP地址

3:目的MAC地址

4:目的IP地址。

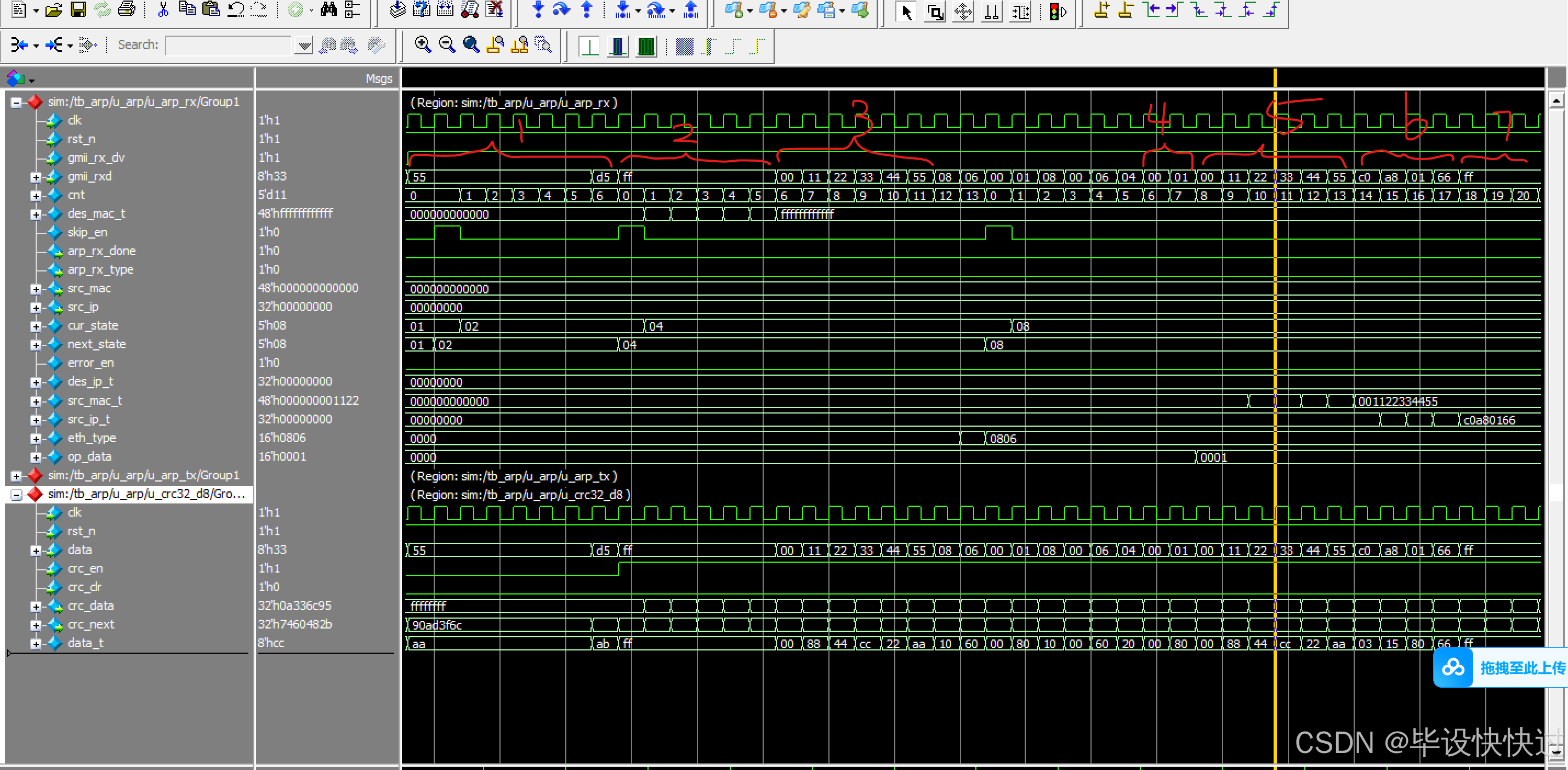

7.2arp_rx仿真

7.2.1arp请求仿真

此时是PC向开发板发送请求,开发板是目的,PC是源。

此时是PC向开发板发送请求,开发板是目的,PC是源。

1:前导码。

2:目的MAC地址,未知,故为广播。

3:源MAC地址即PC MAC地址。

4:OP为1表示是arp请求。

5:源MAC已知。

6:源IP已知。

7:目的MAC未知。

7.2.2arp应答

此时开发板接收PC端应答信号,开发板是目的,PC是源。但源MAC已知。

1:目的MAC。

2:源MAC。

3:02表示是arp应答。

4:源MAC。

5:源IP。

6:目的MAC。

八.板级验证

8.1PC接收开发板arp请求

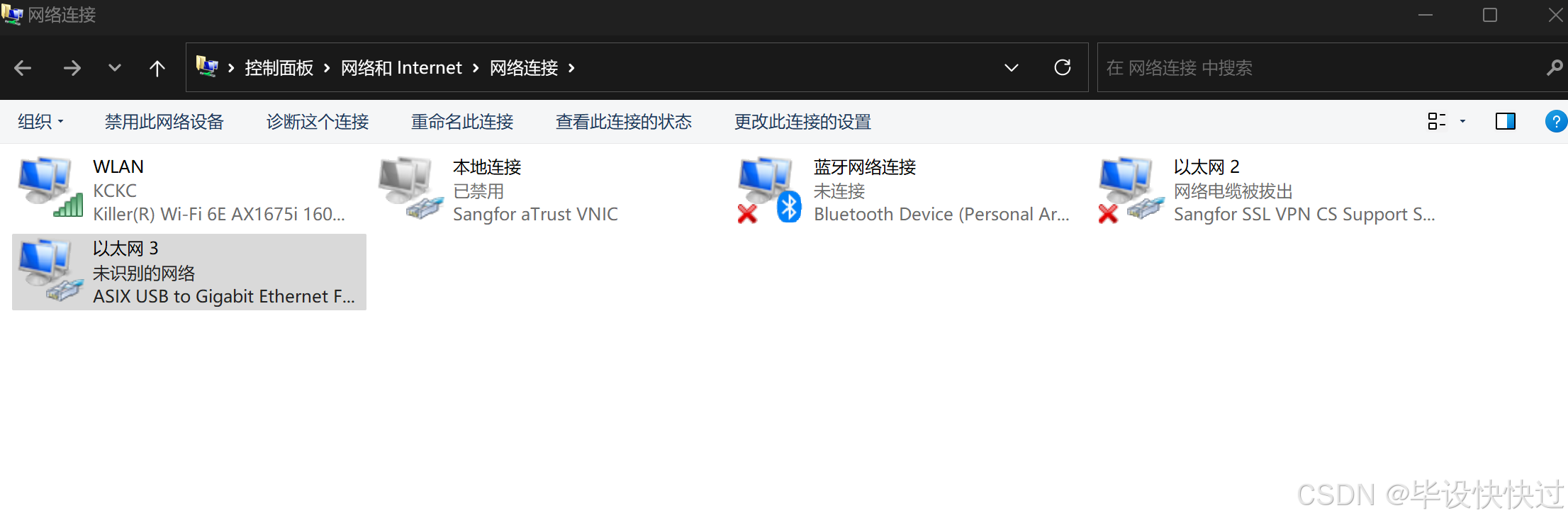

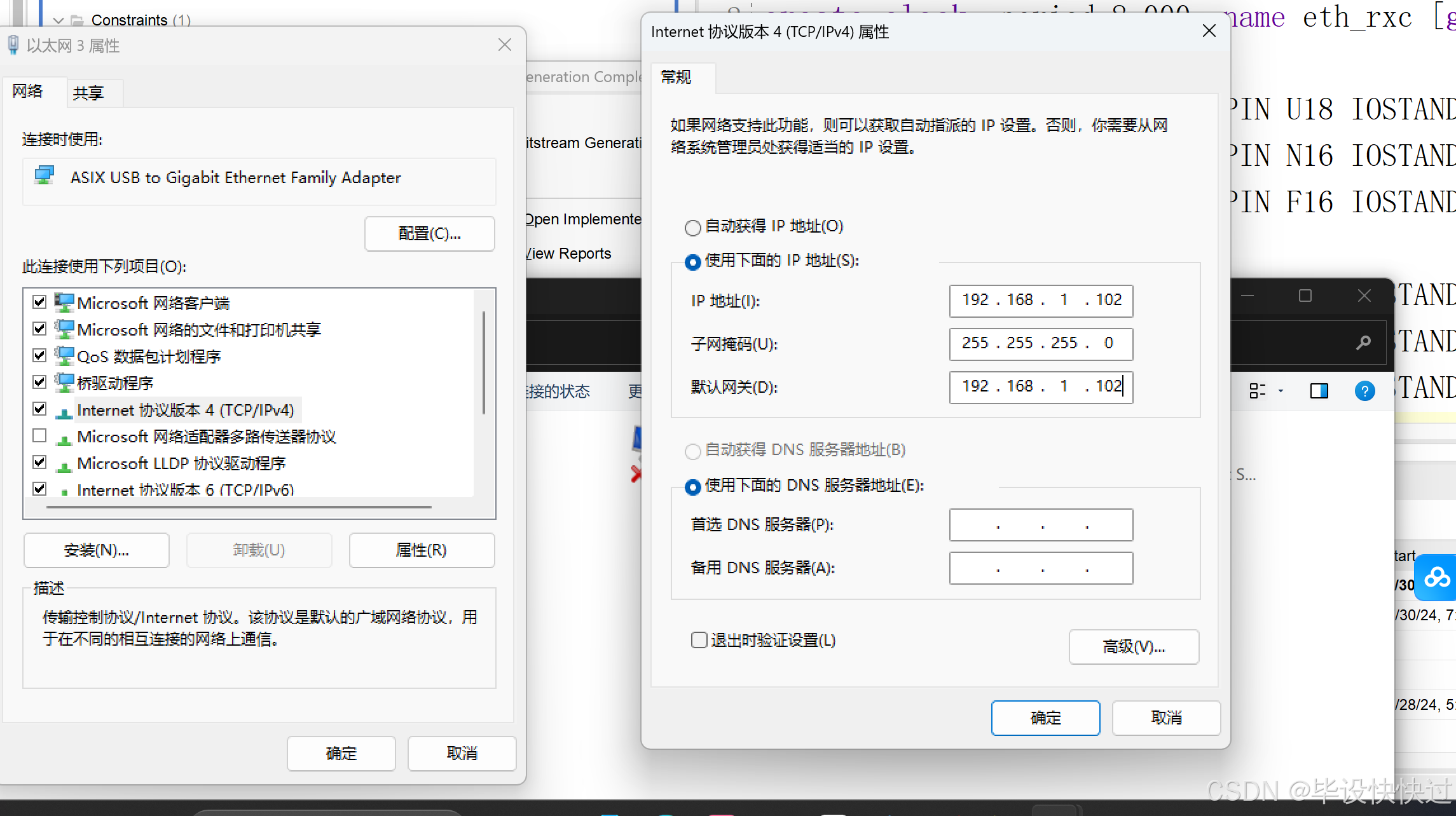

首先将PC端的IP地址设置为192.168.1.102.

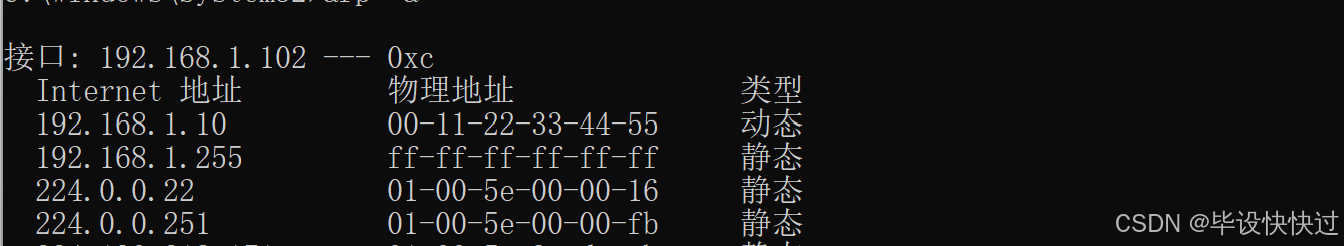

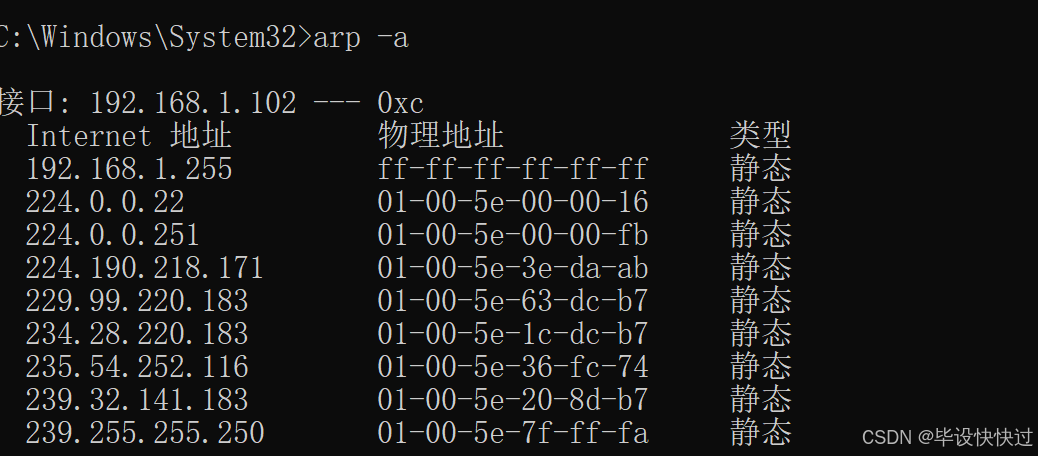

通过arp -a命令 查看接口处表示PC没有收到开发板的arp请求信号。

通过arp -a命令 查看接口处表示PC没有收到开发板的arp请求信号。

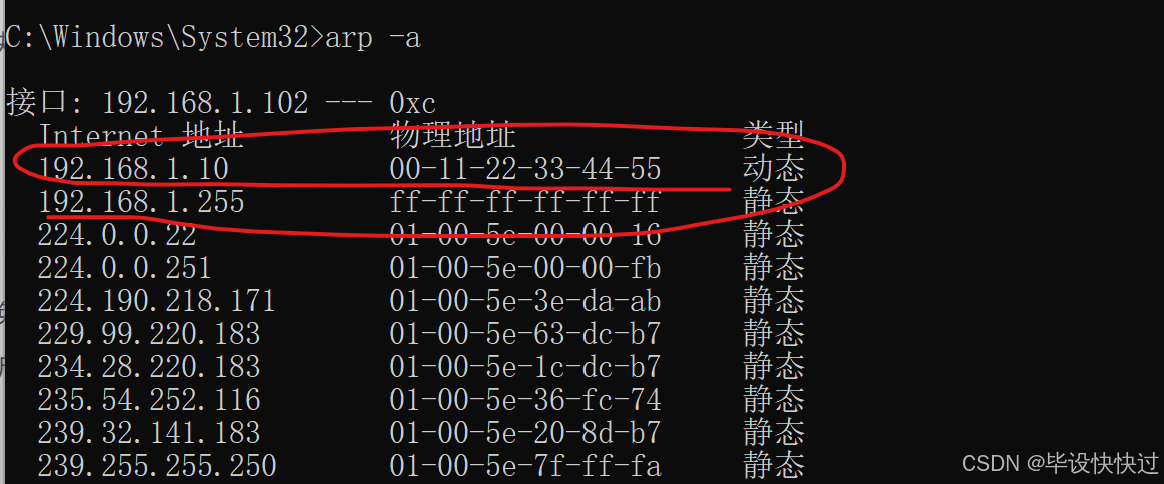

轻触开发板触摸按键,重新查询,可以看到PC已经接收到开发板arp请求信号。

轻触开发板触摸按键,重新查询,可以看到PC已经接收到开发板arp请求信号。

8.2开发板接收PC端arp请求

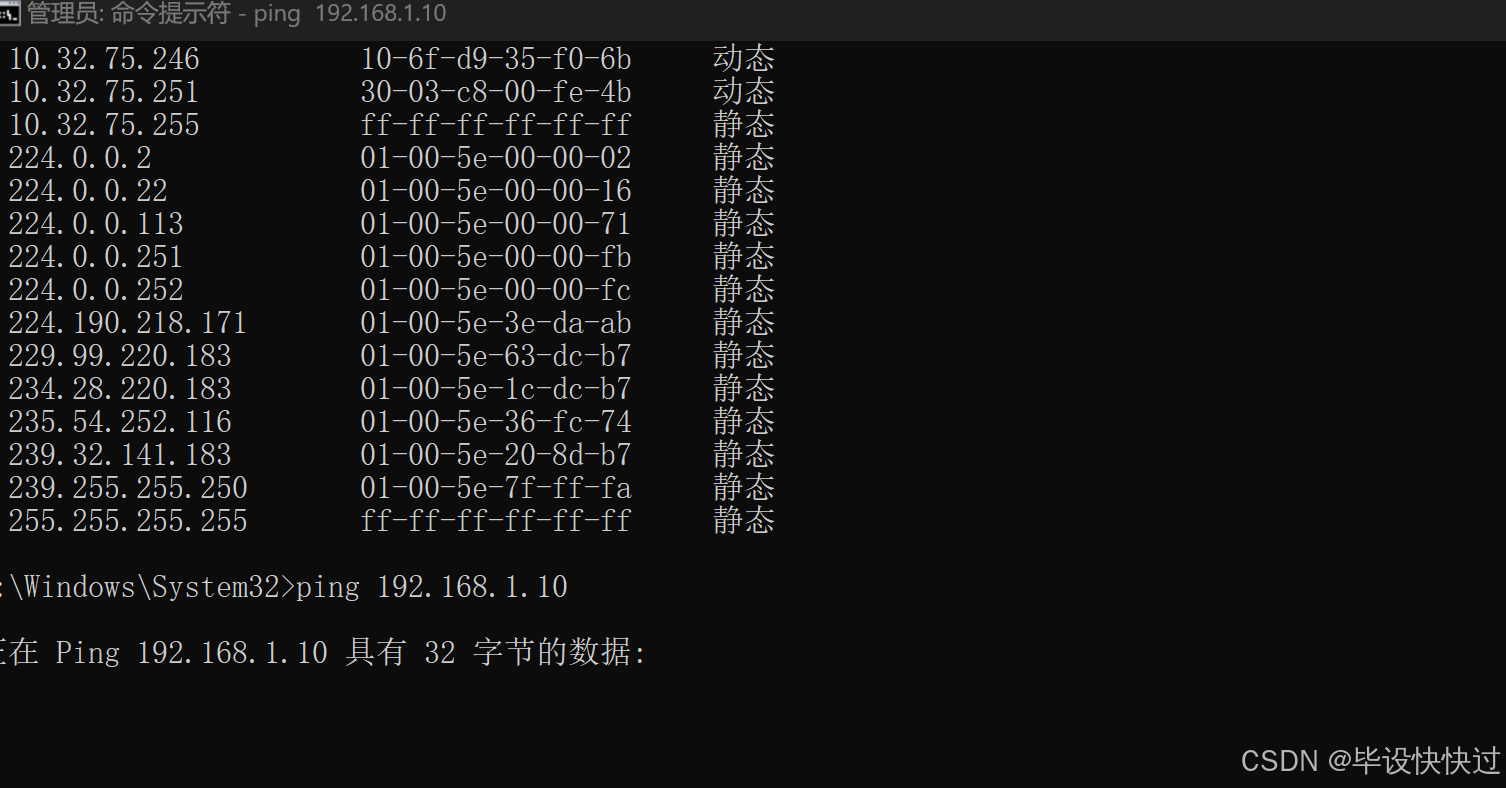

首先使用arp -d命令将上面接口映射表删除,然后使用ping 192.168.1.10向开发板发送arp请求。

PC端发送arp请求。

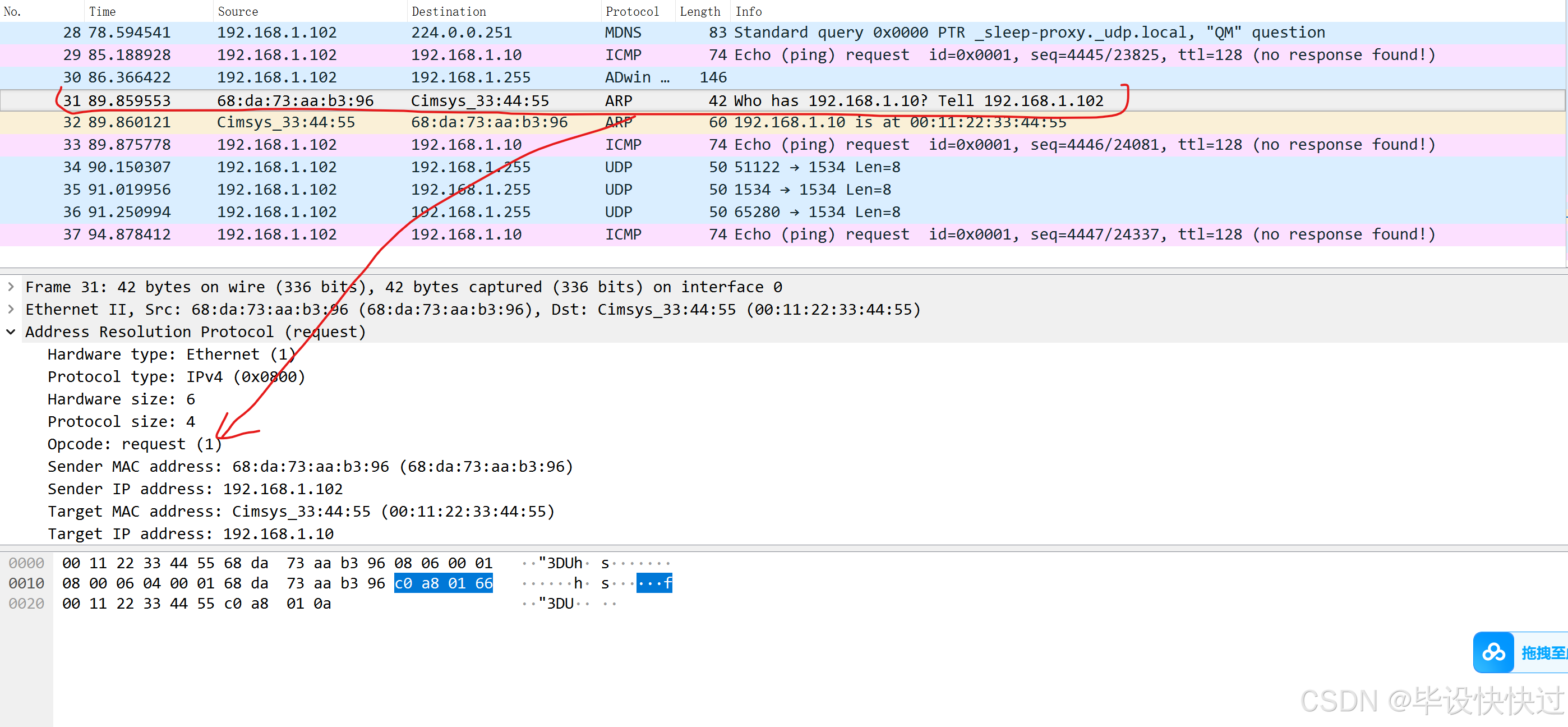

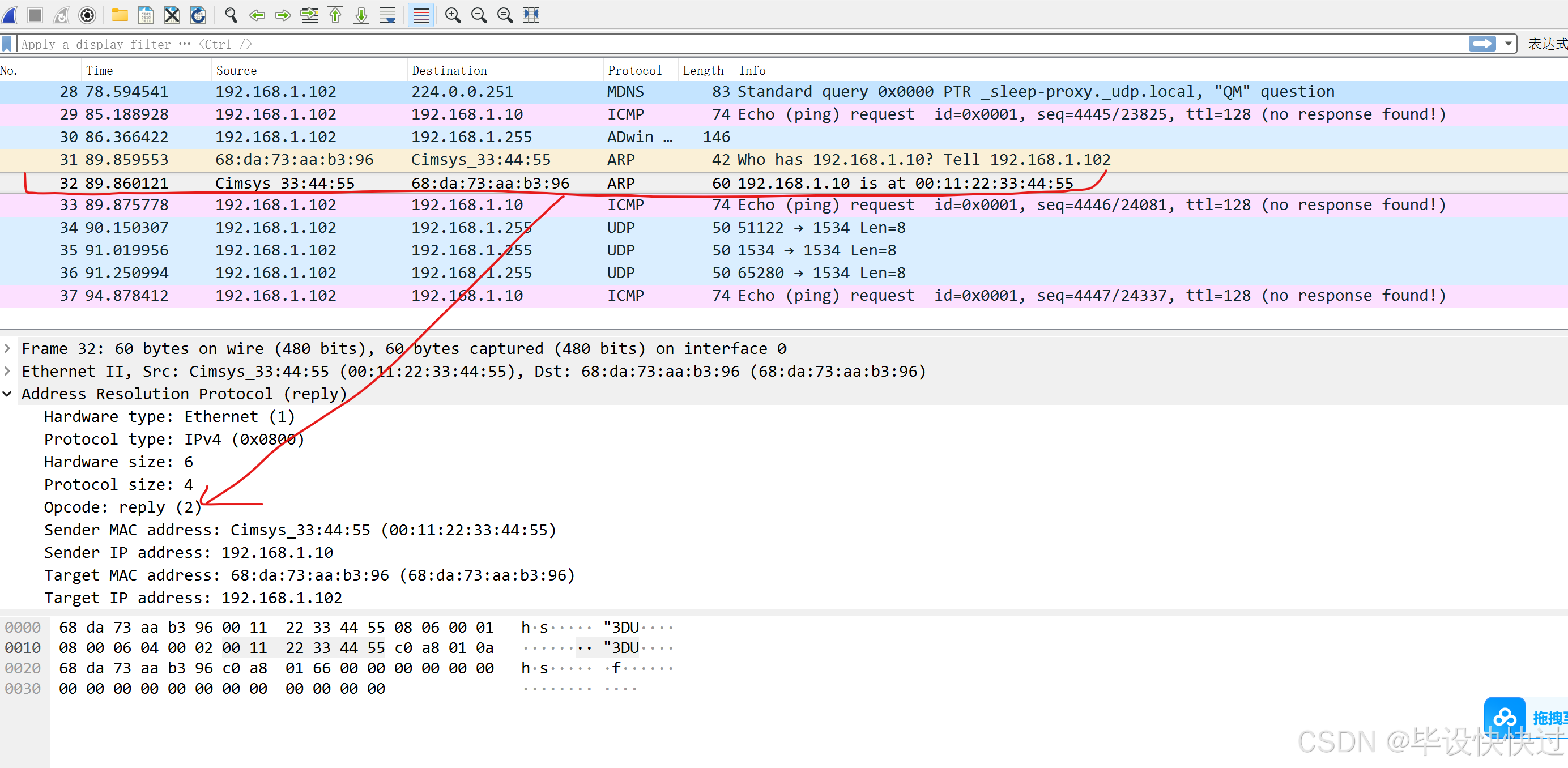

通过WireShark查看arp请求和arp应答信号。

以下是PC端发送的arp请求信号,请求信号中包含PC端IP和PC端MAC和开发板端IP。

以下是开发板的arp应答信号,发送的有开发板IP和开发板MAC即PC端的IP。

通过arp -a查看,接口映射已经成功。