阅读量:0

一、概述

在项目开发的过程当中,我会通常会需要一个东西就行报警显示,有使用语音报警,信息报警等注入此类的方式,但最为简单使用的还是蜂鸣器的使用,蜂鸣器控制简单,成本低,是最为常用的模块之一。今天我们就来对蜂鸣器在FPGA中的使用进行一个简单实现。

二、概念

蜂鸣器原理图

从图中可以看出我们这使用的蜂鸣器是高电平触发。初始蜂鸣器为低电平,当控制引脚按下按下,接通高电平,蜂鸣器通过高电平。这里就一个控制引脚,没有其他需要特别注意的。

三、工程实现

1、设计文件

新建beep.v文件,如下:

//蜂鸣器 module beep( input clk, input rst_n, input flag1, output reg beep_out ); parameter TIME=50_000_000; reg [26:0] cnt; wire add_cnt; wire end_cnt; //分频系数 always @(posedge clk or negedge rst_n)begin if(!rst_n) cnt<=0; else if(add_cnt)begin if(end_cnt) cnt<=0; else cnt<=cnt+1'b1; end end assign add_cnt=1'b1; assign end_cnt=add_cnt &&(cnt==TIME-1); //pwm输出 always @(posedge clk or negedge rst_n)begin if(!rst_n) beep_out<=1'b0; else if(end_cnt) beep_out<=~beep_out; end endmodule 2、测试文件

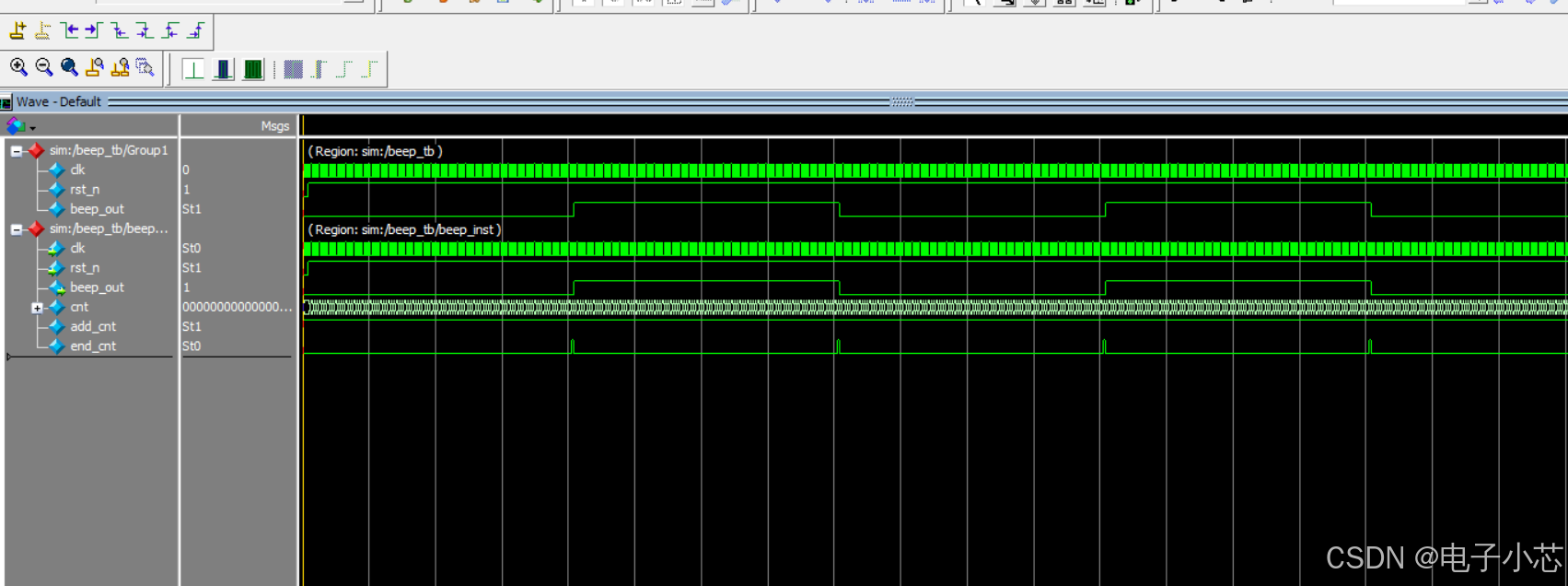

//定义时间尺度 `timescale 1ns/1ns module beep_tb ; //输入信号定义 reg clk ; reg rst_n ; wire beep_out ; //模块例化 beep beep_inst( /*input */ .clk (clk ) , /*input */ .rst_n (rst_n ) , /*output */ .beep_out (beep_out ) ); defparam beep_inst.TIME =100; //激励信号产生 parameter CLK_CYC = 20; //时钟 initial clk=1; always #(CLK_CYC/2)clk=~clk; //复位 initial begin rst_n= 1'b0; #(CLK_CYC*2); #3;//复位结束避开时钟上升沿 rst_n= 1'b1; end endmodule四、波形仿真

通过仿真波形图可以看到当计数器计数了一个周期之后,蜂鸣器状态变换一次,最终在开发板上实现了蜂鸣器响和不响的状态实现