目录

- 1、前言

- 2、相关方案推荐

- 3、详细设计方案

- 4、工程源码1详解-->2路视频缩放拼接,HDMI输出版本

- 5、工程源码2详解-->4路视频缩放拼接,HDMI输出版本

- 6、工程源码3详解-->2路视频缩放拼接,3G-SDI输出版本

- 7、工程源码4详解-->4路视频缩放拼接,3G-SDI输出版本

- 8、工程移植说明

- 9、上板调试验证

- 10、福利:工程代码的获取

Artix7系列FPGA实现SDI视频编解码+图像缩放+多路视频拼接,基于GTP高速接口,提供4套工程源码和技术支持

1、前言

目前FPGA实现SDI视频编解码有两种方案:一是使用专用编解码芯片,比如典型的接收器GS2971,发送器GS2972,优点是简单,比如GS2971接收器直接将SDI解码为并行的YCrCb422,GS2972发送器直接将并行的YCrCb422编码为SDI视频,缺点是成本较高,可以百度一下GS2971和GS2972的价格;另一种方案是使用FPGA逻辑资源部实现SDI编解码,利用Xilinx系列FPGA的GTP/GTX资源实现解串,利用Xilinx系列FPGA的SMPTE SDI资源实现SDI编解码,优点是合理利用了FPGA资源,GTP/GTX资源不用白不用,缺点是操作难度大一些,对FPGA开发者的技术水平要求较高。有意思的是,这两种方案在本博这里都有对应的解决方案,包括硬件的FPGA开发板、工程源码等等。

工程概述

本设计基于Xilinx的Artix7系列FPGA开发板实现SDI视频编解码,输入源为一个3G-SDI相机或者HDMI转3G-SDI盒子,也可以使用HD-SDI或者SD-SDI相机,因为本设计是三种SDI视频自适应的;同轴的SDI视频通过同轴线连接到FPGA开发板的BNC座子,然后同轴视频经过板载的Gv8601a芯片实现单端转差分和均衡EQ的功能;然后差分SDI视频信号进入FPGA内部的GTP高速资源,实现数据高速串行到并行的转换,本博称之为解串;解串后的并行视频再送入Xilinx系列FPGA特有的SMPTE SD/HD/3G SDI IP核,进行SDI视频解码操作并输出BT1120视频,至此,SDI视频解码操作已经完成,可以进行常规的图像处理操作了;

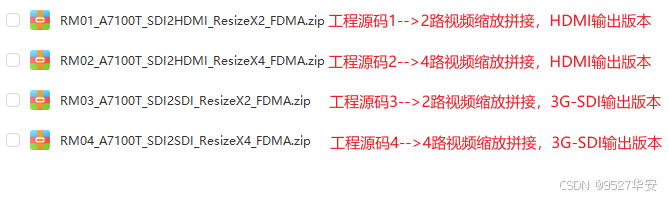

本设计的目的是做图像缩放后输出解码的SDI视频,针对目前市面上的主流项目需求,本博设计了两种输出方式,一种是HDMI输出,另一种是3G-SDI输出,这两种方式都需要对解码BT1120视频进行转RGB和图像缓存操作和图像缩放操作;图像缩放方案采用纯verilog方案;本设计使用BT1120转RGB模块实现视频格式转换;图像缩放采用纯verilog代码实现的图像缩放架构实现SDI的图像缩放操作,将原始的1920x1080分辨率的SDI视频缩小为960x540,当然,读者也可以缩放为其他分辨率;纯verilog多路视频拼接+图像缓存使用FDMA架构,该架构简单灵活,输入接口为VGA视频时序,即用VS、DE、RGB数据,将不同的视频写入不同的内存地址再统一读出来,以达到拼接效果,FDMA架构的视频既可以缓存介质为DDR3;图像从DDR3读出后,进入HDMI发送模块输出HDMI显示器,这是HDMI输出方式;或者经过RGB转BT1120模块实现视频格式转换,然后视频进入SMPTE SD/HD/3G SDI IP核,进行SDI视频编码操作并输出SDI视频,再经过FPGA内部的GTP高速资源,实现并行数据到高速串行的转换,本博称之为串化,差分高速信号再进入板载的Gv8500芯片实现差分转单端和驱动增强的功能,SDI视频通过FPGA开发板的BNC座子输出,通过同轴线连接到SDI转HDMI盒子连接到HDMI显示器,这是SDI输出方式;本博客提供4套工程源码,具体如下:

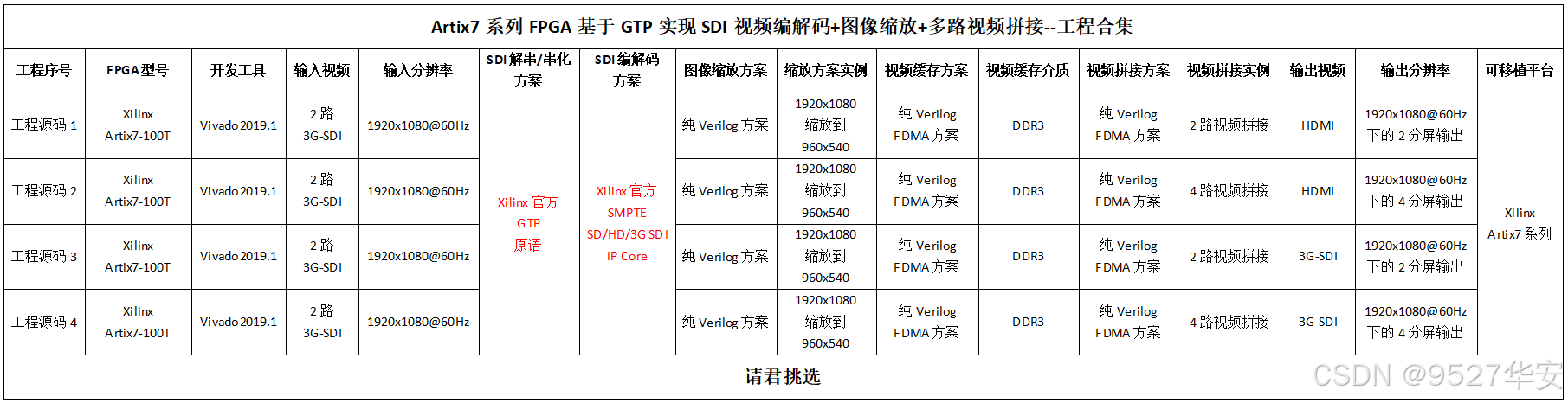

现对上述4套工程源码做如下解释,方便读者理解:

工程源码1

开发板FPGA型号为Xilinx–>Xilinx-Artix7-100T–xc7a100tfgg484-2;输入源有两个,一个是3G-SDI相机,分辨率为1920x1080@60Hz,另一个HDMI转3G-SDI盒子,盒子外接笔记本电脑以模拟SDI相机,分辨率为1920x1080@60Hz;两路输入视频经过板载的2个Gv8601a芯片实现单端转差分和均衡EQ后送入FPGA;再经过2路GTP将SDI视频解串为并行数据;再经过2路SMPTE SDI IP核将SDI解码为2路BT1120数据;再经过2路BT1120转RGB模块将BT1120转换为RGB888视频;再经过2路自研的纯verilog实现的、支持任意比例缩放的图像缩放模块,将输入视频由1920x1080缩放为960x540;再经过自研的2路FPGA图像缓存方案将视频写入DDR3,其中一路FDMA配置为读写,另一路FDMA配置为单写;将不同的视频写入不同的内存地址再统一读出来,以达到拼接效果;然后将拼接视频送入RGB转HDMI模块,将RGB888视频转换为HDMI视频,输出分辨率为1920x1080@60Hz背景下叠加显示2路960x540的有效图像,即2分屏,详细显示效果请看文章末尾的输出演示视频;最后通过HDMI显示器显示图像;该工程需要缓存,适用于Xilinx的Artix7低端系列FPGA实现SDI转HDMI场景;

工程源码2

开发板FPGA型号为Xilinx–>Xilinx-Artix7-100T–xc7a100tfgg484-2;输入源有两个,一个是3G-SDI相机,分辨率为1920x1080@60Hz,另一个HDMI转3G-SDI盒子,盒子外接笔记本电脑以模拟SDI相机,分辨率为1920x1080@60Hz;两路输入视频经过板载的2个Gv8601a芯片实现单端转差分和均衡EQ后送入FPGA;再经过2路GTP将SDI视频解串为并行数据;再经过2路SMPTE SDI IP核将SDI解码为2路BT1120数据;再经过2路BT1120转RGB模块将BT1120转换为RGB888视频;然后将2路视频分别复制1份得到4路视频,以模拟4路输入(如果你的开发板有4路输入,则无需此操作);再经过4路自研的纯verilog实现的、支持任意比例缩放的图像缩放模块,将输入视频由1920x1080缩放为960x540;再经过自研的4路FPGA图像缓存方案将视频写入DDR3,其中三路FDMA配置为读写,另一路FDMA配置为单写;将不同的视频写入不同的内存地址再统一读出来,以达到拼接效果;然后将拼接视频送入RGB转HDMI模块,将RGB888视频转换为HDMI视频,输出分辨率为1920x1080@60Hz背景下叠加显示4路960x540的有效图像,即4分屏,详细显示效果请看文章末尾的输出演示视频;最后通过HDMI显示器显示图像;该工程需要缓存,适用于Xilinx的Artix7低端系列FPGA实现SDI转HDMI场景;

工程源码3

开发板FPGA型号为Xilinx–>Xilinx-Artix7-100T–xc7a100tfgg484-2;输入源有两个,一个是3G-SDI相机,分辨率为1920x1080@60Hz,另一个HDMI转3G-SDI盒子,盒子外接笔记本电脑以模拟SDI相机,分辨率为1920x1080@60Hz;两路输入视频经过板载的2个Gv8601a芯片实现单端转差分和均衡EQ后送入FPGA;再经过2路GTP将SDI视频解串为并行数据;再经过2路SMPTE SDI IP核将SDI解码为2路BT1120数据;再经过2路BT1120转RGB模块将BT1120转换为RGB888视频;再经过2路自研的纯verilog实现的、支持任意比例缩放的图像缩放模块,将输入视频由1920x1080缩放为960x540;再经过自研的2路FPGA图像缓存方案将视频写入DDR3,其中一路FDMA配置为读写,另一路FDMA配置为单写;将不同的视频写入不同的内存地址再统一读出来,以达到拼接效果;然后将视频送RGB转BT1120模块,将RGB888视频转换为BT1120视频;再经过SMPTE SD/HD/3G SDI IP核,将BT1120视频编码为SDI视频;再经过FPGA内部的GTP高速资源,将SDI并行数据转换为高速串行信号;再经过板载的Gv8500芯片实现差分转单端和驱动增强后输出,输出分辨率为1920x1080@60Hz背景下叠加显示2路960x540的有效图像,即2分屏,最后使用SDI转HDMI盒子连接到HDMI显示器显示;详细显示效果请看文章末尾的输出演示视频;该工程需要缓存,适用于Xilinx的Artix7低端系列FPGA实现SDI转SDI场景;

工程源码4

开发板FPGA型号为Xilinx–>Xilinx-Artix7-100T–xc7a100tfgg484-2;输入源有两个,一个是3G-SDI相机,分辨率为1920x1080@60Hz,另一个HDMI转3G-SDI盒子,盒子外接笔记本电脑以模拟SDI相机,分辨率为1920x1080@60Hz;两路输入视频经过板载的2个Gv8601a芯片实现单端转差分和均衡EQ后送入FPGA;再经过2路GTP将SDI视频解串为并行数据;再经过2路SMPTE SDI IP核将SDI解码为2路BT1120数据;再经过2路BT1120转RGB模块将BT1120转换为RGB888视频;然后将2路视频分别复制1份得到4路视频,以模拟4路输入(如果你的开发板有4路输入,则无需此操作);再经过4路自研的纯verilog实现的、支持任意比例缩放的图像缩放模块,将输入视频由1920x1080缩放为960x540;再经过自研的4路FPGA图像缓存方案将视频写入DDR3,其中三路FDMA配置为读写,另一路FDMA配置为单写;将不同的视频写入不同的内存地址再统一读出来,以达到拼接效果;然后将视频送RGB转BT1120模块,将RGB888视频转换为BT1120视频;再经过SMPTE SD/HD/3G SDI IP核,将BT1120视频编码为SDI视频;再经过FPGA内部的GTP高速资源,将SDI并行数据转换为高速串行信号;再经过板载的Gv8500芯片实现差分转单端和驱动增强后输出,输出分辨率为1920x1080@60Hz背景下叠加显示4路960x540的有效图像,即4分屏,最后使用SDI转HDMI盒子连接到HDMI显示器显示;详细显示效果请看文章末尾的输出演示视频;该工程需要缓存,适用于Xilinx的Artix7低端系列FPGA实现SDI转SDI场景;

免责声明

本工程及其源码即有自己写的一部分,也有网络公开渠道获取的一部分(包括CSDN、Xilinx官网、Altera官网等等),若大佬们觉得有所冒犯,请私信批评教育;基于此,本工程及其源码仅限于读者或粉丝个人学习和研究,禁止用于商业用途,若由于读者或粉丝自身原因用于商业用途所导致的法律问题,与本博客及博主无关,请谨慎使用。。。

2、相关方案推荐

本博已有的 SDI 编解码方案

我的博客主页开设有SDI视频专栏,里面全是FPGA编解码SDI的工程源码及博客介绍;既有基于GS2971/GS2972的SDI编解码,也有基于GTP/GTX资源的SDI编解码;既有HD-SDI、3G-SDI,也有6G-SDI、12G-SDI等;专栏地址链接如下:

点击直接前往

本博已有的FPGA图像缩放方案

我的主页目前有FPGA图像缩放专栏,改专栏收录了我目前手里已有的FPGA图像缩放方案,从实现方式分类有基于HSL实现的图像缩放、基于纯verilog代码实现的图像缩放;从应用上分为单路视频图像缩放、多路视频图像缩放、多路视频图像缩放拼接;从输入视频分类可分为OV5640摄像头视频缩放、SDI视频缩放、MIPI视频缩放等等;以下是专栏地址:

点击直接前往

本博已有的已有的FPGA视频拼接叠加融合方案

我的主页目前有FPGA视频拼接叠加融合专栏,改专栏收录了我目前手里已有的FPGA视频拼接叠加融合方案,从实现方式分类有基于HSL实现的视频拼接、基于纯verilog代码实现的视频拼接;从应用上分为单路、2路、3路、4路、8路、16路视频拼接;视频缩放+拼接;视频融合叠加;从输入视频分类可分为OV5640摄像头视频拼接、SDI视频拼接、CameraLink视频拼接等等;以下是专栏地址:

点击直接前往

本方案的无缩放应用

本方案有无缩放版本的应用,只做SDI视频编解码,之前专门写过一篇博客,博客地址链接如下:

点击直接前往

本方案在Xilinx–Kintex系列FPGA上的应用

本方案在Xilinx–Kintex系列FPGA上的也有应用,之前专门写过一篇博客,博客地址链接如下:

点击直接前往

本方案在Xilinx–Zynq系列FPGA上的应用

本方案在Xilinx–Zynq系列FPGA上的也有应用,之前专门写过一篇博客,博客地址链接如下:

点击直接前往

3、详细设计方案

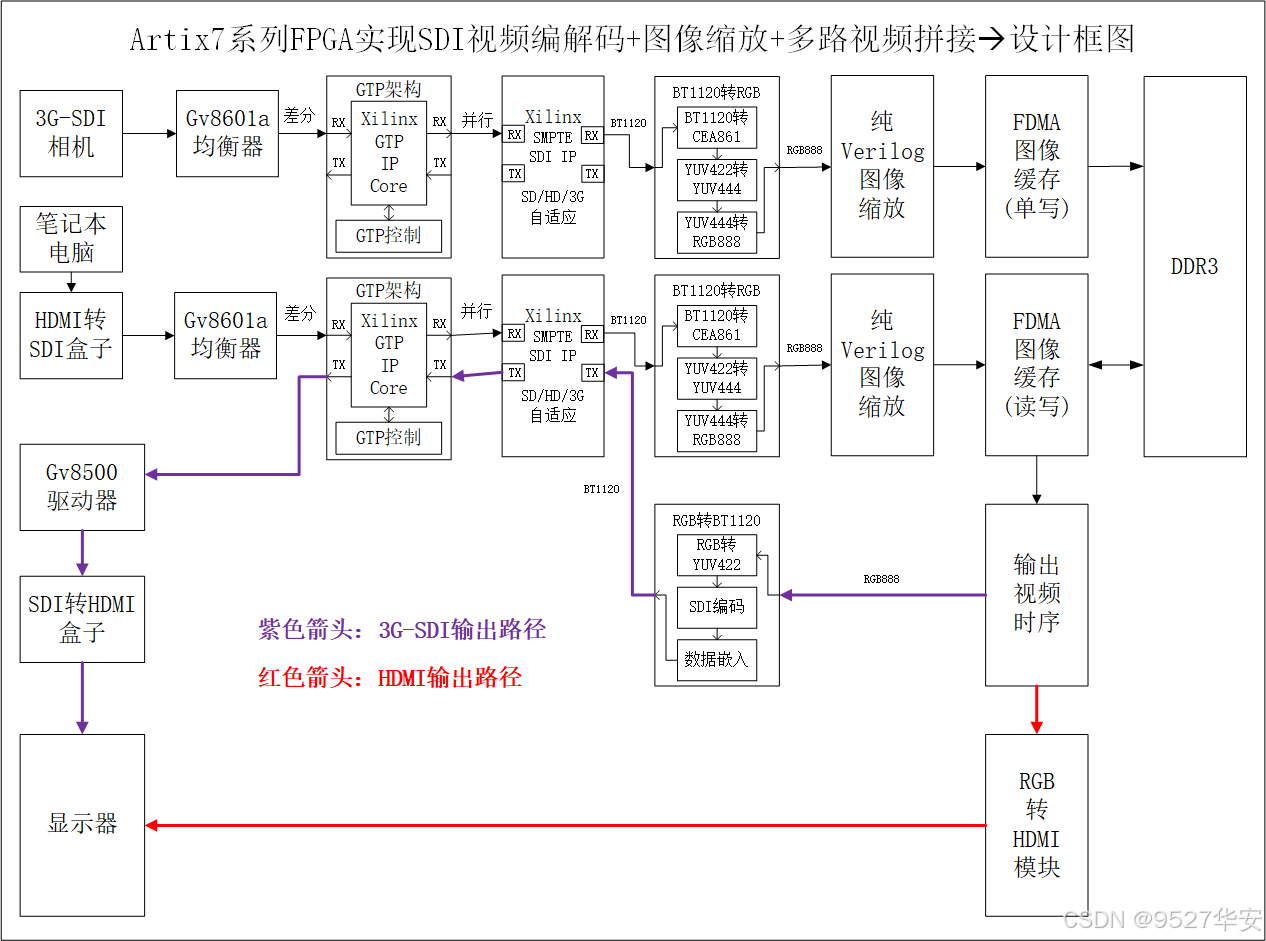

设计原理框图

设计原理框图如下:

注意!!!!

注意!!!!

紫色箭头:3G-SDI输出路径

红色箭头:HDMI输出路径

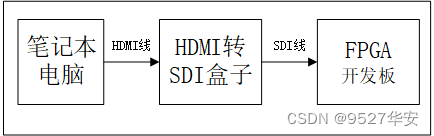

SDI 输入设备

SDI 输入设备有两个,分别接入FPGA开发板的2路SDI视频输入接口;一个是3G-SDI相机,分辨率为1920x1080@60Hz,也可以使用HD-SDI或者SD-SDI相机,因为本设计是三种SDI视频自适应的;另一个HDMI转3G-SDI盒子,盒子外接笔记本电脑以模拟SDI相机;SDI相机相对比较贵,预算有限的朋友可以考虑用HDMI转SDI盒子模拟SDI相机,这种盒子某宝一百块左右;当使用HDMI转SDI盒子时,输入源可以用笔记本电脑,即用笔记本电脑通过HDMI线连接到HDMI转SDI盒子的HDMI输入接口,再用SDI线连接HDMI转SDI盒子的SDI输出接口到FPGA开发板,如下:

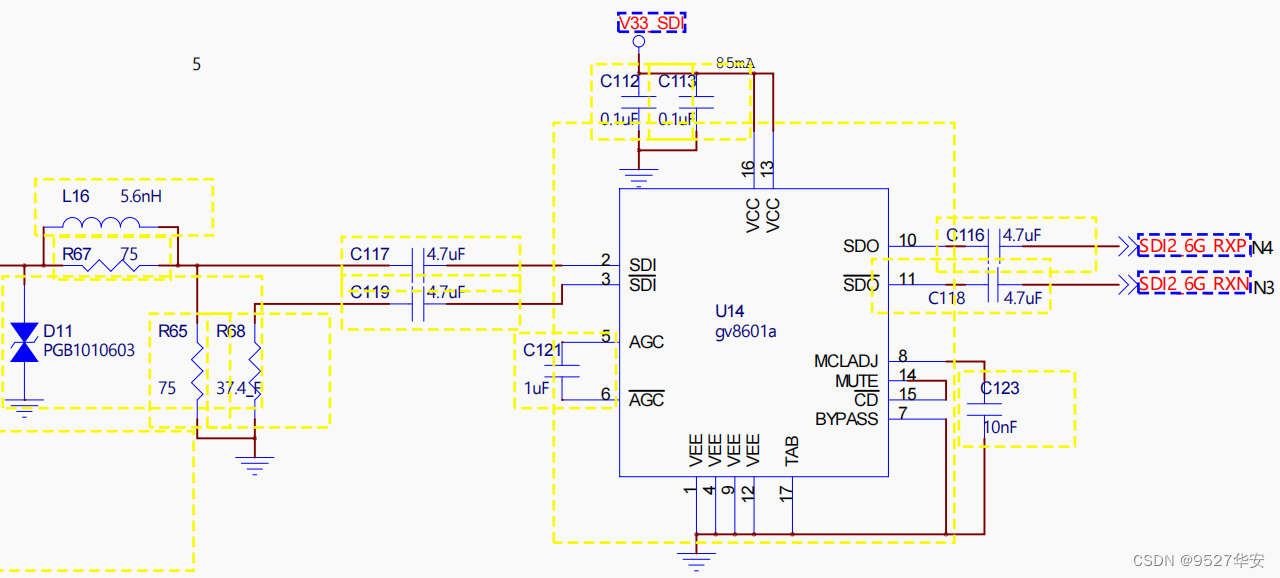

Gv8601a 均衡器

Gv8601a芯片实现单端转差分和均衡EQ的功能,这里选用Gv8601a是因为借鉴了了Xilinx官方的方案,当然也可以用其他型号器件。Gv8601a均衡器原理图如下:

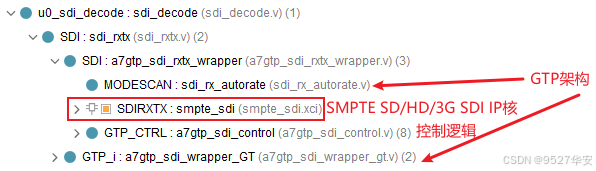

GTP 高速接口–>解串与串化

本设计使用Xilinx特有的GTP高速信号处理资源实现SDI差分视频信号的解串与串化,对于SDI视频接收而言,GTP起到解串的作用,即将输入的高速串行的差分信号解为并行的数字信号;对于SDI视频发送而言,GTP起到串化的作用,即将输入的并行的数字信号串化为高速串行的差分信号;GTP的使用一般需要例化GTP IP核,通过vivado的UI界面进行配置,但本设计需要对SD-SDI、HD-SDI、3G-SDI视频进行自动识别和自适应处理,所以需要使得GTP具有动态改变线速率的功能,该功能可通过DRP接口配置,也可通过GTP的rate接口配置,所以不能使用vivado的UI界面进行配置,而是直接例化GTP的GTPE2_CHANNEL和GTPE2_COMMON源语直接使用GTP资源;此外,为了动态配置GTP线速率,还需要GTP控制模块,该模块参考了Xilinx的官方设计方案,具有动态监测SDI模式,动态配置DRP等功能;该方案参考了Xilinx官方的设计;GTP 解串与串化模块代码架构如下:

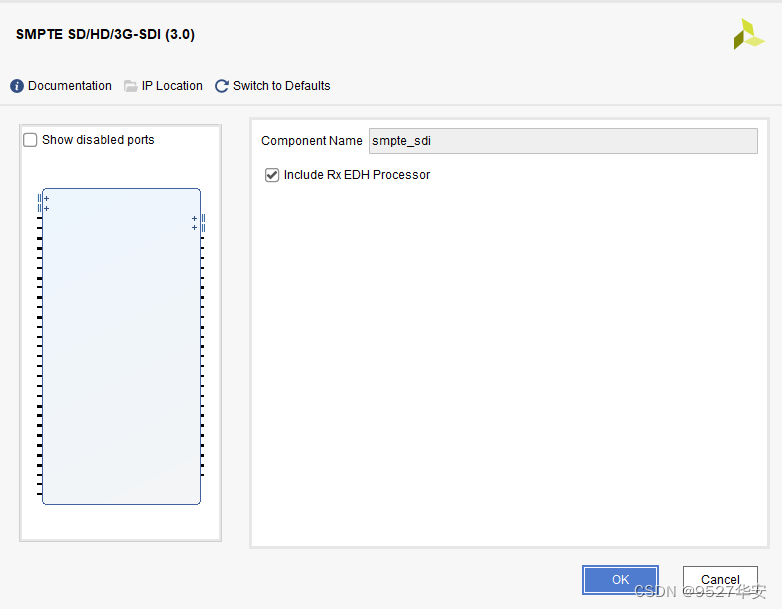

SMPTE SD/HD/3G SDI IP核

SMPTE SD/HD/3G SDI IP核是Xilinx系列FPGA特有的用于SDI视频编解码的IP,该IP配置使用非常简单,vivado的UI界面如下:

SMPTE SD/HD/3G SDI IP核必须与GTP配合才能使用,对于SDI视频接收而言,该IP接收来自于GTP的数据,然后将SDI视频解码为BT1120视频输出,对于SDI视频发送而言,该IP接收来自于用户侧的的BT1120视频数据,然后将BT1120视频编码为SDI视频输出;该方案参考了Xilinx官方的设计;SMPTE SD/HD/3G SDI IP核代码架构如下:

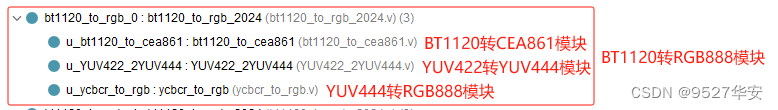

BT1120转RGB

BT1120转RGB模块的作用是将SMPTE SD/HD/3G SDI IP核解码输出的BT1120视频转换为RGB888视频,它由BT1120转CEA861模块、YUV422转YUV444模块、YUV444转RGB888三个模块组成,该方案参考了Xilinx官方的设计;BT1120转RGB模块代码架构如下:

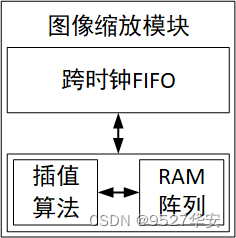

纯Verilog图像缩放模块详解

工程源码1、2的图像缩放模块使用纯Verilog方案,功能框图如下,由跨时钟FIFO、插值+RAM阵列构成,跨时钟FIFO的目的是解决跨时钟域的问题,比如从低分辨率视频放大到高分辨率视频时,像素时钟必然需要变大,这是就需要异步FIFO了,插值算法和RAM阵列具体负责图像缩放算法层面的实现;

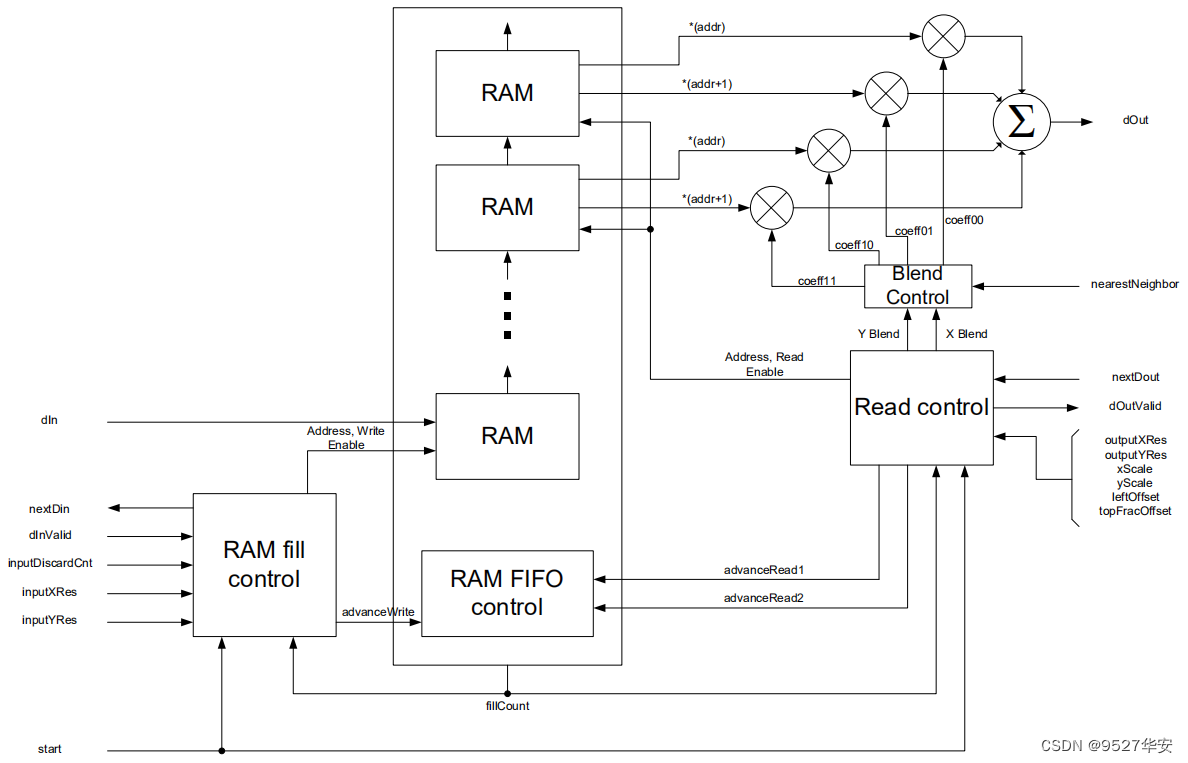

插值算法和RAM阵列以ram和fifo为核心进行数据缓存和插值实现,设计架构如下:

图像缩放模块代码架构如下:模块的例化请参考工程源码的顶层代码;

图像缩放模块FIFO的选择可以调用工程对应的vivado工具自带的FIFO IP核,也可以使用纯verilog实现的FIFO,可通过接口参数选择,图像缩放模块顶层接口如下:

module helai_video_scale #( //---------------------------Parameters---------------------------------------- parameter FIFO_TYPE = "xilinx", // "xilinx" for xilinx-fifo ; "verilog" for verilog-fifo parameter DATA_WIDTH = 8 , //Width of input/output data parameter CHANNELS = 1 , //Number of channels of DATA_WIDTH, for color images parameter INPUT_X_RES_WIDTH = 11 //Widths of input/output resolution control signals )( input i_reset_n , // 输入--低电平复位信号 input [INPUT_X_RES_WIDTH-1:0] i_src_video_width , // 输入视频--即缩放前视频的宽度 input [INPUT_X_RES_WIDTH-1:0] i_src_video_height, // 输入视频--即缩放前视频的高度 input [INPUT_X_RES_WIDTH-1:0] i_des_video_width , // 输出视频--即缩后前视频的宽度 input [INPUT_X_RES_WIDTH-1:0] i_des_video_height, // 输出视频--即缩后前视频的高度 input i_src_video_pclk , // 输入视频--即缩前视频的像素时钟 input i_src_video_vs , // 输入视频--即缩前视频的场同步信号,必须为高电平有效 input i_src_video_de , // 输入视频--即缩前视频的数据有效信号,必须为高电平有效 input [DATA_WIDTH*CHANNELS-1:0] i_src_video_pixel , // 输入视频--即缩前视频的像素数据 input i_des_video_pclk , // 输出视频--即缩后视频的像素时钟,一般为写入DDR缓存的时钟 output o_des_video_vs , // 输出视频--即缩后视频的场同步信号,高电平有效 output o_des_video_de , // 输出视频--即缩后视频的数据有效信号,高电平有效 output [DATA_WIDTH*CHANNELS-1:0] o_des_video_pixel // 输出视频--即缩后视频的像素数据 ); FIFO_TYPE选择原则如下:

1:总体原则,选择"xilinx"好处大于选择"verilog";

2:当你的FPGA逻辑资源不足时,请选"xilinx";

3:当你图像缩放的视频分辨率较大时,请选"xilinx";

4:当你的FPGA没有FIFO IP或者FIFO IP快用完了,请选"verilog";

5:当你向自学一下异步FIFO时,,请选"verilog";

6:不同FPGA型号对应的工程FIFO_TYPE参数不一样,但选择原则一样,具体参考代码;

2种插值算法的整合与选择

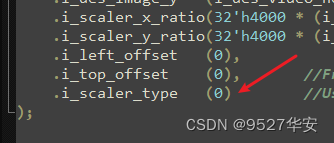

本设计将常用的双线性插值和邻域插值算法融合为一个代码中,通过输入参数选择某一种算法;

具体选择参数如下:

input wire i_scaler_type //0-->bilinear;1-->neighbor 通过输入i_scaler_type 的值即可选择;

输入0选择双线性插值算法;

输入1选择邻域插值算法;

代码里的配置如下:

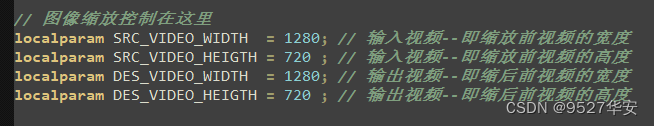

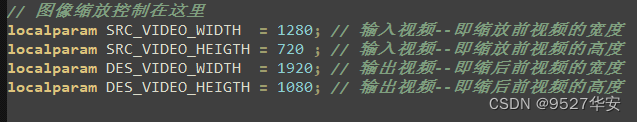

纯Verilog图像缩放模块使用

图像缩放模块使用非常简单,顶层代码里设置了四个参数,举例如下:

上图视频通过图像缩放模块但不进行缩放操作,旨在掌握图像缩放模块的用法;如果需要将图像放大到1080P,则修改为如下:

当然,需要修改的不仅仅这一个地方,FDMA的配置也需要相应修改,详情请参考代码,但我想要证明的是,图像缩放模块使用非常简单,你都不需要知道它内部具体怎么实现的,上手就能用;

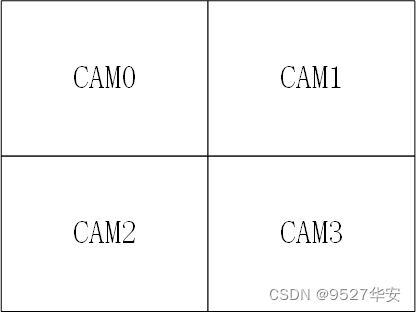

FDMA多路视频拼接算法

纯verilog多路视频拼接方案如下:以4路视频拼接为例;

输出屏幕分辨率为1920X1080;

需要拼接的4路视频分辨率为960X540;

4路输入刚好可以占满整个屏幕;

多路视频的拼接显示原理如下:

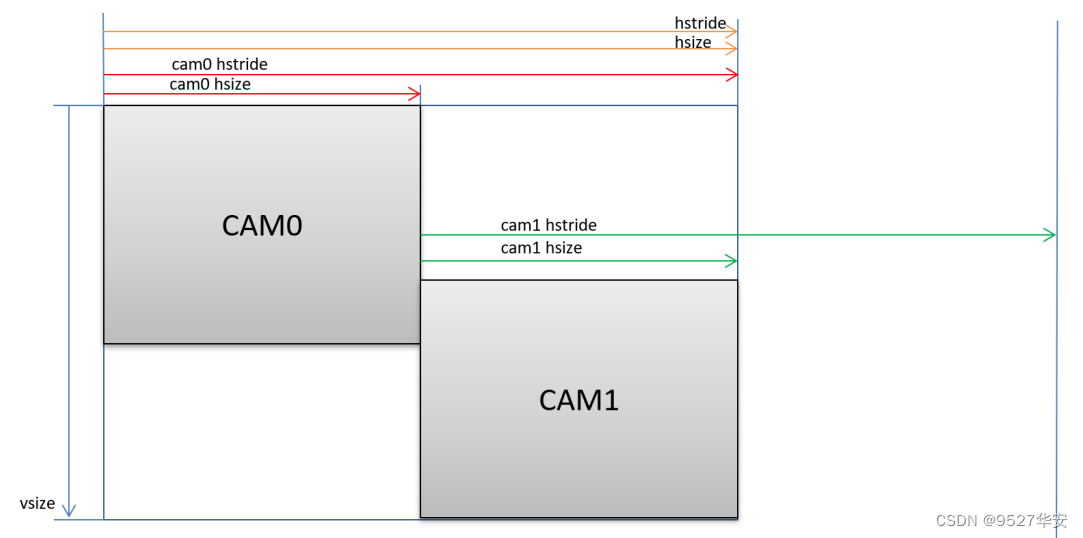

以把 2 个摄像头 CAM0 和 CAM1 输出到同一个显示器上为列,为了把 2 个图像显示到 1 个显示器,首先得搞清楚以下关系:

hsize:每 1 行图像实际在内存中占用的有效空间,以 32bit 表示一个像素的时候占用内存大小为 hsize X 4;

hstride:用于设置每行图像第一个像素的地址,以 32bit 表示一个像素的时候 v_cnt X hstride X 4;

vsize:有效的行;

因此很容易得出 cam0 的每行第一个像素的地址也是 v_cnt X hstride X 4;

同理如果我们需要把 cam1 在 hsize 和 vsize 空间的任何位置显示,我们只要关心 cam1 每一行图像第一个像素的地址,可以用以下公式 v_cnt X hstride X 4 + offset;

uifdma_dbuf 支持 stride 参数设置,stride 参数可以设置输入数据 X(hsize)方向每一行数据的第一个像素到下一个起始像素的间隔地址,利用 stride 参数可以非常方便地摆放输入视频到内存中的排列方式。

关于uifdma_dbuf,可以参考我之前写的文章点击查看:FDMA实现视频数据三帧缓存

根据以上铺垫,每路摄像头缓存的基地址如下:

CAM0:ADDR_BASE=0x80000000;

CAM1:ADDR_BASE=0x80000000+(1920-960)X4;

CAM2:ADDR_BASE=0x80000000+(1080-540)X1920X4;

CAM3:ADDR_BASE=0x80000000+(1080-540)X1920X4+(1920-960)X4;

地址设置完毕后基本就完事儿了;

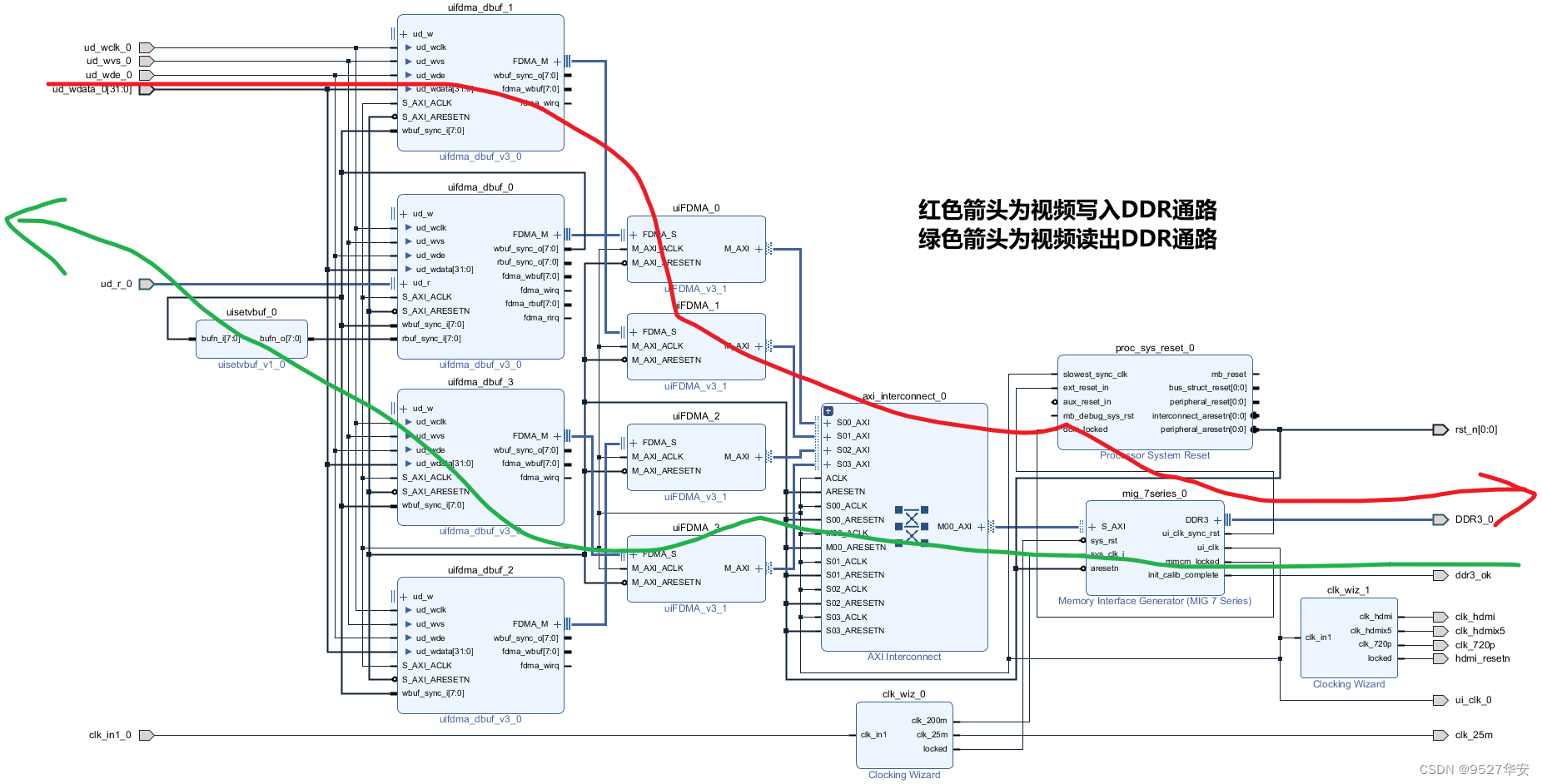

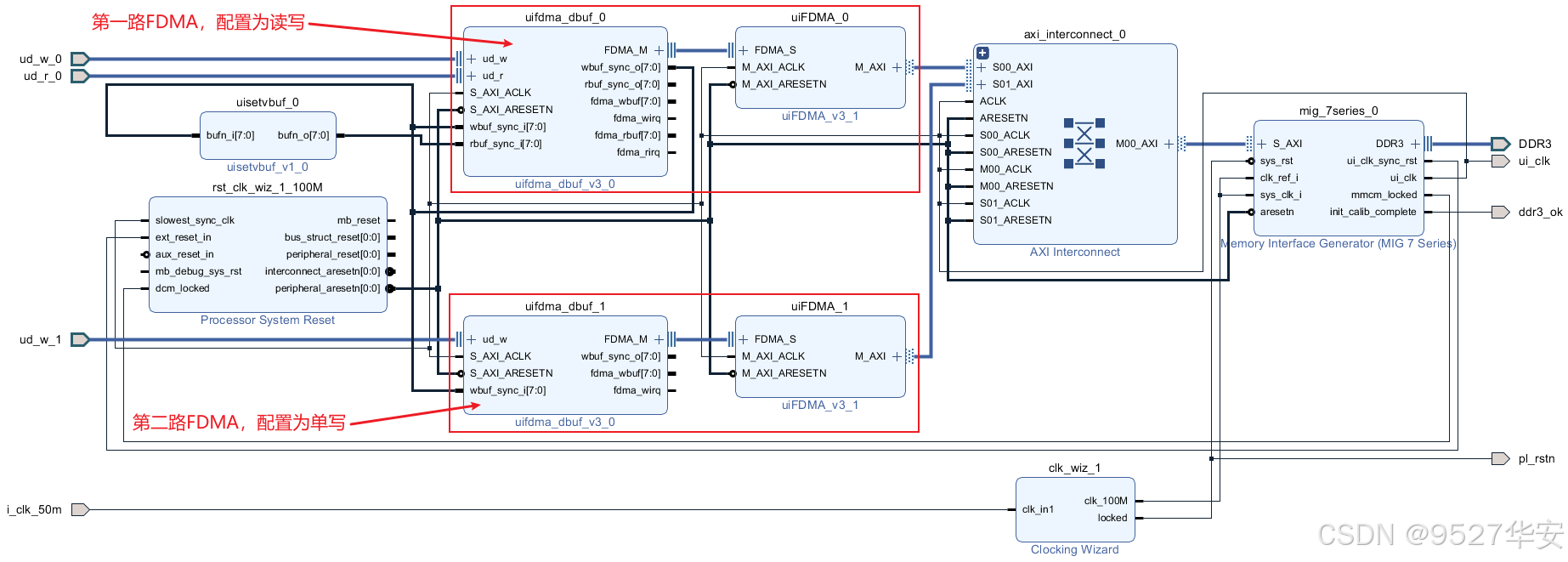

FDMA图像缓存

使用本博常用的FDMA图像缓存架构实现图像3帧缓存,缓存介质为板载的DDR3;FDMA图像缓存架构由FDMA、FDMA控制器、缓存帧选择器构成、Xilinx MIG IP核构成;图像缓存使用Xilinx vivado的Block Design设计,他的作用是将图像送入DDR中做3帧缓存再读出显示,目的是匹配输入输出的时钟差和提高输出视频质量,关于FDMA,请参考我之前的博客,博客地址:点击直接前往

FDMA图像缓存架构如下图所示:截图为4路视频拼接,其他多路视频拼接与之类似;

这里多路视频拼接时,调用多路FDMA进行缓存,具体讲就是每一路视频调用1路FDMA,以4路视频拼接为例:

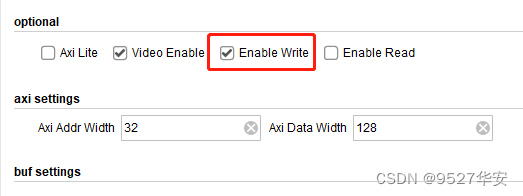

调用4路FDMA,其中三路配置为写模式,因为这三路视频在这里只需要写入DDR3,读出是由另一个FDMA完成,配置如下:

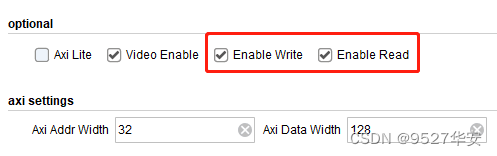

另外1路FDMA配置为读写模式,因为4路视频需要同时一并读出,配置如下:

视频拼接的关键点在于4路视频在DDR3中缓存地址的不同,还是以4路视频拼接为例,4路FDMA的写地址以此为:

第一路视频缓存写基地址:0x80000000;

第二路视频缓存写基地址:0x80000f00;

第三路视频缓存写基地址:0x803f4800;

第四路视频缓存写基地址:0x803f5700;

视频缓存读基地址:0x80000000;

视频读取控制

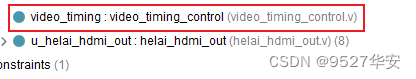

FDMA图像缓存架构使用VGA时序模块完成视频读取控制,VGA时序模块负责产生VGA时序,他有两个作用,一是控制FDMA控制器从DDR3中读出缓存的视频,二是将同步后的VGA视频送入下一级模块,在HDMI输出方式下VGA时序模块的像素时钟由用户提供;在SDI输出方式下VGA时序模块的像素时钟由SMPTE SD/HD/3G SDI IP核的发送用户时钟提供,在不同的SDI模式下像素时钟不同,比如在3G-SDI模式下像素时钟为148.5M,在HD-SDI的720P@60Hz模式下像素时钟为74.25M;HDMI输出方式下的VGA时序模块代码架构如下:

SDI输出方式下的VGA时序模块代码架构如下:

HDMI输出

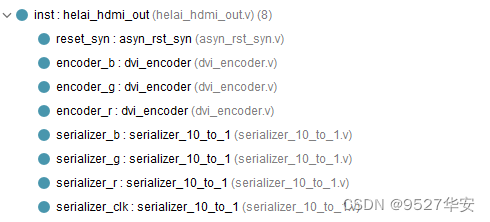

在HDMI输出方式下,使用HDMI输出模块将RGB视频编码为HDMI差分信号,HDMI输出模块采用verilog代码手写,可以用于FPGA的HDMI发送应用,代码如下:

关于这个模块,请参考我之前的博客,博客地址:点击直接前往

RGB转BT1120

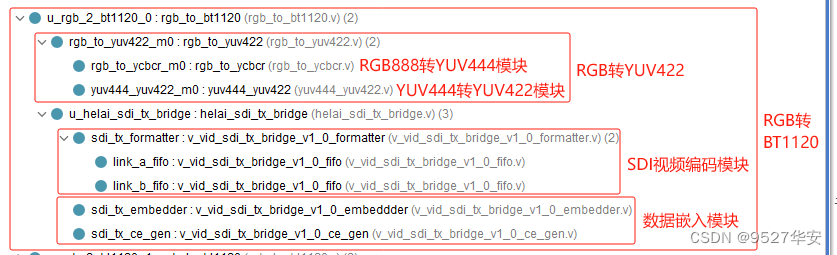

在SDI输出方式下需要使用该模块;RGB转BT1200模块的作用是将用户侧的RGB视频转换为BT1200视频输出给SMPTE SD/HD/3G SDI IP核;RGB转BT1120模块由RGB888转YUV444模块、YUV444转YUV422模块、SDI视频编码模块、数据嵌入模块组成,该方案参考了Xilinx官方的设计;BT1120转RGB模块代码架构如下:

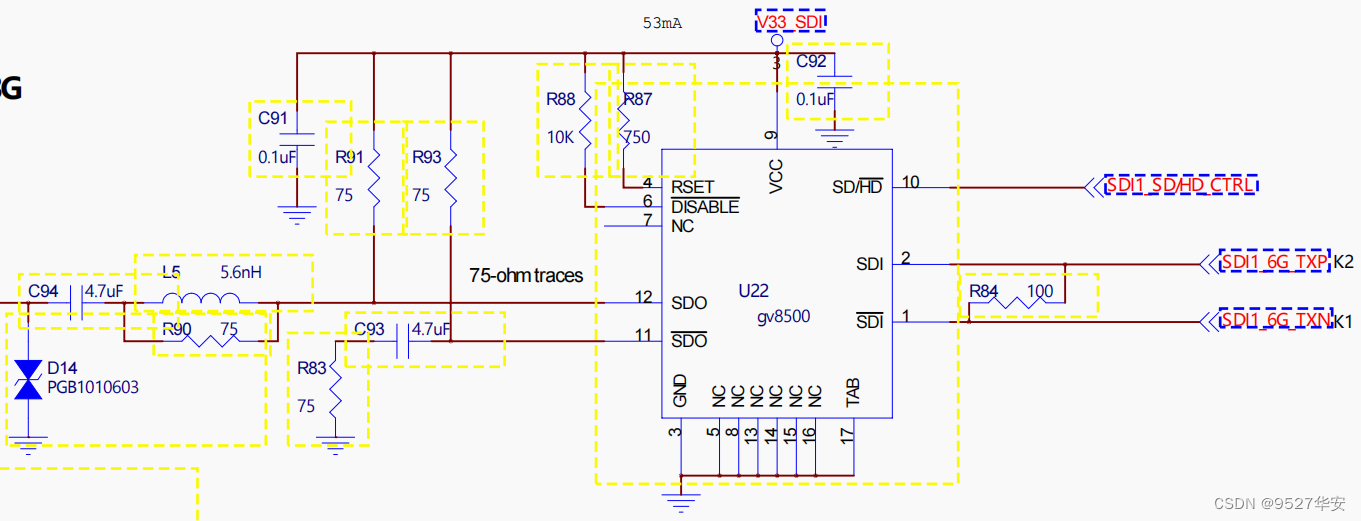

Gv8500 驱动器

Gv8500芯片实现差分转单端和增强驱动的功能,这里选用Gv8500是因为借鉴了了Xilinx官方的方案,当然也可以用其他型号器件。Gv8500驱动器原理图如下:

SDI转HDMI盒子

在SDI输出方式下需要使用到SDI转HDMI盒子,因为我手里的显示器没有SDI接口,只有HDMI接口,为了显示SDI视频,只能这么做,当然,如果你的显示器有SDI接口,则可直接连接显示,我的SDI转HDMI盒子在某宝购买,不到100块;

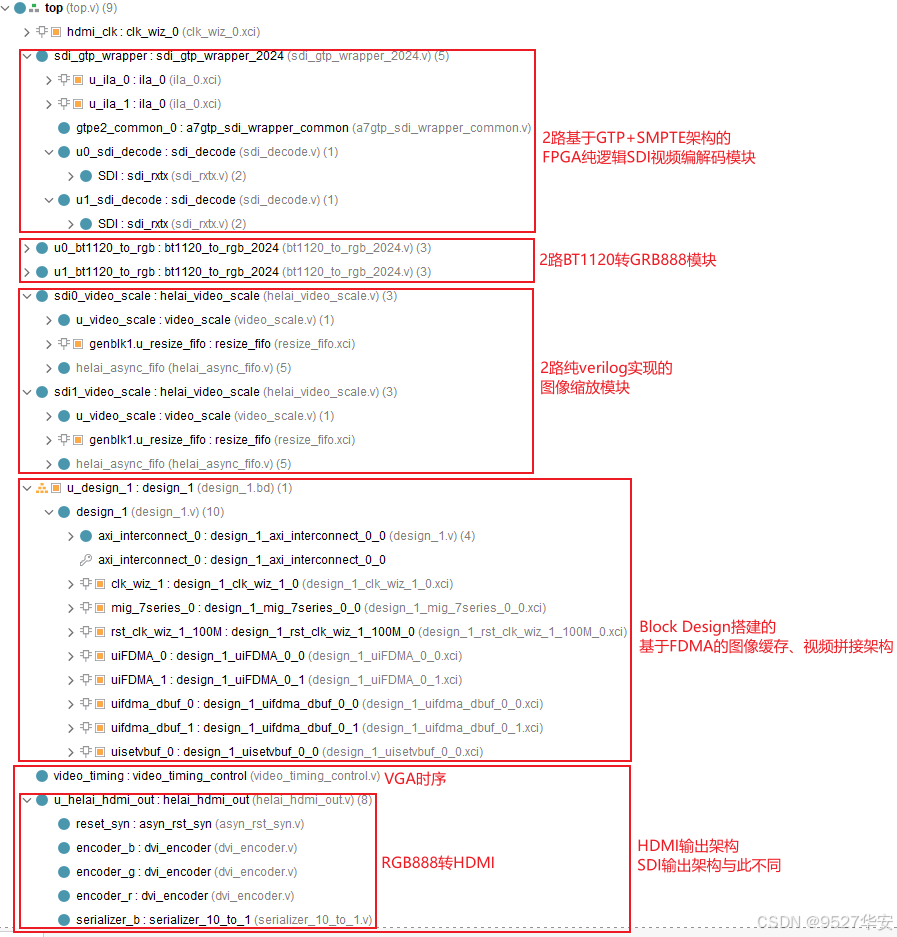

工程源码架构

本博客提供4套工程源码,以工程源码1为例,vivado Block Design设计如下,其他工程与之类似,Block Design设计为图像缓存架构的部分:

以工程源码1为例,使工程源码架构如下,其他工程与之类似:

4、工程源码1详解–>2路视频缩放拼接,HDMI输出版本

开发板FPGA型号:Xilinx-Artix7-100T–xc7a100tfgg484-2;

开发环境:Vivado2019.1;

输入1:3G-SDI相机,分辨率1920x1080@60Hz;

输入2:HDMI转SDI盒子(外接笔记本电脑),分辨率1920x1080@60Hz;

输出:HDMI ,1920x1080@60Hz背景下叠加显示2路拼接的960x540的有效图像;

SDI视频解串方案:Xilinx–GTP高速接口解串;

SDI视频解码方案:Xilinx–SMPTE SD/HD/3G SDI解码;

图像缩放方案:自研纯Verilog图像缩放;

图像缩放实例:1920x1080缩放到960x540;

图像缓存方案:自研FDMA方案;

图像缓存介质:DDR3;

视频拼接方案:自研FDMA方案;

视频拼接应用:2路视频拼接;

工程作用:此工程目的是让读者掌握Xilinx–Artix7低端系列FPGA实现SDI转HDMI的设计能力,以便能够移植和设计自己的项目;

工程Block Design和工程代码架构请参考第3章节的《工程源码架构》小节内容;

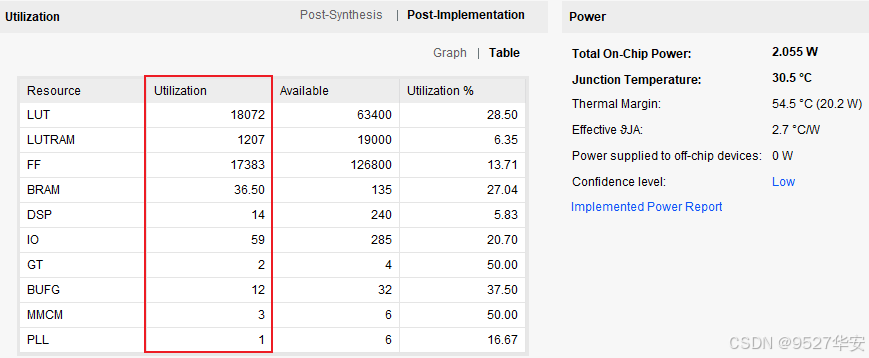

工程的资源消耗和功耗如下:

5、工程源码2详解–>4路视频缩放拼接,HDMI输出版本

开发板FPGA型号:Xilinx-Artix7-100T–xc7a100tfgg484-2;

开发环境:Vivado2019.1;

输入1:3G-SDI相机,分辨率1920x1080@60Hz;

输入2:HDMI转SDI盒子(外接笔记本电脑),分辨率1920x1080@60Hz;

输出:HDMI ,1920x1080@60Hz背景下叠加显示4路拼接的960x540的有效图像;

SDI视频解串方案:Xilinx–GTP高速接口解串;

SDI视频解码方案:Xilinx–SMPTE SD/HD/3G SDI解码;

图像缩放方案:自研纯Verilog图像缩放;

图像缩放实例:1920x1080缩放到960x540;

图像缓存方案:自研FDMA方案;

图像缓存介质:DDR3;

视频拼接方案:自研FDMA方案;

视频拼接应用:4路视频拼接;

工程作用:此工程目的是让读者掌握Xilinx–Artix7低端系列FPGA实现SDI转HDMI的设计能力,以便能够移植和设计自己的项目;

工程Block Design和工程代码架构请参考第3章节的《工程源码架构》小节内容;

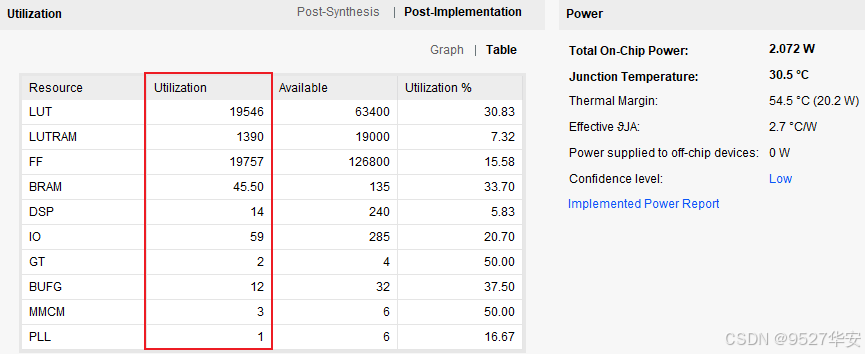

工程的资源消耗和功耗如下:

6、工程源码3详解–>2路视频缩放拼接,3G-SDI输出版本

开发板FPGA型号:Xilinx-Artix7-100T–xc7a100tfgg484-2;

开发环境:Vivado2019.1;

输入1:3G-SDI相机,分辨率1920x1080@60Hz;

输入2:HDMI转SDI盒子(外接笔记本电脑),分辨率1920x1080@60Hz;

输出:3G-SDI,1920x1080@60Hz背景下叠加显示2路拼接的960x540的有效图像;

SDI视频解串方案:Xilinx–GTP高速接口解串;

SDI视频解码方案:Xilinx–SMPTE SD/HD/3G SDI解码;

图像缩放方案:自研纯Verilog图像缩放;

图像缩放实例:1920x1080缩放到960x540;

图像缓存方案:自研FDMA方案;

图像缓存介质:DDR3;

视频拼接方案:自研FDMA方案;

视频拼接应用:2路视频拼接;

工程作用:此工程目的是让读者掌握Xilinx–Artix7低端系列FPGA实现SDI转3G-SDI的设计能力,以便能够移植和设计自己的项目;

工程Block Design和工程代码架构请参考第3章节的《工程源码架构》小节内容;

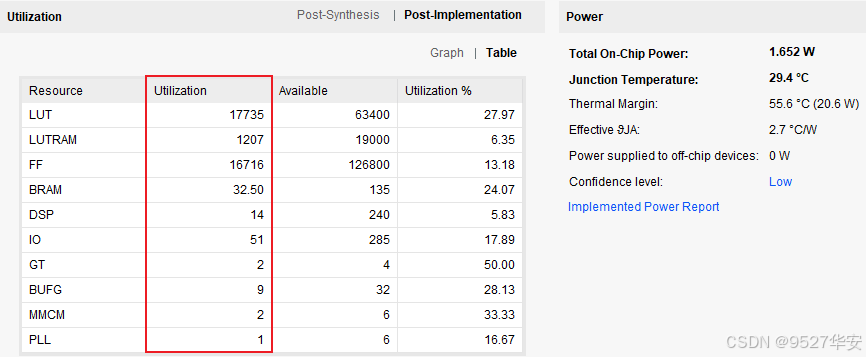

工程的资源消耗和功耗如下:

7、工程源码4详解–>4路视频缩放拼接,3G-SDI输出版本

开发板FPGA型号:Xilinx-Artix7-100T–xc7a100tfgg484-2;

开发环境:Vivado2019.1;

输入1:3G-SDI相机,分辨率1920x1080@60Hz;

输入2:HDMI转SDI盒子(外接笔记本电脑),分辨率1920x1080@60Hz;

输出:3G-SDI,1920x1080@60Hz背景下叠加显示4路拼接的960x540的有效图像;

SDI视频解串方案:Xilinx–GTP高速接口解串;

SDI视频解码方案:Xilinx–SMPTE SD/HD/3G SDI解码;

图像缩放方案:自研纯Verilog图像缩放;

图像缩放实例:1920x1080缩放到960x540;

图像缓存方案:自研FDMA方案;

图像缓存介质:DDR3;

视频拼接方案:自研FDMA方案;

视频拼接应用:4路视频拼接;

工程作用:此工程目的是让读者掌握Xilinx–Artix7低端系列FPGA实现SDI转3G-SDI的设计能力,以便能够移植和设计自己的项目;

工程Block Design和工程代码架构请参考第3章节的《工程源码架构》小节内容;

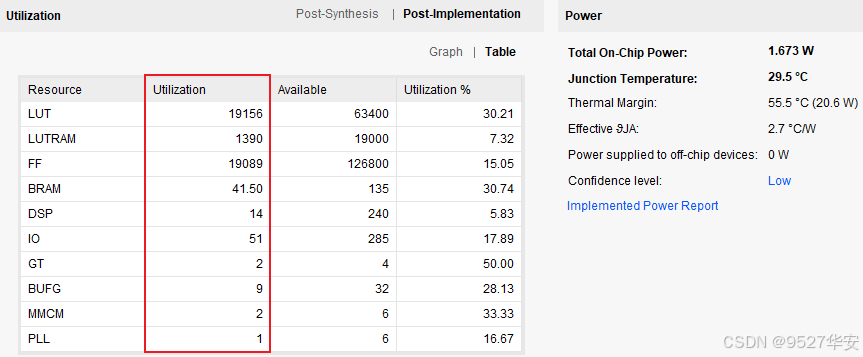

工程的资源消耗和功耗如下:

8、工程移植说明

vivado版本不一致处理

1:如果你的vivado版本与本工程vivado版本一致,则直接打开工程;

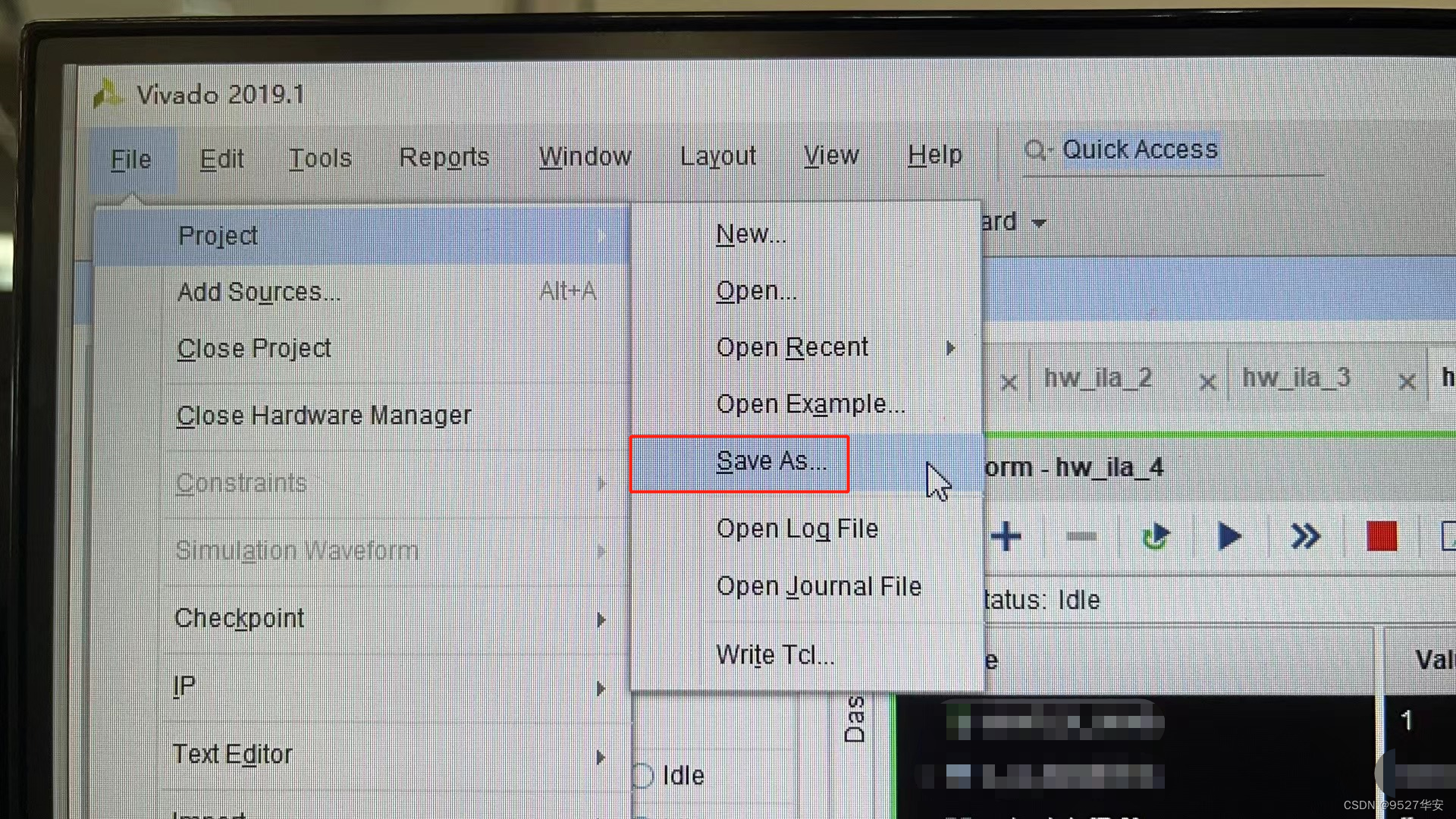

2:如果你的vivado版本低于本工程vivado版本,则需要打开工程后,点击文件–>另存为;但此方法并不保险,最保险的方法是将你的vivado版本升级到本工程vivado的版本或者更高版本;

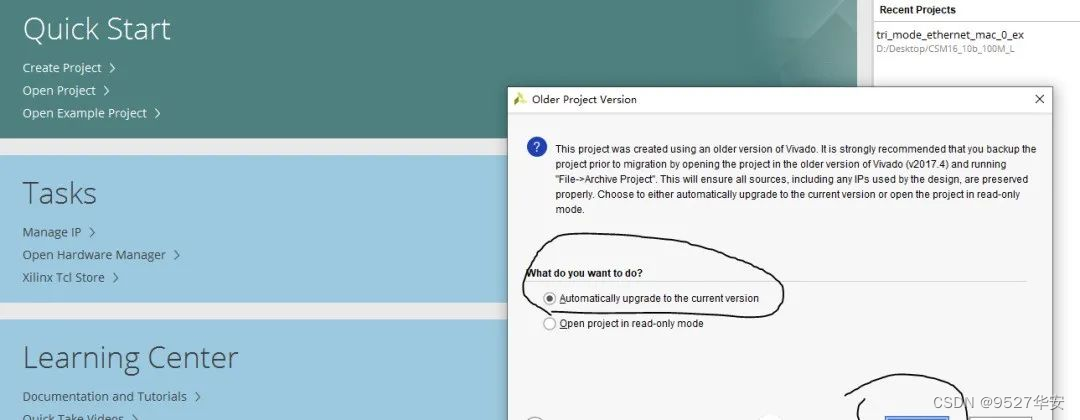

3:如果你的vivado版本高于本工程vivado版本,解决如下:

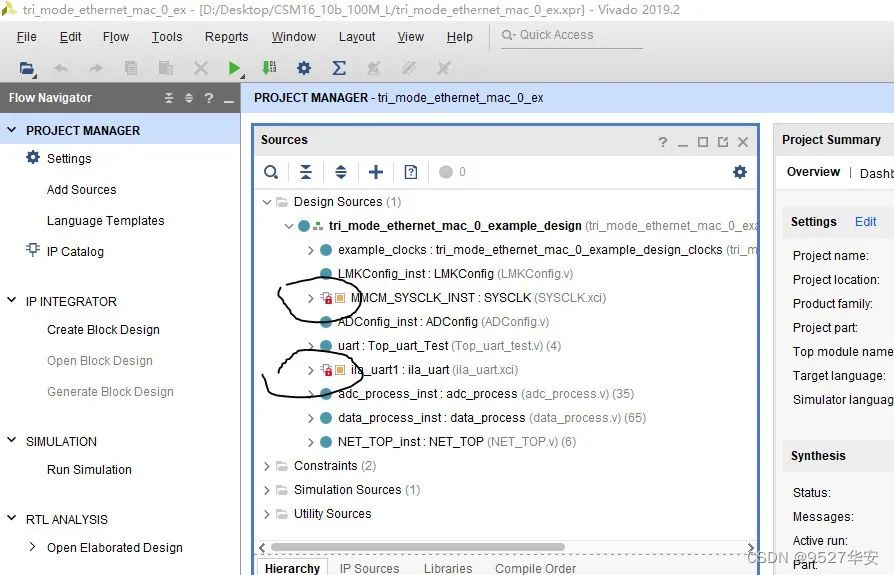

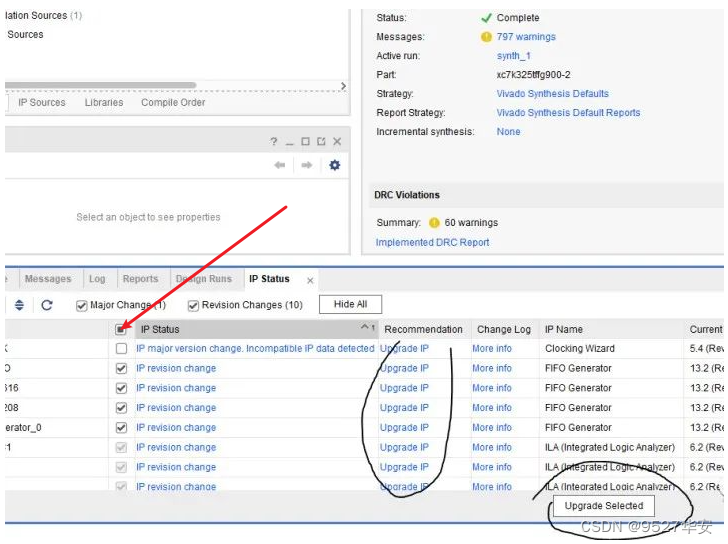

打开工程后会发现IP都被锁住了,如下:

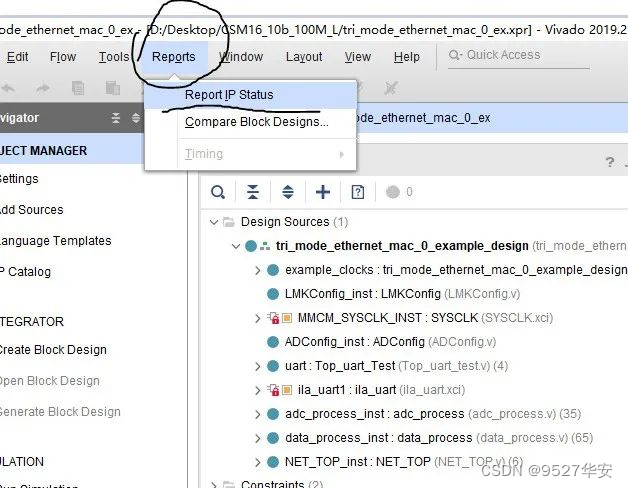

此时需要升级IP,操作如下:

FPGA型号不一致处理

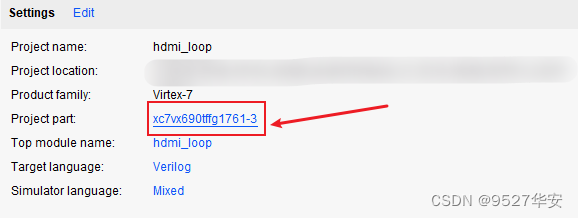

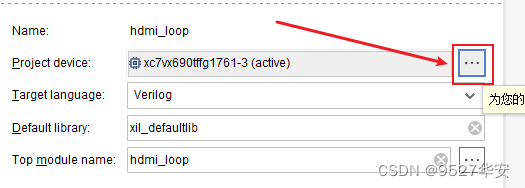

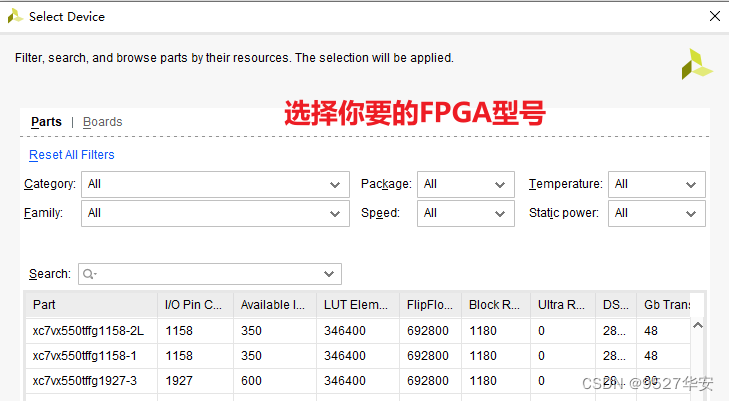

如果你的FPGA型号与我的不一致,则需要更改FPGA型号,操作如下:

更改FPGA型号后还需要升级IP,升级IP的方法前面已经讲述了;

其他注意事项

1:由于每个板子的DDR不一定完全一样,所以MIG IP需要根据你自己的原理图进行配置,甚至可以直接删掉我这里原工程的MIG并重新添加IP,重新配置;

2:根据你自己的原理图修改引脚约束,在xdc文件中修改即可;

3:纯FPGA移植到Zynq需要在工程中添加zynq软核;

9、上板调试验证

准备工作

需要准备的器材如下:

FPGA开发板;

SDI摄像头或HDMI转SDI盒子;

SDI转HDMI盒子;

HDMI显示器;

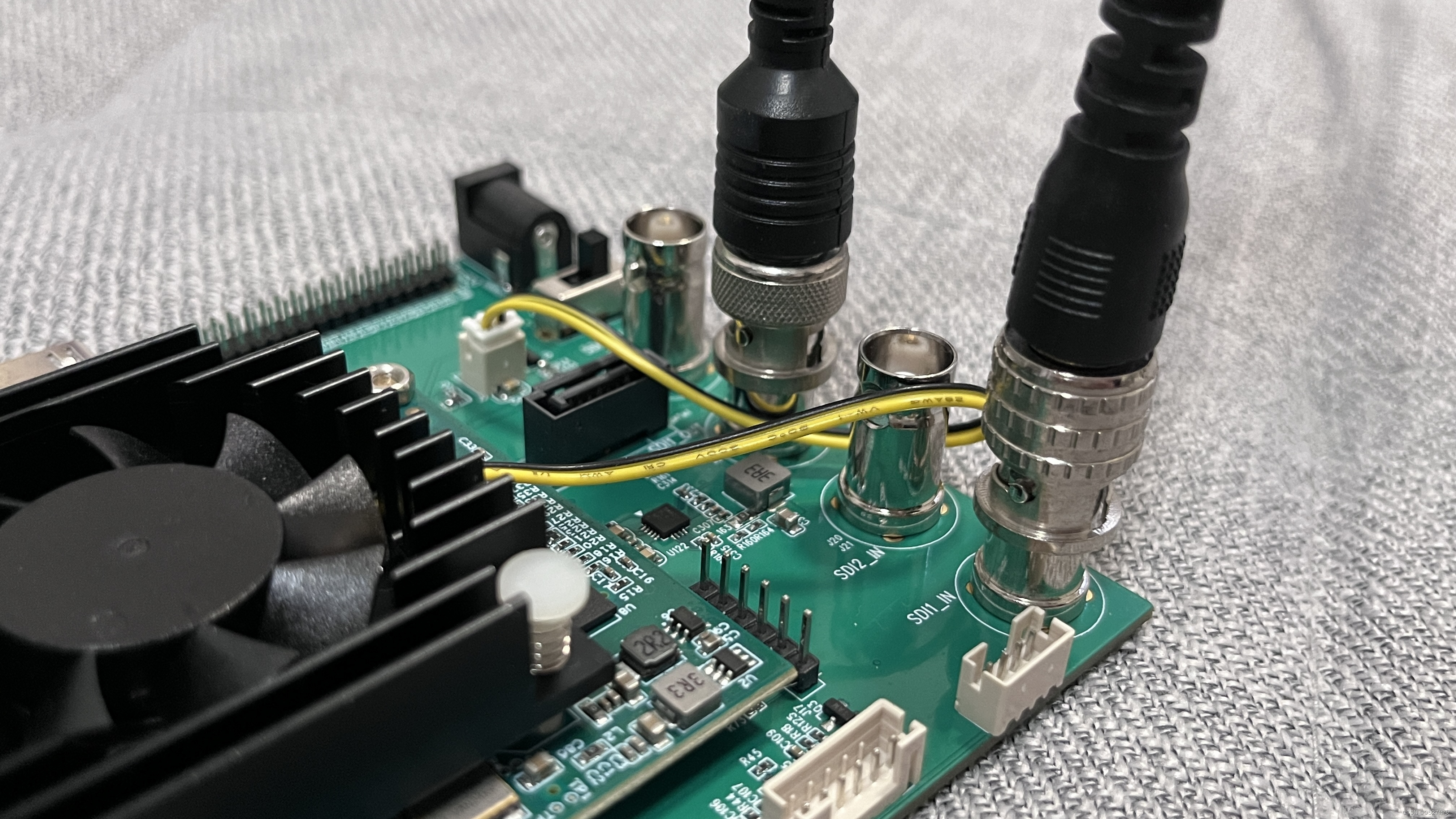

我的开发板了连接如下:

2路SDI视频缩放拼接–>输出视频演示

2路SDI视频缩放拼接,输出如下:

Zynq-SDI-2路视频拼接

4路SDI视频缩放拼接–>输出视频演示

4路SDI视频缩放拼接,输出如下:

Zynq-SDI-4路视频拼接

10、福利:工程代码的获取

福利:工程代码的获取

代码太大,无法邮箱发送,以某度网盘链接方式发送,

资料获取方式:私,或者文章末尾的V名片。

网盘资料如下:

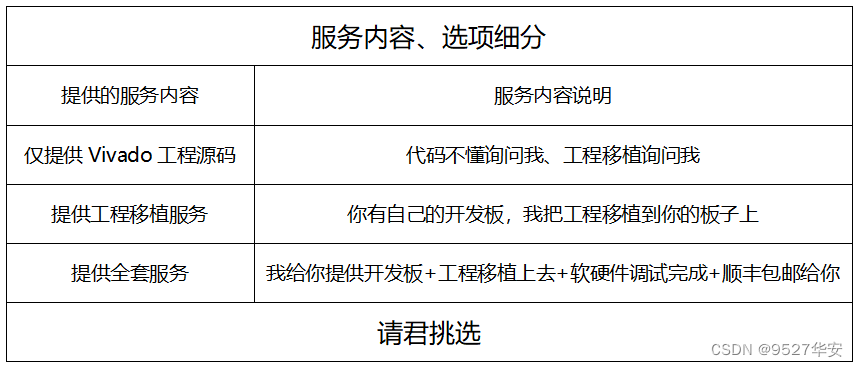

此外,有很多朋友给本博主提了很多意见和建议,希望能丰富服务内容和选项,因为不同朋友的需求不一样,所以本博主还提供以下服务: