GPIO口以及EXTI外部中断

GPIO

一、简介

可配置为4种输入模式、4种输出模式

引脚电平0~3.3V,部分可以容忍5V

输出模式下可控制端口输出高低电平,用以驱动LED、控制蜂鸣器、模拟通信协议输出时序等

输入模式下可读取端口的高低电平或电压,用于读取按键输入、外接模块电平信号输入、ADC电压采集、模拟通信协议接收数据等

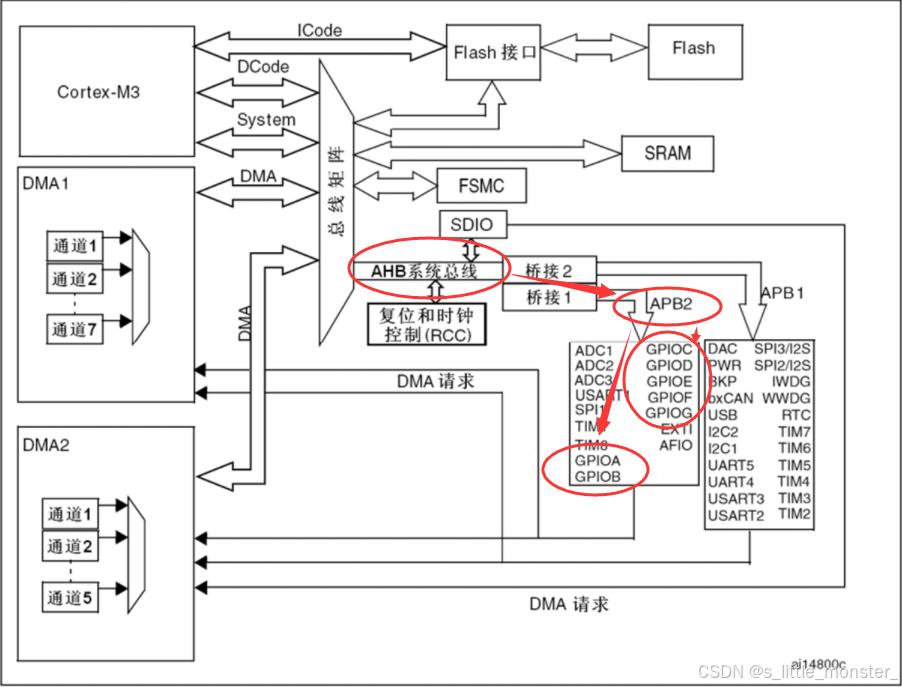

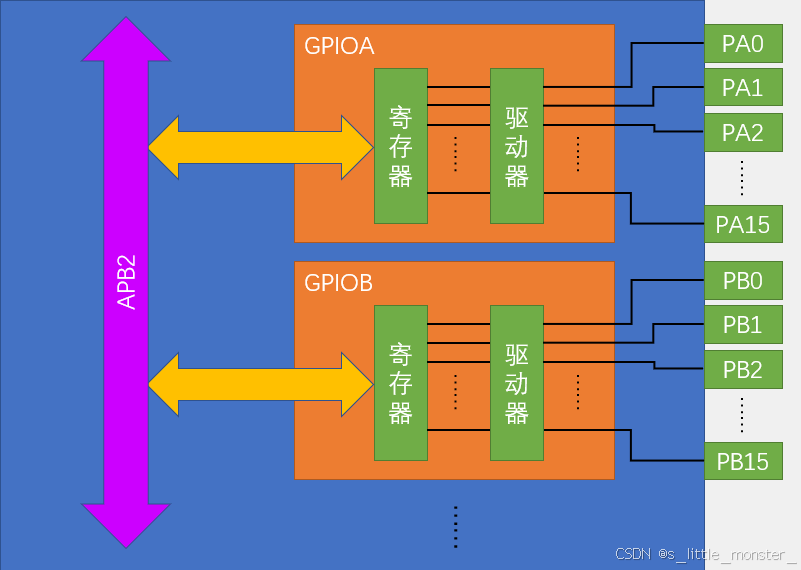

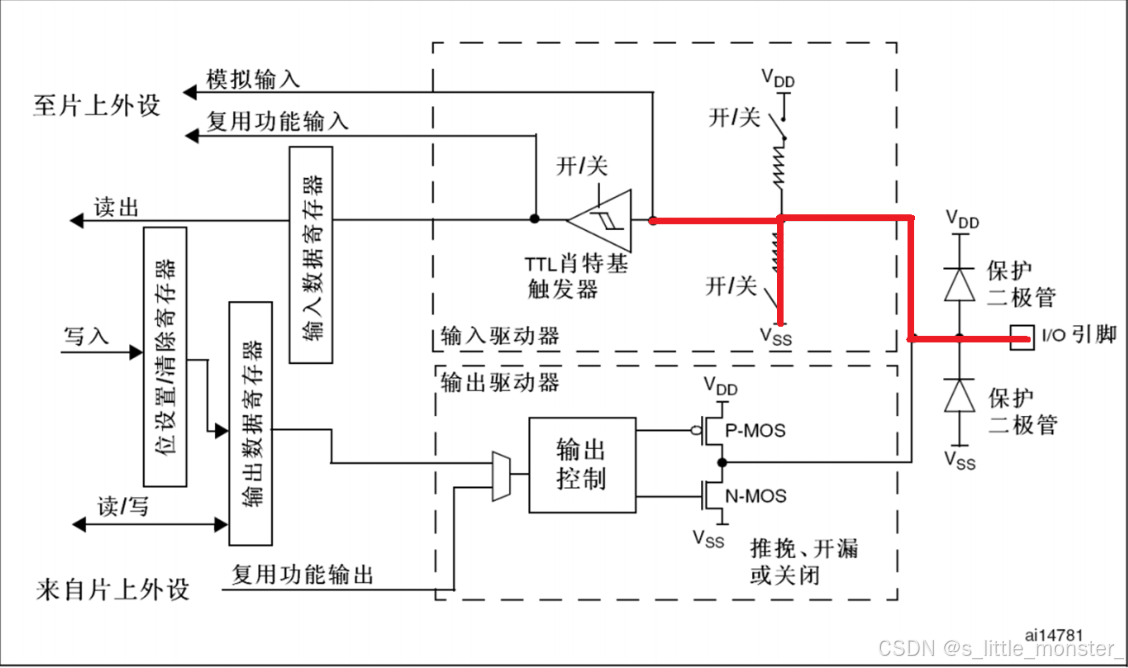

二、基本结构

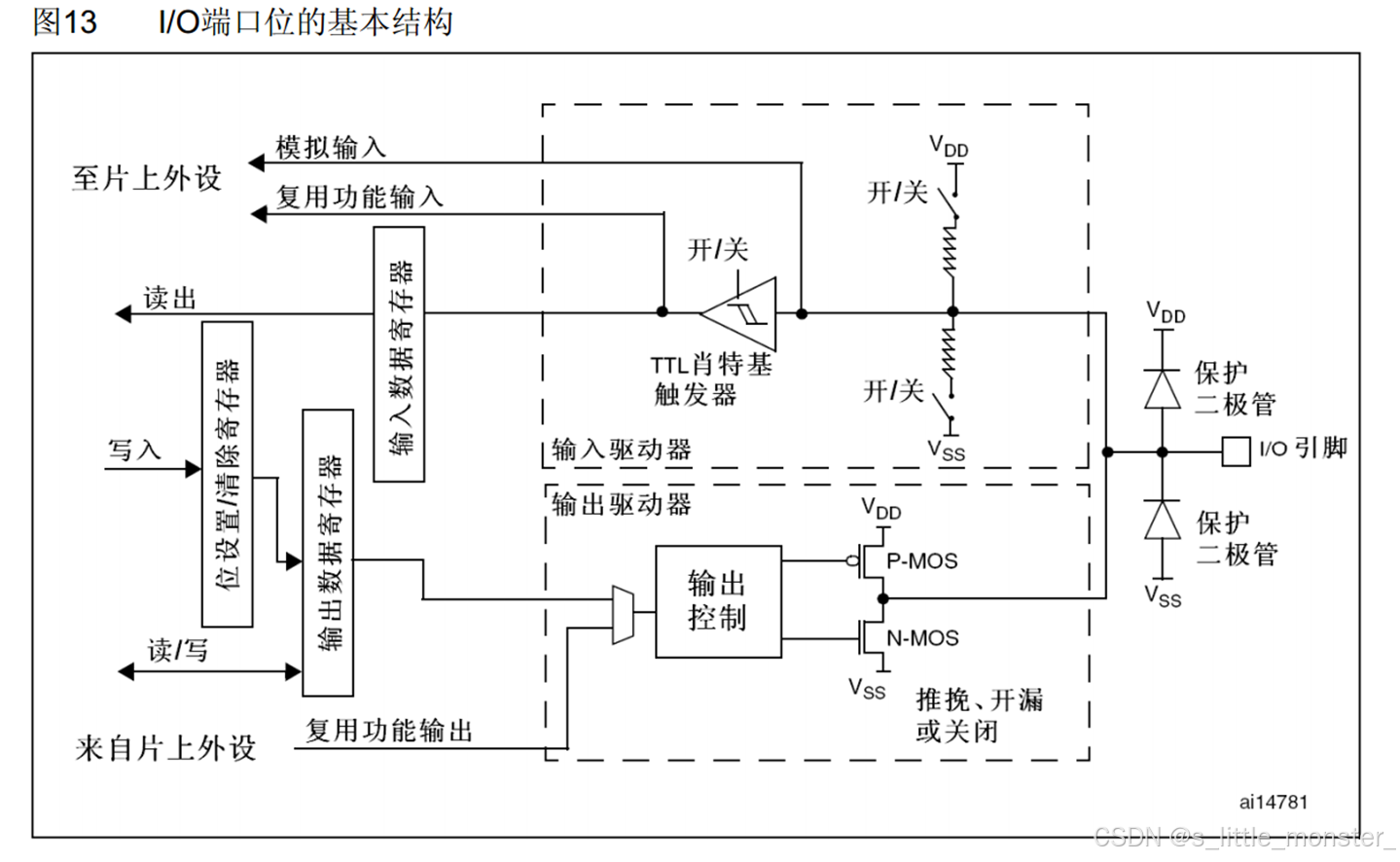

每一个GPIO口都由寄存器和驱动器组成,寄存器的每一位对应一个引脚,内核可以通过APB2总线对寄存器进行读写,输出(输入)寄存器写1引脚输出(输入)高电平,输出(输入)寄存器写0引脚输出(输入)低电平,因为STM32是32位的单片机,而引脚只有16个,所以寄存器只有低16位有对应的端口,驱动器用来增大驱动能力,寄存器只存储数据

三、输入输出模式

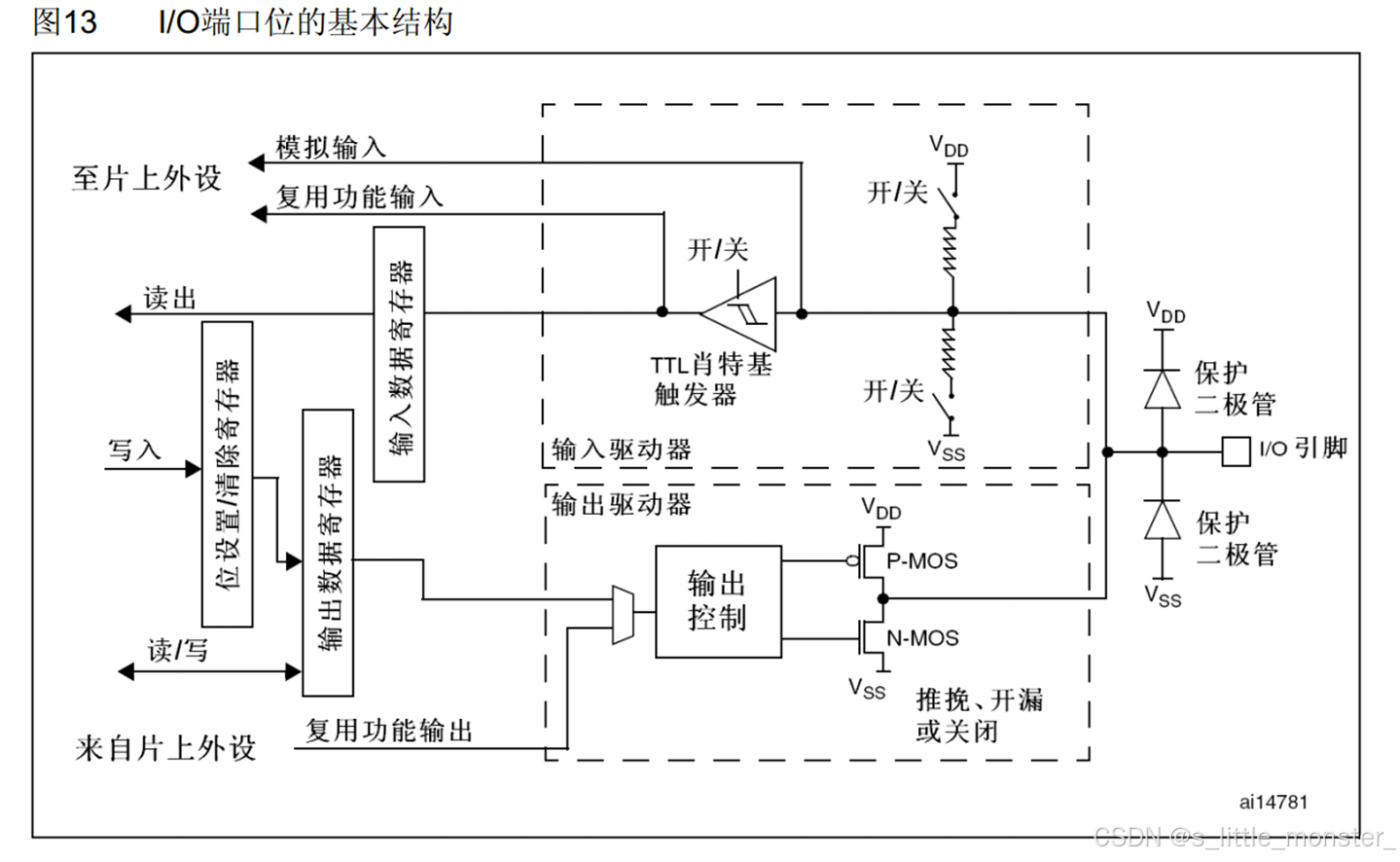

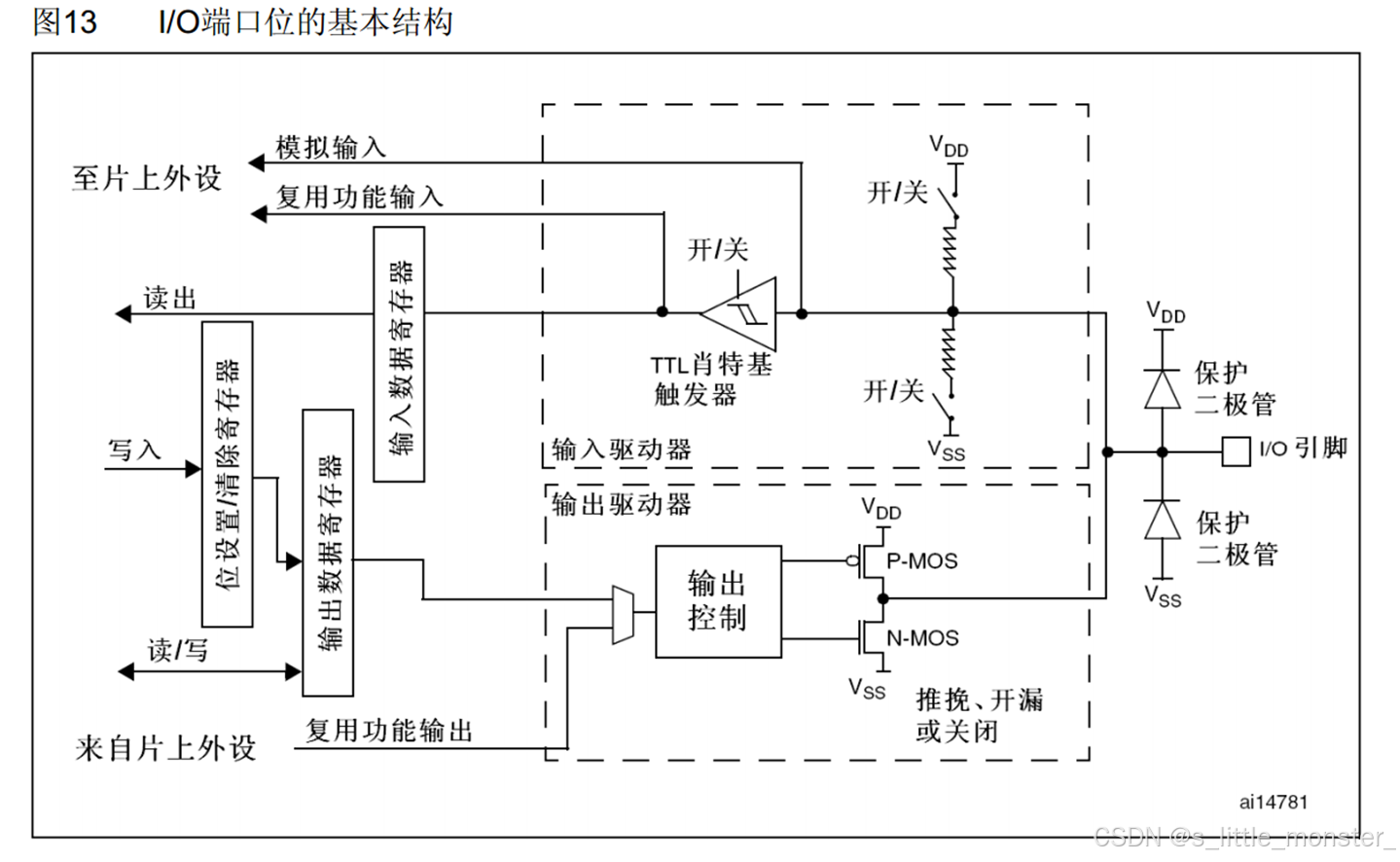

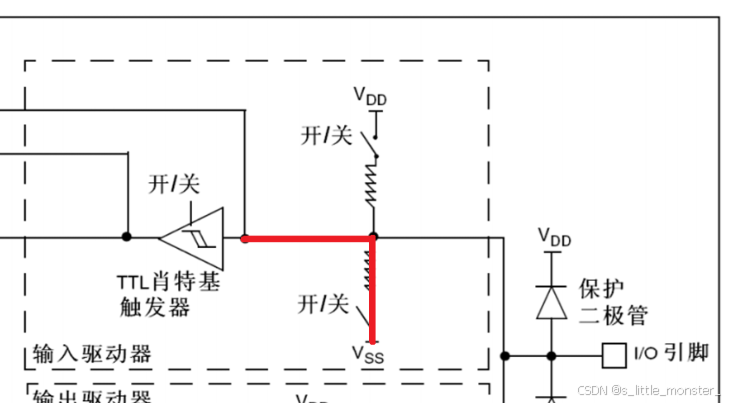

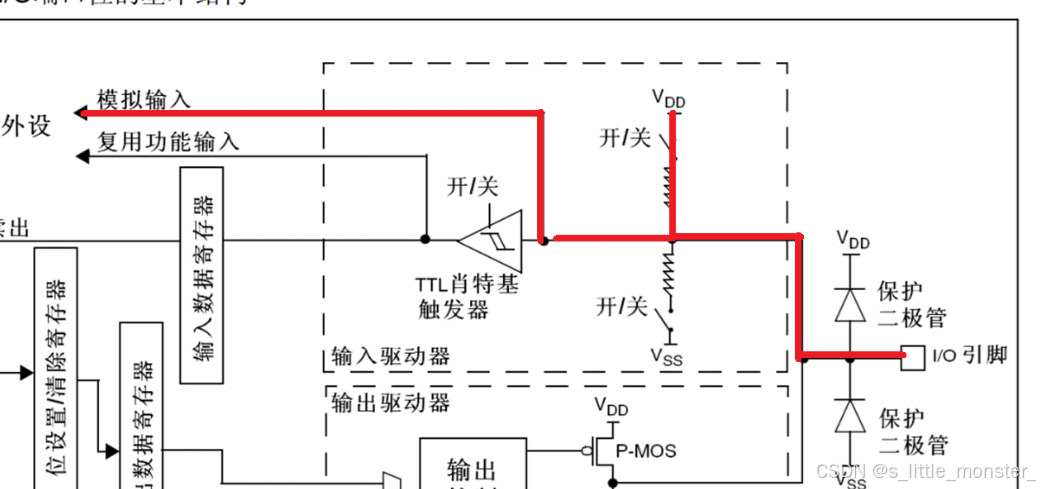

一个端口只能有一个输出,但可以有多个输入,所以在输入时,输出驱动器是关闭的,在输出时,输入驱动器是开启的

当最右边I/O引脚输入高于VDD电压时,上方保护二极管被导通,电流进入不到电路中

当最右边I/O引脚输入低于VSS电压时,下方保护二极管被导通,电流进入不到电路中

所以可输入的电流范围在VSS~VDD

不管是输入输出模式,都会涉及到数字数据与模拟数据的转换,输入部分是通过触发器和输入数据寄存器,输出部分是通过MOS管和输出控制

1、输入模式

上半部分是输入电路

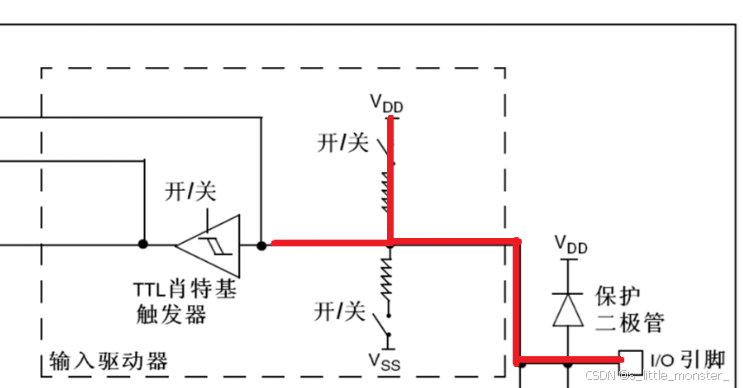

(1)上拉输入

上拉输入和下拉输入都是通过stm32控制的,可以自己决定上拉、下拉、浮空,并且上拉电阻和下拉电阻的阻值都很大,所以对电路的影响不是很大

上拉输入就是输入驱动器上方开关接通,此时内部连接上拉电阻,是一种默认为高电平的输入方式

在引脚输入高电平时,输入高电平,引脚输入低电平时,输入低电平:

引脚浮空(没有输入)时,输入高电平:

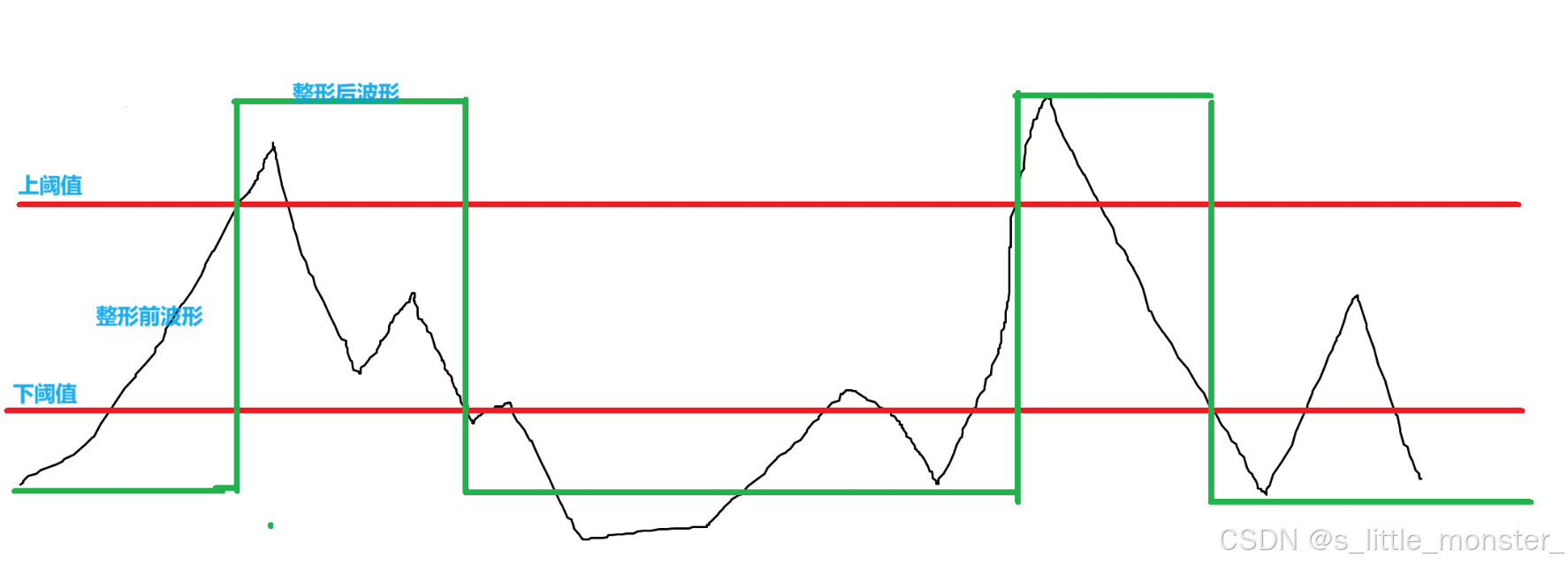

然后通过触发器,这里的触发器作用是给信号整形,因为在输入的过程中信号可能会失真,

触发器的作用:当数据高于上阈值时输出高电平,低于下阈值时输出低电平,在中间晃悠的不变化

然后这个数据就写入输入数据寄存器,由程序读取寄存器某一位的数据就可以知道端口的输入电平了

然后是复用功能输入这根线连接到其他需要读取端口状态的外设上,接收数字量

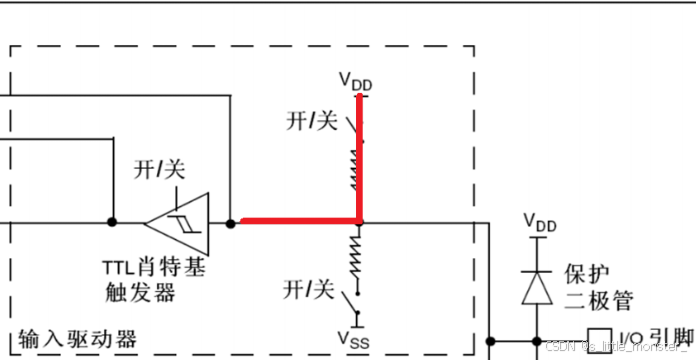

(2)下拉输入

下拉输入就是输入驱动器下方开关接通,此时内部连接下拉电阻,是一种默认为低电平的输入方式

在引脚输入高电平时,输入高电平,引脚输入低电平时,输入低电平:

在引脚浮空时,输入低电平:

(3)浮空输入

当上拉电阻和下拉电阻同时断开时,此时引脚处于浮空输入状态,此时输入高电平为高电平,输入低电平为低电平

当引脚处于浮空状态时,输入不确定,任意稍微的影响都有可能导致输入发生变化

小总结:不管是上拉输输入、下拉输入还是浮空输入,优先保证I/O口的输入如果为高电平(低电平),那么输入一定是高电平(低电平),变化只是在引脚处为浮空输入时有变化,我们一般使用浮空输入(多数情况下)和上拉输入(在有外界干扰的情况下),很少使用下拉输入

当使用浮空输入时最好使用一个连续的驱动,防止输入浮空

(4)模拟输入

接收模拟量,接到触发器前边,直接接收真实信号

2、输出模式

下半部分是输出电路

数字数据由输出数据寄存器或外设控制,输出数据寄存器控制输出直接接普通I/O口,外设控制输出则需要使用AFIO口,也就是复用功能IO口

输出数据寄存器还接一个位设置/清除寄存器,用来随时更改输出数据寄存器的某一位上的值

通过将位设置寄存器某一位改为1(不需置输出数据寄存器某一位为1的都为0),那么对应的那一位的输出数据寄存器的值就设置为1

通过将位清除寄存器的某一位改为1(不需置输出数据寄存器某一位为0的都为0),那么对应的那一位的输出数据寄存器的值就设置为0

(1)推挽输出

在推挽输出模式下,P-MOS管、N-MOS管均可以使用

MOS管就相当于一个开关,只是这个开关可以用来转换信号

数据寄存器为1时,上管导通,下管断开,引脚直接接VDD,输出高电平

数据寄存器为0时,上管断开,下管导通,引脚直接接VSS,输出低电平

在推挽输出模式下STM32对I/O口有绝对的控制权,高低电平的输出都是由STM32决定的

(2)开漏输出

在开漏输出模式下,P-MOS管不可用,N-MOS管可用

数据寄存器为1时,下管断开,此时引脚处为高阻态(无驱动能力)

数据寄存器为0时,下管导通,引脚接VSS,输出低电平(有驱动能力)

在引脚外接一个上拉电阻到5V的电源,当输出低电平时N-MOS接VSS,输出高电平时,上拉电阻将电压拉高至5V

(3)复用推挽输出

同推挽输出,不过是由外设控制的,不是数据寄存器控制的

(4)复用开漏输出

同开漏输出,不过是由外设控制的,不是数据寄存器控制的

EXIT外部中断

一、中断系统

在主程序运行过程中,出现了特定的中断触发条件,也叫中断源,使得CPU暂停当前正在运行的程序,去处理中断程序,处理完成后再返回原来的位置继续执行主程序

当有多个中断源同时申请中断时,CPU会先相应优先级更高的中断源,优先级是可以自己设置的

当一个中断程序正在运行时,又有新的优先级更高的中断源申请中断,CPU暂停当前中断程序,去处理该优先级更高的中断程序,处理完后返回该中断程序

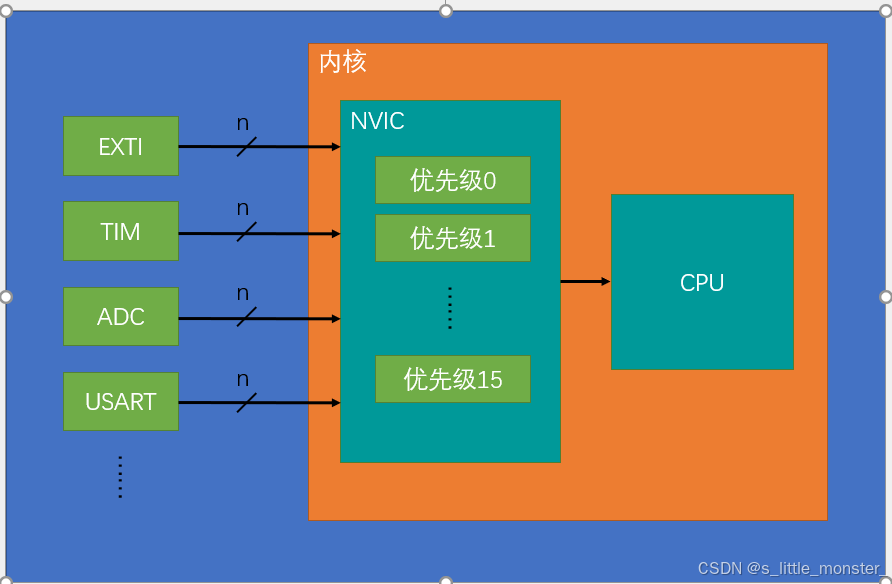

二、STM32中断

STM32使用NVIC统一管理中断,每个中断通道有16个可编程的优先级,优先级可再分为抢占优先级和响应优先级

1、NVIC的基本结构

在第一篇的博文里提到过外设表,外设表中的前两个是内核外设,NVIC就是一个内核外设,是用来管理中断的

每个中断都可以直接连接到NVIC上,NVIC通过分配优先级确定每个中断的先后顺序,它同一时间只会上交一个中断给CPU,让CPU处理中断

2、NVIC优先级分组

NVIC的中断优先级由优先级寄存器的4位决定,这4位可以分为高n位的抢占优先级和低4-n位的相应优先级,当抢占优先级和响应优先级均相同时按照中断号排队

抢占优先级和响应优先级分为五组

| 组别(位数以及取值范围) | 抢占优先级 | 相应优先级 |

|---|---|---|

| 0 | 0位,0 | 4位,0~15 |

| 1 | 1位,0~1 | 3位,0~7 |

| 2 | 2位,0~3 | 2位,0~3 |

| 3 | 3位,0~7 | 1位,0~1 |

| 4 | 4位,0~15 | 0位,0 |

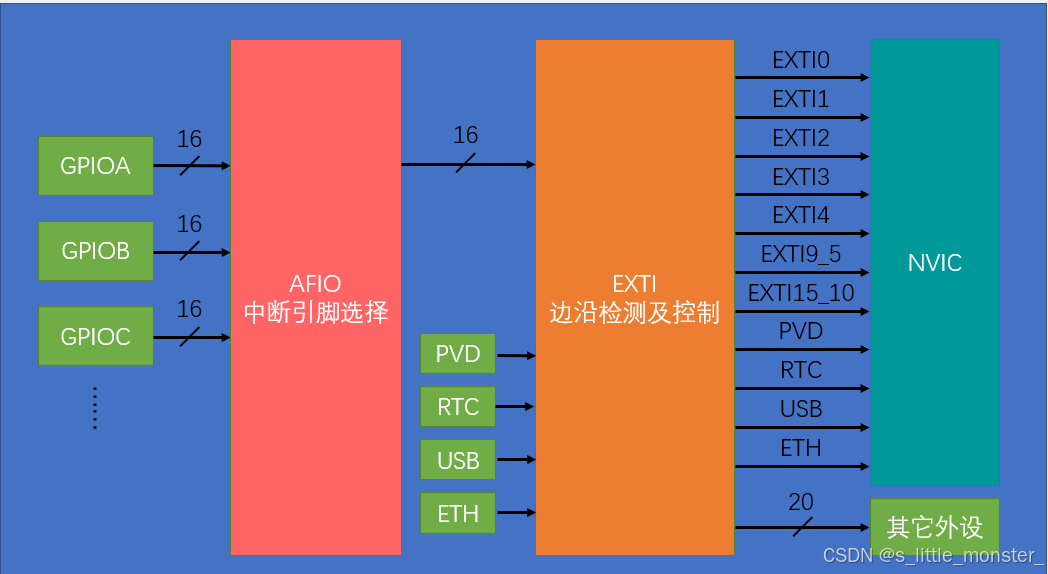

三、EXTI简介

EXTI可以监测指定GPIO的电平信号,当电平变化时,EXTI向NVIC发出中断申请

支持上升沿、下降沿、双边沿、软件触发

上升沿:电平由低电平变为高电平的瞬间触发中断

下降沿:电平由高电平变为低电平的瞬间触发中断

双边沿:上升沿和下降沿都可以触发中断

软件触发:程序代码执行触发中断

任意GPIO口都可以当做外部中断的引脚,但GPIO后边跟的数字相同不能触发中断,这个数字叫做pin,也就是说PA0和PB0不能同时做中断引脚,如果需要多个中断引脚的话pin值不能相同,原因是GPIO连接到AFIO上,起到中断引脚选择的作用,AFIO从pin值相同的通道里选择一个接到EXTI边沿检测及控制电路上,一共选择16个,也就是PA0、PB0、PC0只能有一个接到EXTI边沿检测及控制电路上,再加上PVD、RTC、USB、ETH四个特殊外设一共20个输入信号,经过EXTI分为两种输出:NVIC触发中断,其他外设触发事件响应

这里5 ~ 9、10 ~ 15整合到一条通道上了,一条通道上的触发同一个中断函数,在中断函数里还需要标志位才能区分到底是哪一个中断进来的

如果发生EXTI外部中断,可以发生中断响应或者事件响应,中断响应就是执行中断程序,事件响应就是操作外设而不触发中断

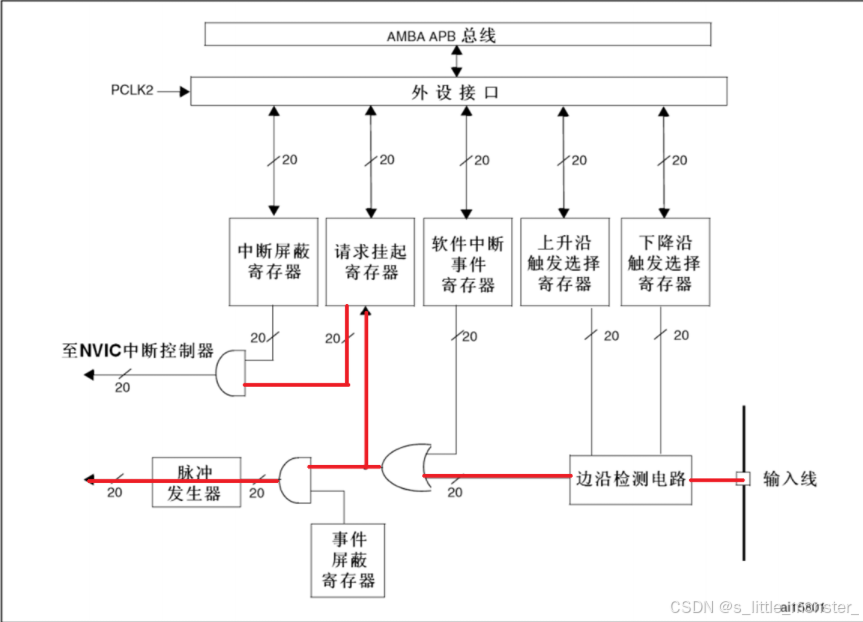

四、EXTI实现

上方是总线和外设接口,输入先遇到边沿检测电路,当上升沿时上升沿触发选择寄存器为1,下降沿时下降沿触发选择寄存器为1,它们两个只要有一个为1,边沿检测电路就可以为通路

之后遇到的这个元器件叫做或门,执行逻辑或的操作,当软件中断事件寄存器和边沿检测电路传来的数据中有一个为1则为1,全为0则为0

然后线路分为两路,左路对应的是事件响应,上路对应的是中断响应

左路连接的元器件叫做与门,执行逻辑与的操作,如果事件屏蔽寄存器和全为1则为1,有一个为0则为0,然后连接到脉冲发生器,脉冲发生器起到将数字信号转变为模拟信号的作用

上路连接请求挂起寄存器,可以通过读取该寄存器知道是哪个通道触发的中断,如果该寄存器置1,就继续往左走,与中断屏蔽寄存器连接到一个与门上,最后连接到中断控制器NVIC执行中断程序

今日分享就到这里了~