目录

本实验用到的breath.led工程如下:

链接:https://pan.baidu.com/s/1VQQSpEjppNuTi20chFGyFw

提取码:1234

1、什么是逻辑分析仪

逻辑分析仪是被设计用来在不同的时间点查看和分析数字信号电平的工具。它能够捕获并记录在特定时间点或者时间段内一组或多组信号线(也就是数字电路中的各种控制信号、数据信号等)的逻辑状态(通常是高电平或低电平,分别对应于数字信号的1和0)。这些记录下来的数据可以以图形或列表的形式展示,使得用户能够观察到信号在时间上的变化情况。

想象一下,有一所大房子里发生了一件神秘事件,而房子里的每个房间都有可能藏有线索。逻辑分析仪就像是一位侦探,他要通过检查房间(信号)之间的互动来解开谜团。在没有逻辑分析仪的情况下,这位侦探需要亲自进入每个房间(信号线),使用他的侦查工具(比如示波器)去手动检查每个角落寻找线索。这不仅耗时,而且效率低下,特别是当房子非常大,房间非常多(即需要检查的信号很多)时。

2、Vivado中的在线逻辑分析仪

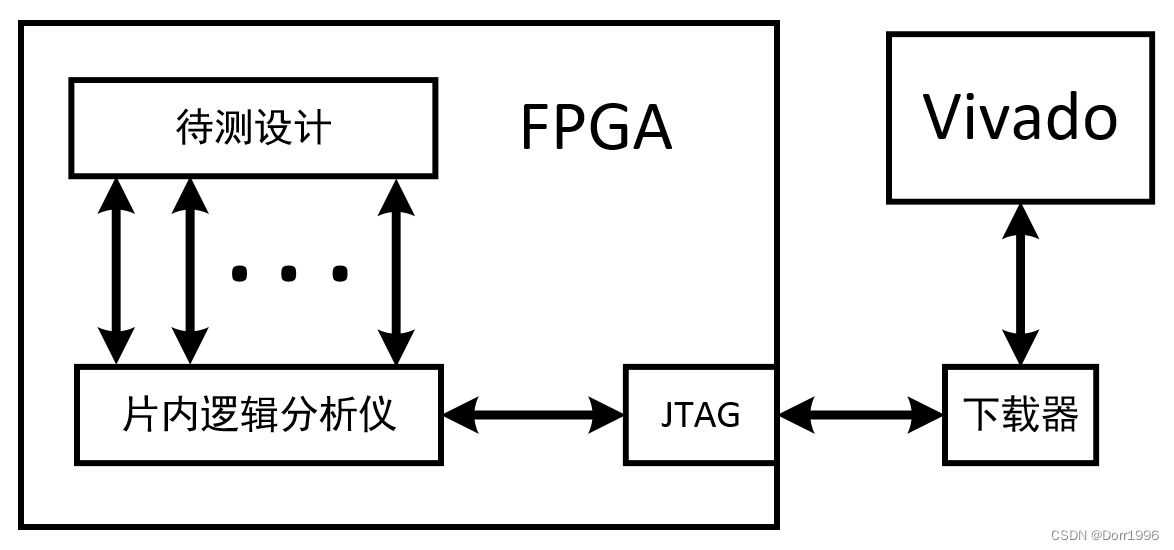

传统的 FPGA 板级调试是由外接的逻辑分析仪连接到 FPGA 的控制管脚,然后将内部信号引出至引脚 IO 上,进行板级调试。这种方法的缺点是我们需要一个逻辑分析仪,而逻辑分析仪一般价格都比较昂贵, 且对于需要测试几十个信号的时候,选择使用外接的逻辑分析仪就比较繁琐了。在线逻辑分析仪克服了以上所有的缺点,其借用了传统逻辑分析仪的理念以及大部分的功能,并利用 FPGA 中的逻辑资源,将这些功能植入到 FPGA 的设计当中。在线逻辑分析仪的应用原理框图如下图所示:

3、几种插入ILA的方法

在 Vivado 中,在线逻辑分析仪的功能被称为“集成逻辑分析器(Integrated Logic Analyzer, ILA)”,它以 IP 核的形式来加入到用户设计中。Vivado 提供了几种具有不同集成层次的插入 ILA 方法, 以满足不同 Vivado 用户群的不同需求: 第一种方法: 是直接在 HDL 代码中例化一个 ILA IP 核,也被称为“HDL 实例化调试探针流程”,这是集成层次最高的方法。ILA IP 核可以在IP Catalog(IP 目录)中找到,并对其进行配置,以符合所需的调试需求,这是最直接的方法,但其灵活性也较差。在调试工作完毕之后,还需要在 HDL 源代码中删除 ILA IP 核,然后重新综合以生成最终的比特流。 第二种方法: 是在 HDL 代码综合之前为想要观察的 reg 或 wire 信号添加“Mark Debug”综合属性,然后通过一个简单的“Setup Debug”向导来设置各个探针和 ILA IP 核的工作参数,工具会根据用户设置的参数,自动地生成各个 ILA IP 核,这个方法也被称为“使用 Debug 标记创建 ILA 调试环境”。用户设置的调试信息会以 Tcl XDC 调试命令的形式保存到 XDC 约束文件中,在实现阶段,Vivado 会读取这些 XDC 调试命令,并在布局布线时加入这些 ILA IP 核。在调试工作完毕之后,用户可以在 HLD 代码中删除之前添加的“Mark Debug”综合属性,并且在 XDC 文件中删除调试命令,然后再对设计进行重新编译,以生成最终的比特流。下面是举个例子能更好的理解这种方法: 【想象你正在搭建一座由乐高积木组成的小城市,而你想确保所有的街道灯在晚上都能正常亮起。在这个过程中,乐高积木城市代表你的FPGA设计,街道灯则代表你想要观察或调试的信号。标记街道灯(Mark Debug):在开始搭建之前,你决定给某些街道灯做上标记,这样你就能记住哪些是需要晚上检查是否亮起的。这相当于在你的HDL代码中为特定的信号添加“Mark Debug”属性,告诉自己这些是待会儿需要特别关注的部分。

设置检查工具(Setup Debug with ILA):你决定使用一种特殊的检查工具来晚上自动检查这些标记过的街道灯是否亮起。在设置这个工具之前,你需要确定检查哪些街道灯、检查的时间等等。这就像是通过设置向导来配置ILA IP核——一种内置在FPGA中的逻辑分析仪,用于检测和记录这些标记过的信号的状态。

自动搭建检查系统(Auto-generate ILA IP Core):根据你的设置,这个特殊工具自动在城市的各个角落安装了小型监测器,以便在晚上检查标记过的街道灯。在FPGA设计中,这相当于根据你的设置参数自动生成ILA IP核,并将它们植入到设计当中去。

进行检查(Debugging):到了晚上,你的检查工具自动运行,记录哪些街道灯亮了,哪些没亮。在FPGA设计中,你会启动ILA来观察那些标记过的信号在实际运行中的状态。

清理(Cleanup after Debugging):检查完成后,你决定拆除这些小型监测器,因为它们不再需要,且可能影响城市的美观。这就像在HDL代码中删除之前添加的“Mark Debug”属性,并从XDC文件中删除调试命令,然后重新编译设计一样,以确保最终的FPGA设计是干净、无多余调试模块的。

通过这个比喻,可以更好地理解在FPGA设计中使用“Mark Debug”和ILA IP核来创建调试环境的整个过程。】 第三种方法: 是在综合后的网表中,分别标记要进行调试观察的信号,然后通过一个简单的“Setup Debug”向导来设置各个探针和 ILA IP 核的工作参数,工具会根据用户设置的参数,自动地生成各个 ILA IP 核。这个方法也被称为“网表插入调试探针流程”。在此流程中,用户不需要修改 HDL 源代码,并且能够单独控制每个 ILA IP 核以及每个探针,这样就提供了很大的灵活性。用户设置的调试信息会以 Tcl XDC 调试命令的形式保存到 XDC 约束文件中,在实现阶段,Vivado 会读取这些 XDC 调试命令,并在布局布线时加入这些 ILA IP 核。在调试工作完毕之后,用户就可以在 XDC 文件中删除调试命令,然后再对设计进行重新编译,以生成最终的比特流。第三种方法与第二种方法的使用区别很小,只是标记信号的方式不同,第二种是在综合前标记,第三种是在综合后标记。 第四种方法: 是手动地在 XDC 约束文件中书写对应的 Tcl XDC 调试命令,在实现阶段工具会自动读取 这些命令,并在布局布线时加入这些 ILA IP 核。在调试工作完毕之后,用户还需要在 XDC 约束文件中删除这些命令,然后实现最终的设计。这种方法集成层次最低,一般不会使用这种方法。下面举个例子来让你更清晰的理解这种方法: 【 想象你正在组织一场生日派对,并计划在派对现场放置几个摄像头来拍摄精彩瞬间。这个过程中,派对现场代表你的FPGA设计,而摄像头代表ILA IP核(用于观察和调试的工具)。

手动安排摄像头位置(手写Tcl XDC调试命令):在派对开始前,你决定哪些地方需要放置摄像头来捕捉精彩瞬间。这就像是手动在XDC约束文件中写入Tcl调试命令,指定哪些信号需要被ILA IP核观察。你需要事先规划好,确保每个重要的时刻都能被记录下来。

摄像头开始工作(工具自动读取命令):派对开始时,摄像头根据你的安排自动拍摄。在FPGA的实现阶段,编译工具自动读取XDC文件中的调试命令,并在布局布线时将ILA IP核加入设计中,正如摄像头在你指定的位置自动记录派对的精彩瞬间。

派对结束,收拾现场(删除调试命令,实现最终设计):派对结束后,为了恢复家中的平常状态,你需要拆除并收回所有的摄像头。同样,调试工作完成后,你需要在XDC约束文件中删除之前添加的所有调试命令,并重新实现设计,确保最终的FPGA设计是干净、无多余调试模块的,就像派对现场被清理干净,恢复到派对前的状态一样。】

4、HDL 实例化调试探针流程

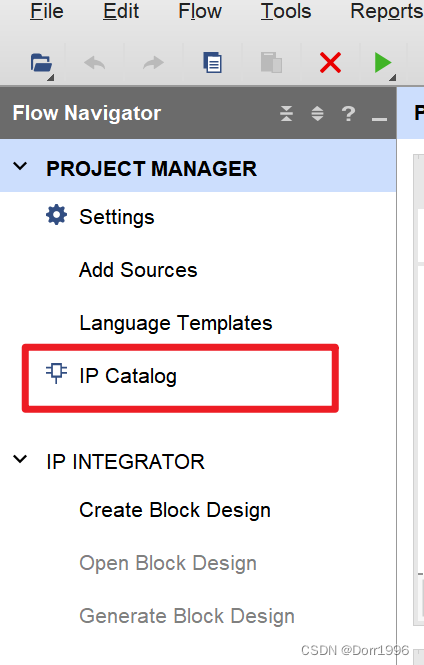

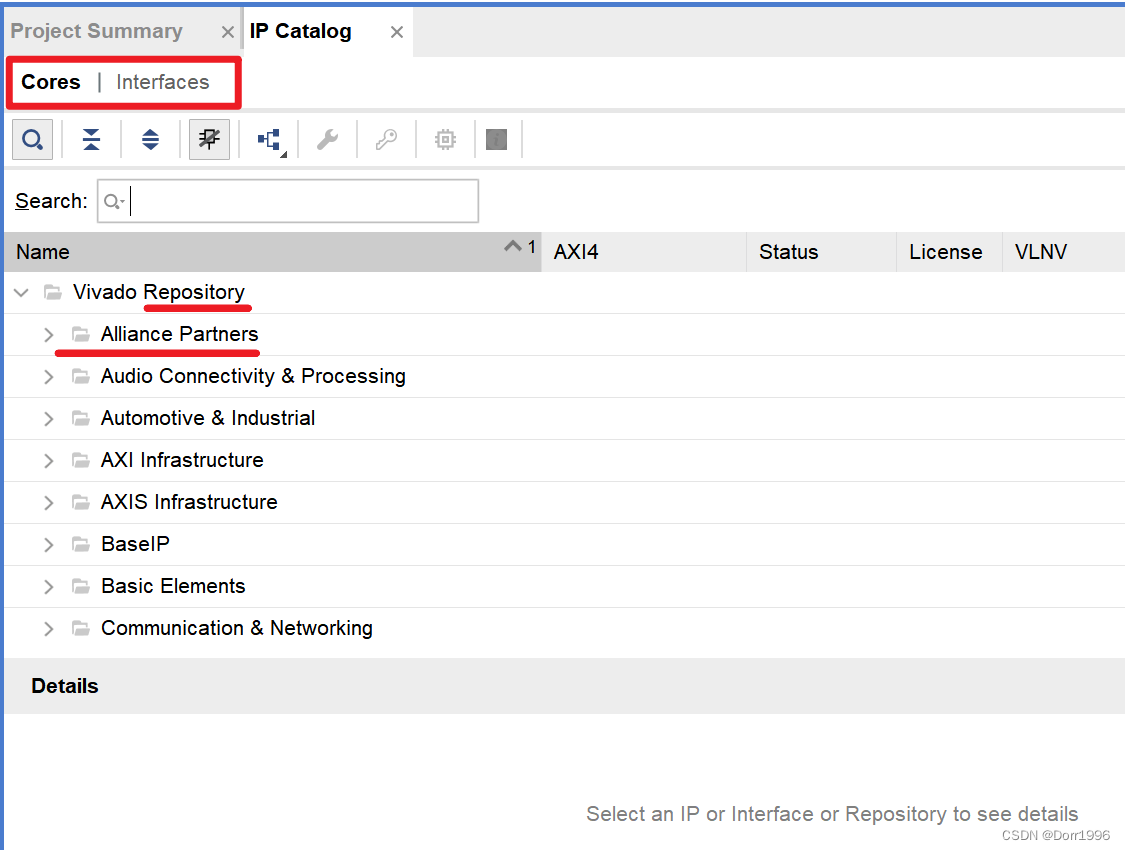

首先需要在 HDL 源代码中实例化 ILA IP 核。我们点击“Flow Navigator” 窗口中的“IP Catalog”按钮,如下图所示:

“IP Catalog”窗口打开了后如下图所示:

2、Cores(核心):Cores 是预先设计和验证的可重用 IP 核心。这些核心是在 FPGA设计中常用的功能模块,如处理器、数字信号处理器(DSP)、存储控制器等。它们经过优化和验证,可以轻松集成到您的 FPGA 项目中。这些核心提供了高性能和低功耗的解决方案,可以加速您的 FPGA 设计开发过程。 例如,Vcado 的 IP Catalog 中可能包含一个图像处理器核心,该核心能够对图像进行实时处理和滤波。另外,还可能包含一个视频编码器核心,用于将输入视频流压缩为更小的尺寸。

Interfaces(接口):Interfaces 部分列出了各种通用和标准的接口 IP。这些接口包括协议转换器、串行通信接口、存储接口等。使用这些接口 IP,您可以轻松地与其他设备或系统进行通信,并实现各种数据传输和控制功能。例如,Vcado 的 IP Catalog 中可能包含一个 HDMI 接口 IP,用于将 FPGA 连接到显示器或其他 HDMI 设备。另外,还可能包含一个以太网接口 IP,用于实现与网络

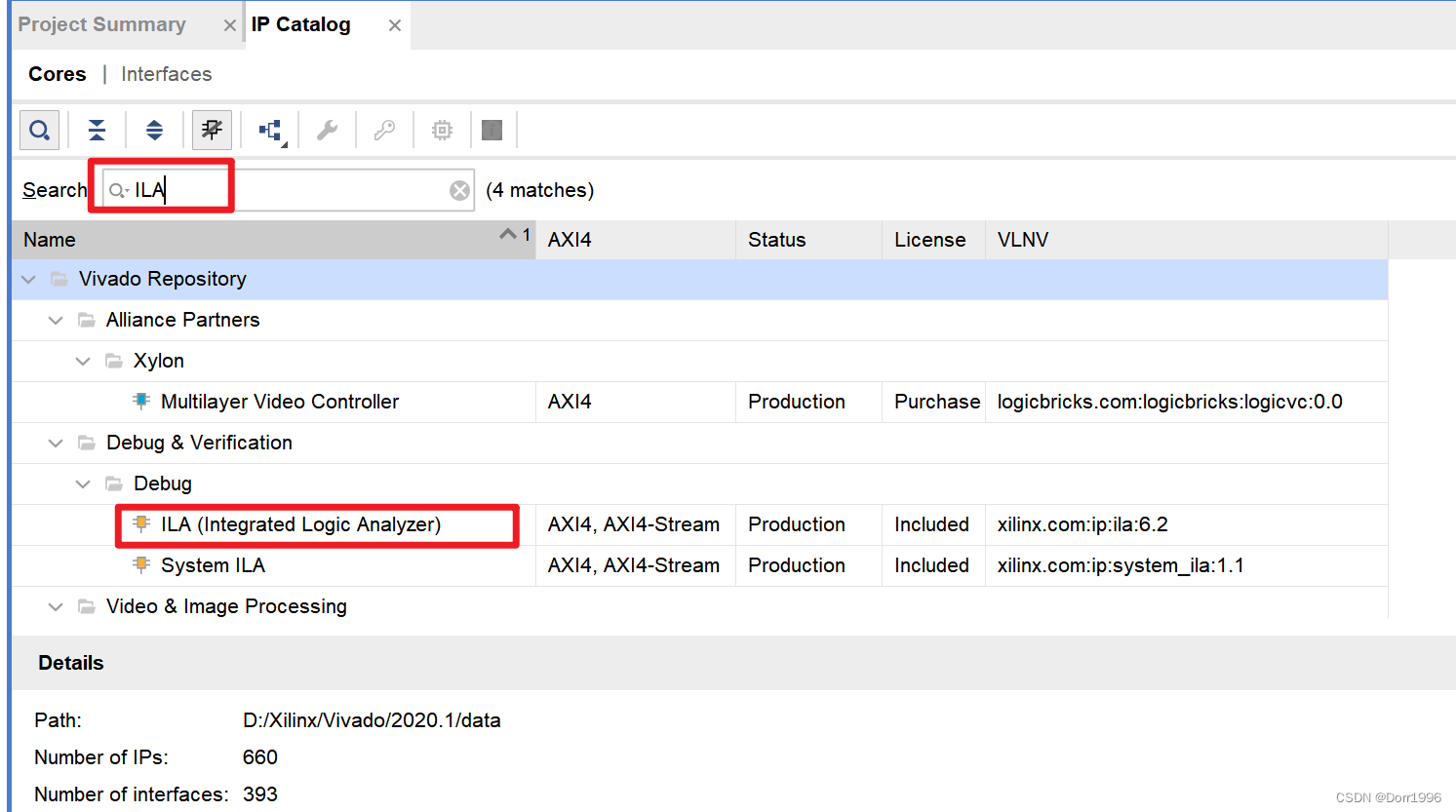

的通信。 3、在 Vivado 工具中的 IP Catalog 中,"Alliance Partners"(联盟伙伴)是指与赛灵思公司(Xilinx)建立合作关系的第三方公司或组织。 在搜索栏中输入“ILA”,这时 Vivado 会自动根据关键词搜索出相应的结果,我们双击“ILA (Integrated Logic Analyzer)”,如下图所示:

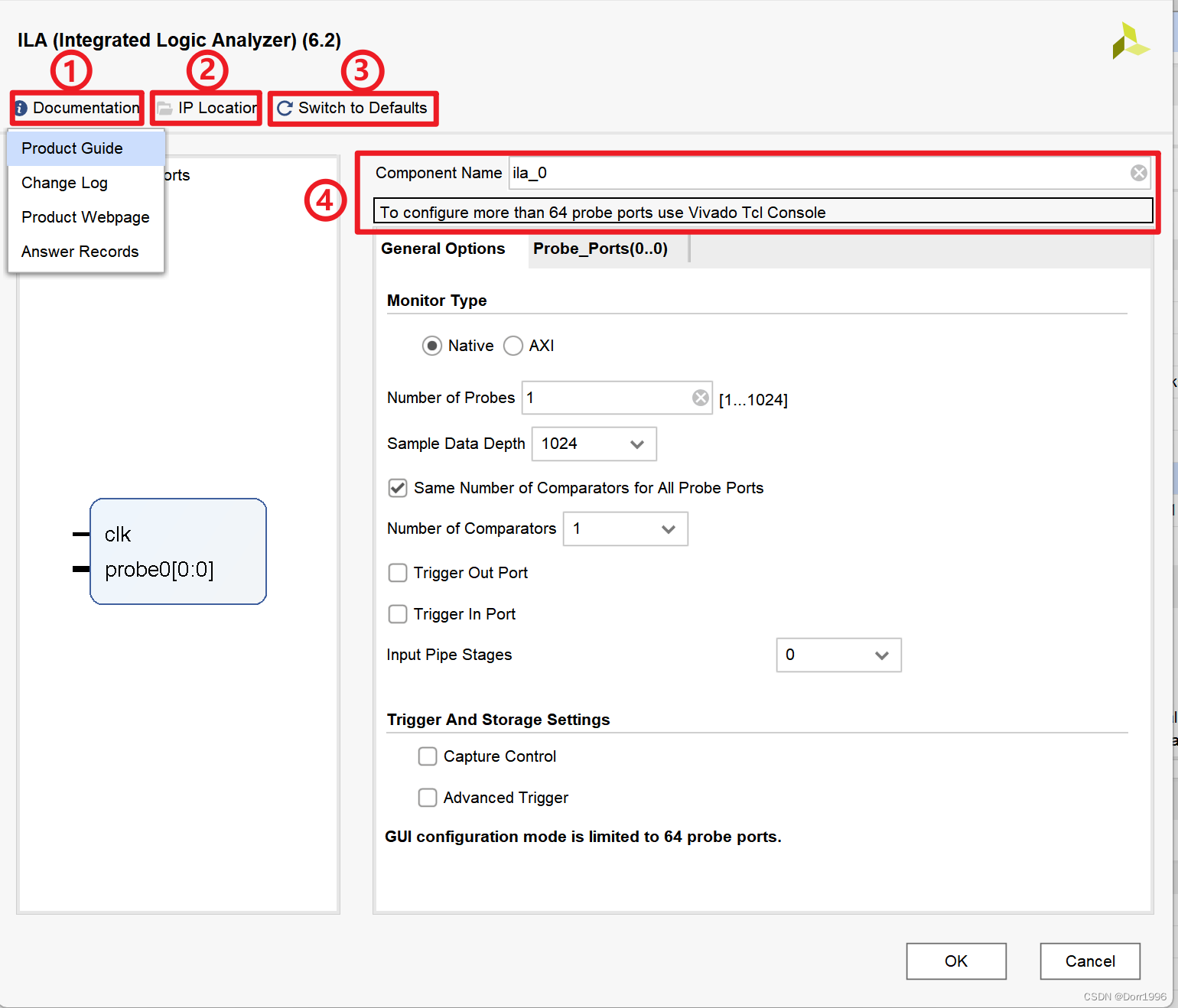

左上角工具栏主要有 Documentation、IP Location、Switch to Defaults 三个设置 ,分别为:

1、Documentation:IP 相关文档入口

①Product Guide:IP 手册查看入口,点击可自动跳转到 Xilinx 官方文档 DocNav 软件。

②Change Log:是 IP 版本更新记录。

③Product Webpage:是 IP 相关介绍的网页版。

④Answer Records:是与 IP 相关的 Xilinx 官方疑问解答记录网页。

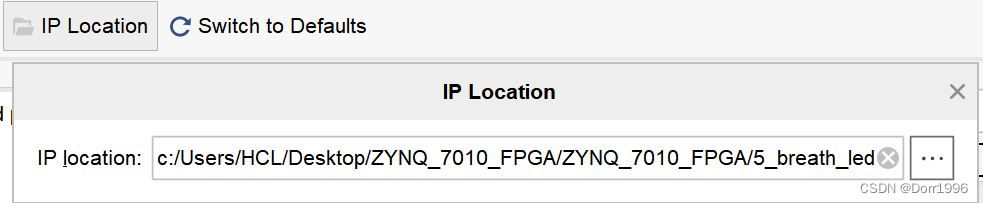

2、IP Location:设置 IP 的存放路径入口,点击出现如下图所示窗口,在窗口里可以通过点击“…” 更换存放路径。

3、Switch to Default:点击后所有的设置恢复到默认值。

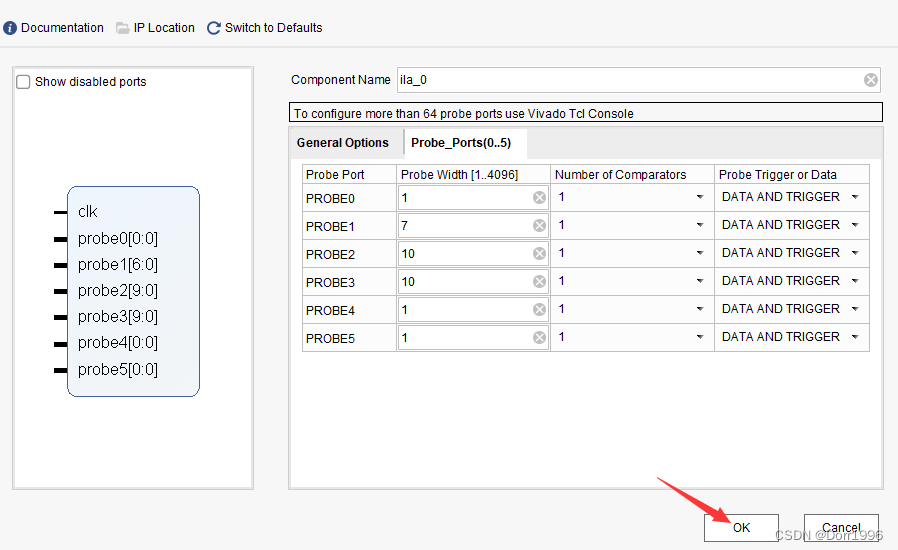

4、Component Name:设置生成 IP Core 的名称,下面有一个提示,该提示表示通过这个界面最多可以设置 64 个探针,如果想设置更多的探针需要使用 Tcl 脚本命令去设置。

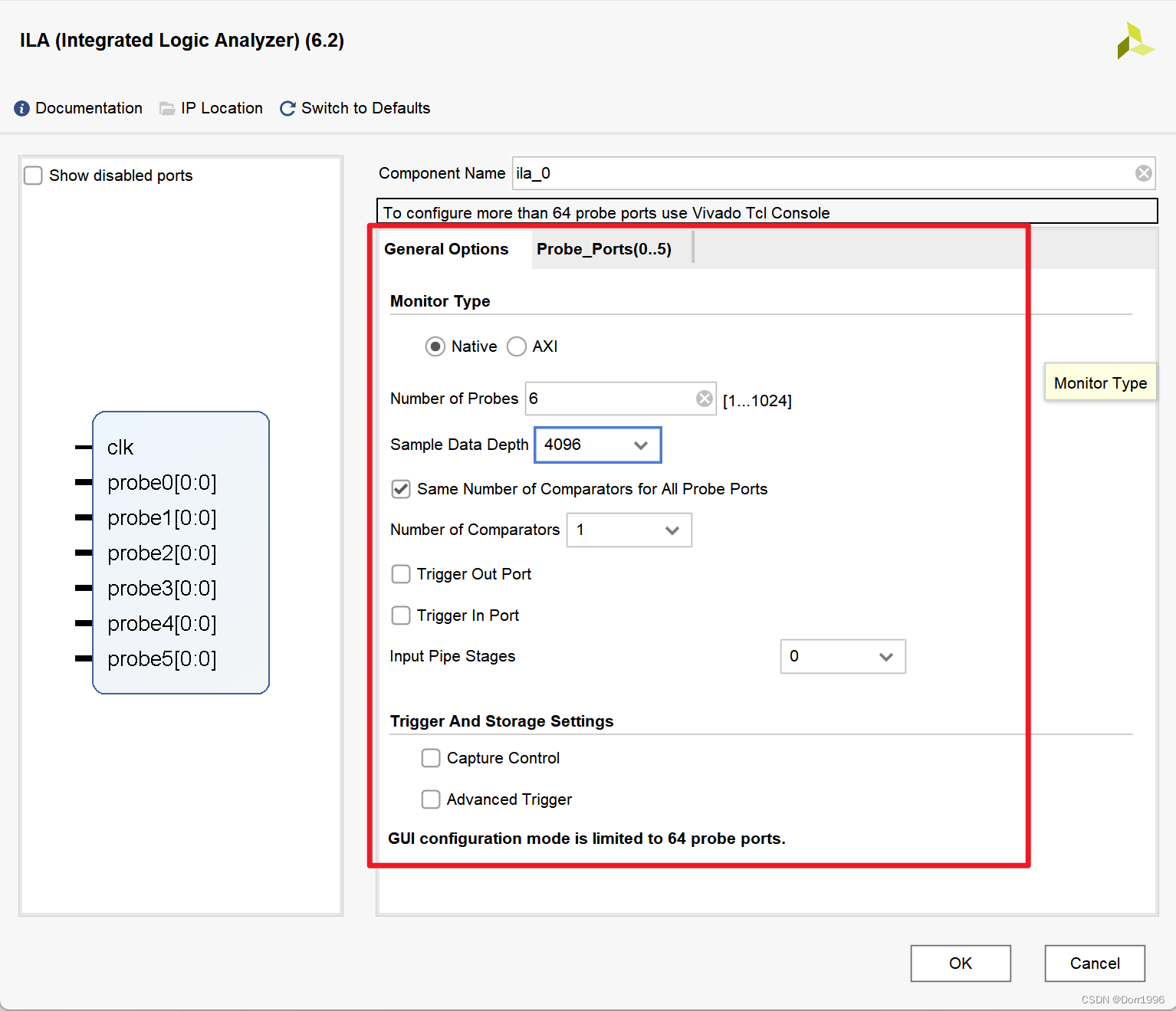

4-1 通用选项配置

将从上到下依次介绍参数的配置:

1、General Options(常规选项)

2、Monitor Type(监视器、探针类型):ILA 探针接口类型设置,ILA 探针接口有两种类型,Native模式更通用,允许用户自由选择任何信号进行分析,适用于各种信号和逻辑的调试。AXI模式专门用于监控和分析遵循AXI协议的通信,它提供了对AXI事务的高级解析功能,适用于调试基于AXI接口的数据传输问题。

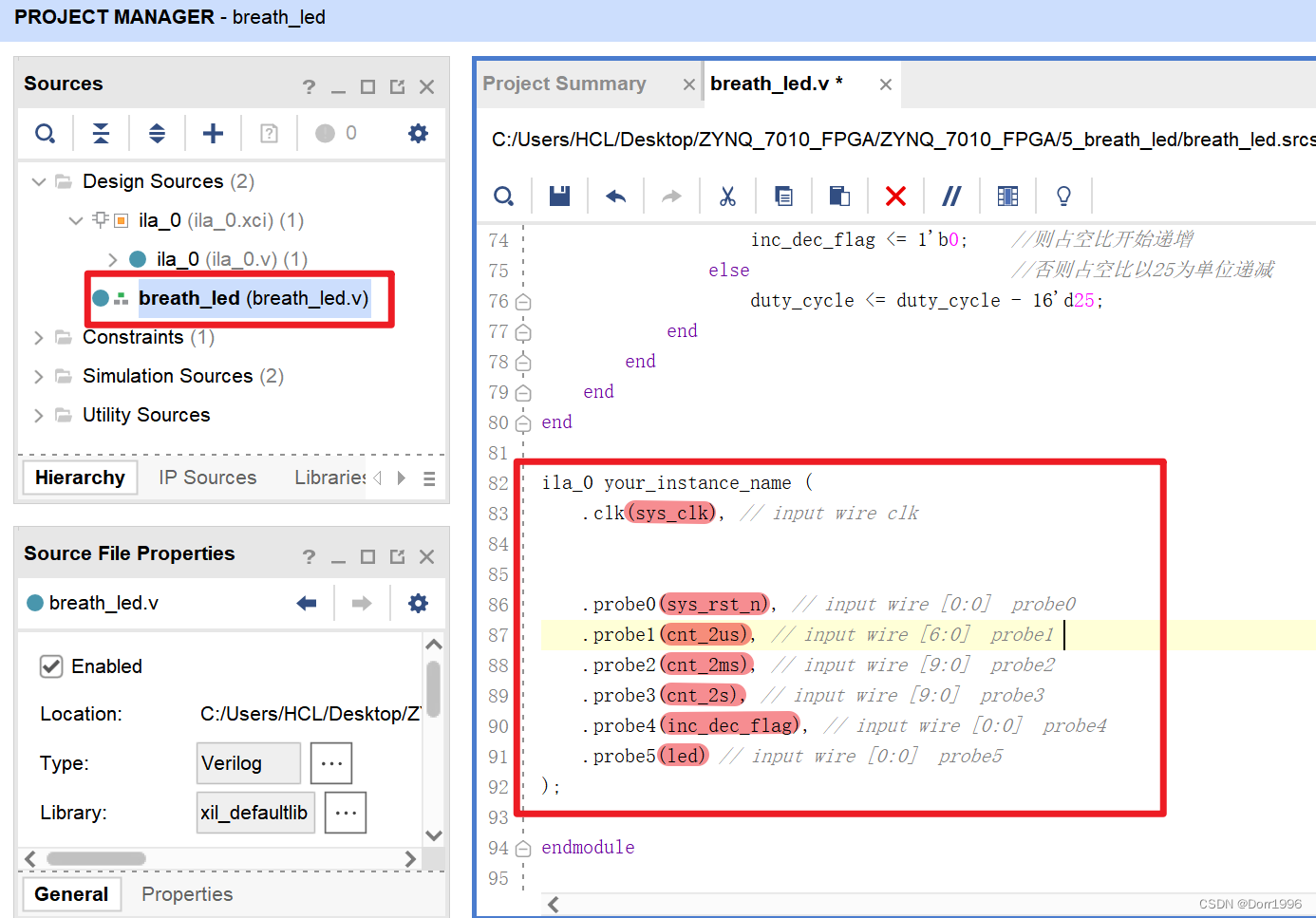

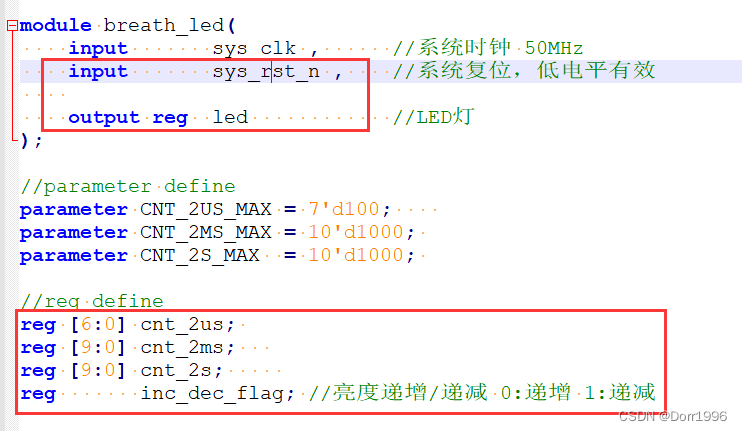

3、Number of Probes:探针数量设置,在 GUI 界面最大可设置 64 个,这个实验以呼吸灯实验代码为基础根据呼吸灯实验的需求,我们希望对 sys_rst_n、cnt_2us、cnt_2ms、cnt_2s、inc_dec_flag 和 led 信号抓取后进行线调试,所以这里需要设置探针数量为 6。

4、Sample Data Depth:采样数据深度,设置的数值越大,采样的数据越多,看到的波形数据越多,但是最终占用的资源也会越多,并不是设置的越大越好。“采样的数据越多,看到的波形数据越多”的原因是因为在数字电路调试过程中,逻辑分析仪(ILA IP核)通过对指定的信号进行采样来捕获信号在不同时间点的状态(例如,电平是高还是低)。这些采样点随后可以被用来重构信号在一段时间内的波形。

5、Same Number of Comparators for All Probe Ports:勾选此项意味着你决定所有探针端口将使用相同数量的比较器。这种设置在所有探测信号的重要性大致相等,且你希望对它们施加相同触发条件时很有用。不勾选该选项:意味着你可以为不同的探针端口设置不同数量的比较器。这在一些探针信号比其他信号更重要,或者需要更精细的触发条件控制时非常有用。不勾选时,“Number of Comparators”选项会消失,因为此时将需要为每个探针端口单独指定比较器数量。

比较器(Comparators)的作用:在ILA中,比较器用于触发(Trigger)条件的设置。比如,你可能想要在某个信号达到特定值时开始捕获数据,比较器就是用来检测这种条件是否满足的。简单来说,比较器用于比较探针信号的值与用户设置的期望值,当匹配时触发数据的捕获。

6、Trigger Out Port和Trigger In Port:"Trigger Out Port"(触发输出端口)是ILA IP核提供的一个输出信号,当ILA满足触发条件并开始捕获数据时,这个端口会发出信号。这个信号可以被用来触发其他的逻辑或调试模块开始执行某些操作。例如,你可以使用ILA的触发输出来启动另一个ILA核心或自定义逻辑开始数据的记录或分析。"Trigger In Port"(触发输入端口)正好相反,它是ILA IP核接收的一个输入信号。

7、Capture Control(捕获控制)和Advanced Trigger(高级触发):"Capture Control"涉及到如何管理ILA核心捕获数据的过程。这可以包括设置捕获的深度(即捕获多少个信号样本)、决定在触发事件发生之前或之后捕获数据的比例,以及是否连续捕获数据等。简而言之,"Capture Control"就像是一个高级的摄像机控制系统,允许你设置在特定事件发生时摄像机应如何响应——是只在事件发生后开始录制,还是在事件发生前后都记录一些画面,或者一直录制但只保存最关键的部分。Advanced Trigger"关注于定义触发捕获的条件。除了基本的触发条件(如某个信号变为高电平),高级触发还可以包括更复杂的逻辑,比如多个条件的组合(与、或、非逻辑),甚至是特定的信号模式匹配。

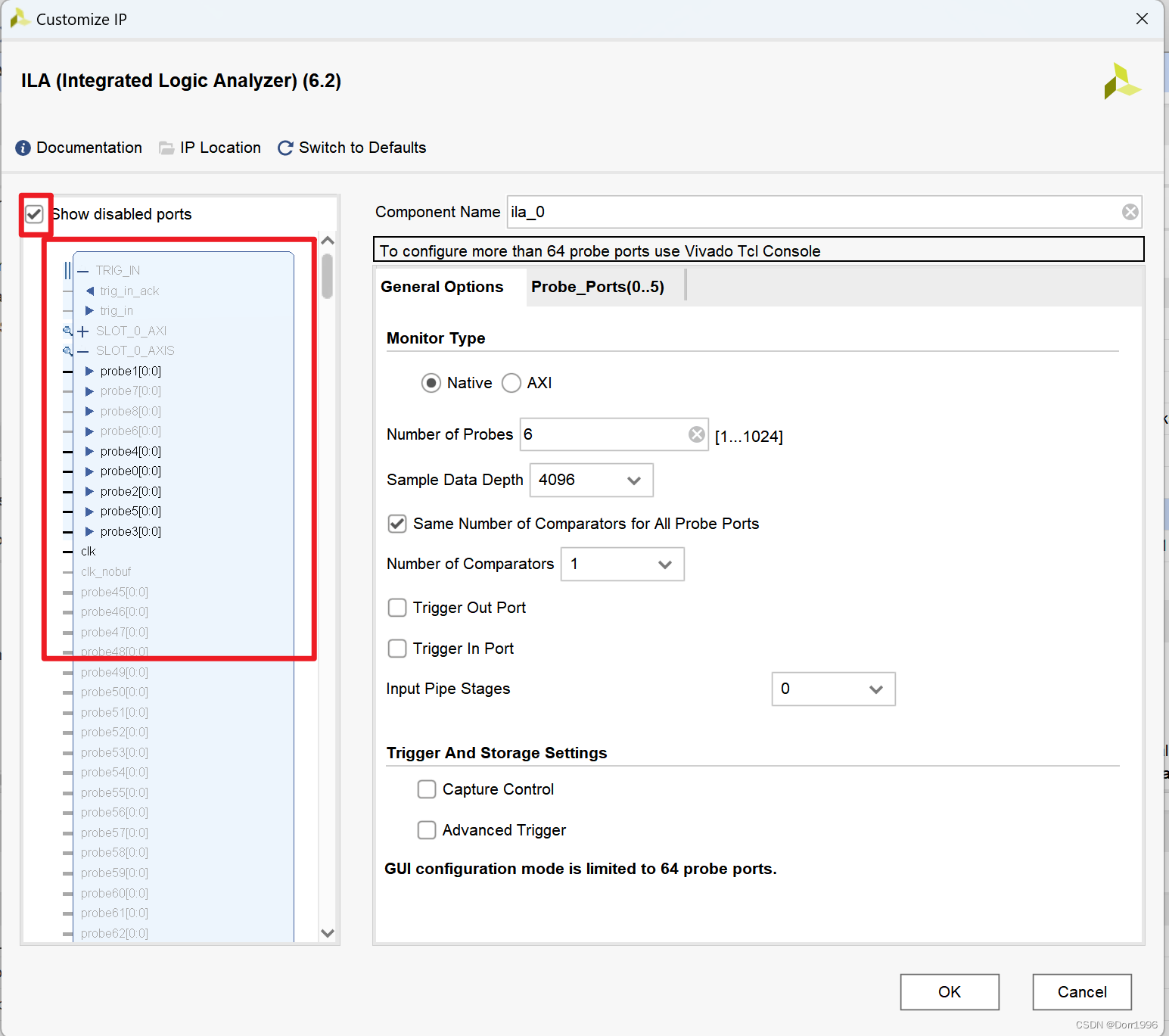

点击确定,配置完成后勾选Show disabled ports 选项,鼠标点击图 21.6.20 中的蓝色 ip 核,然后按住 Ctrl+滚动鼠标滚轮,通过放大可以查看详细引脚。

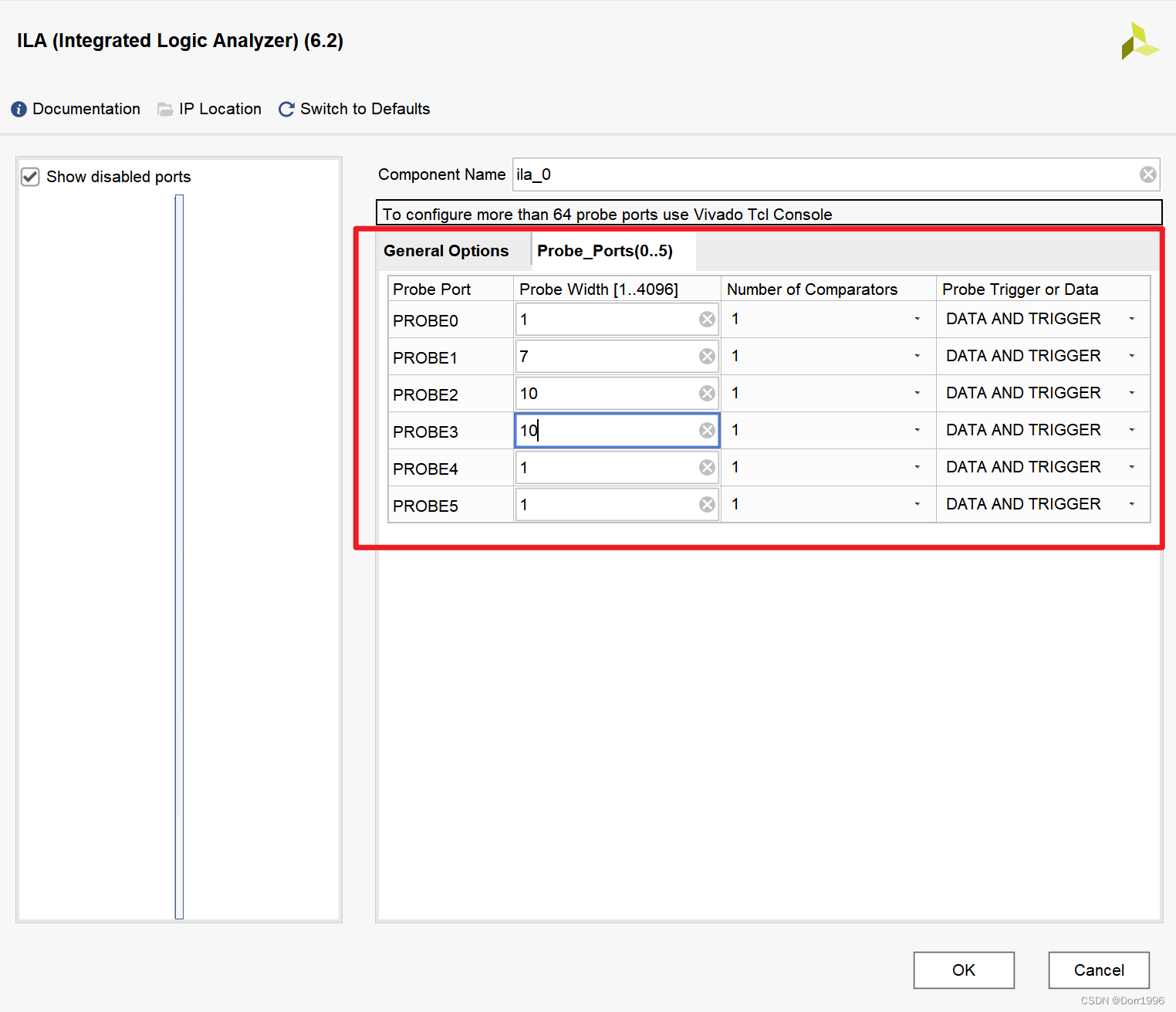

4-2 探针端口配置

4-3 ILA IP核的综合

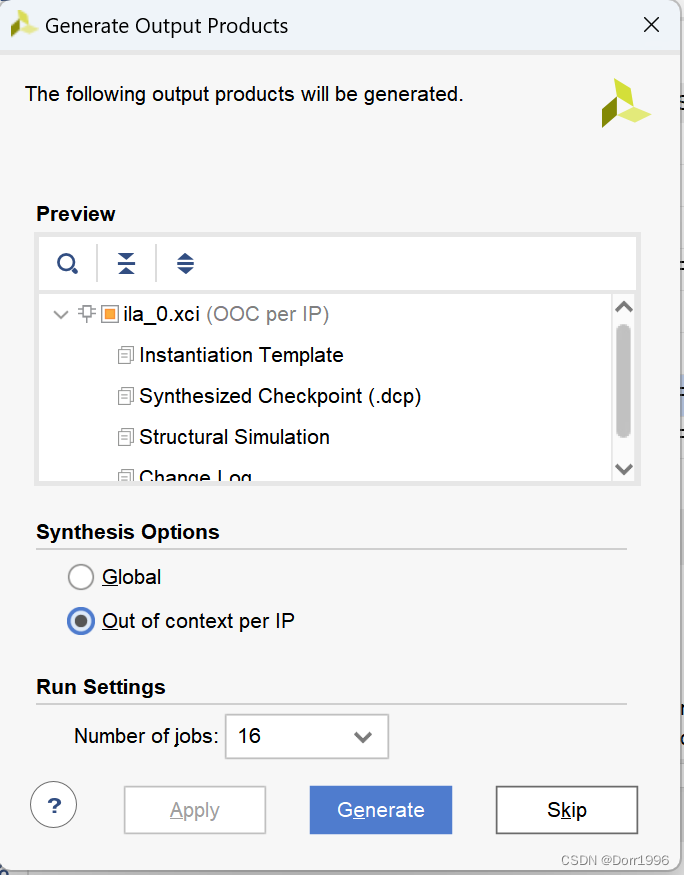

接下来弹出“Generate Output Products”对话框,直接点击“Generate”对该 ILA IP 核进行 OOC(Out-of-Context)综合了。如下图所示:

补充知识:

OOC(Out-of-Context)综合是一个在Vivado和其他硬件设计工具中使用的术语,它指的是将某个模块或IP核单独从整个项目或设计的上下文中提出来,进行独立的综合过程。这种方法允许设计者对特定的模块或IP核进行综合,而不需要每次都重新综合整个设计,可以显著提高开发和测试的效率。OOC 模块只会在综合顶层之前被综合一次,这样在顶层的设计迭代过程中, OOC 模块就不必跟随顶层模块而一次次产生相同结果的多余综合了。

OOC 综合完毕之后弹出下图所示窗口:

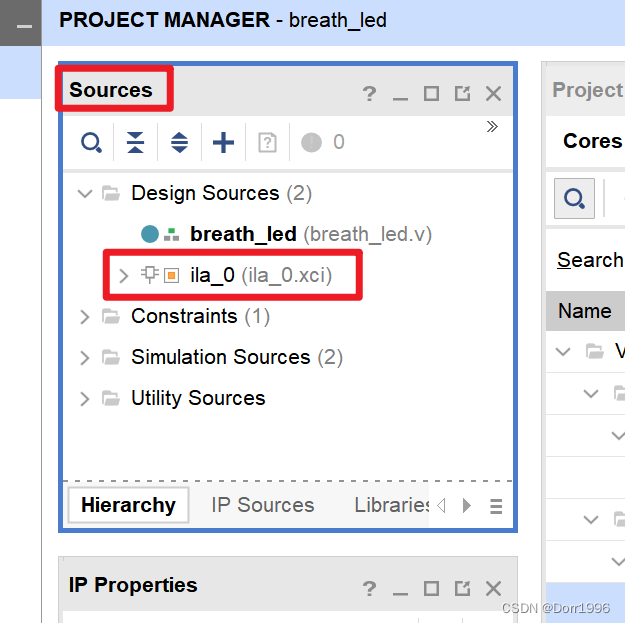

4-4 ILA IP核的例化

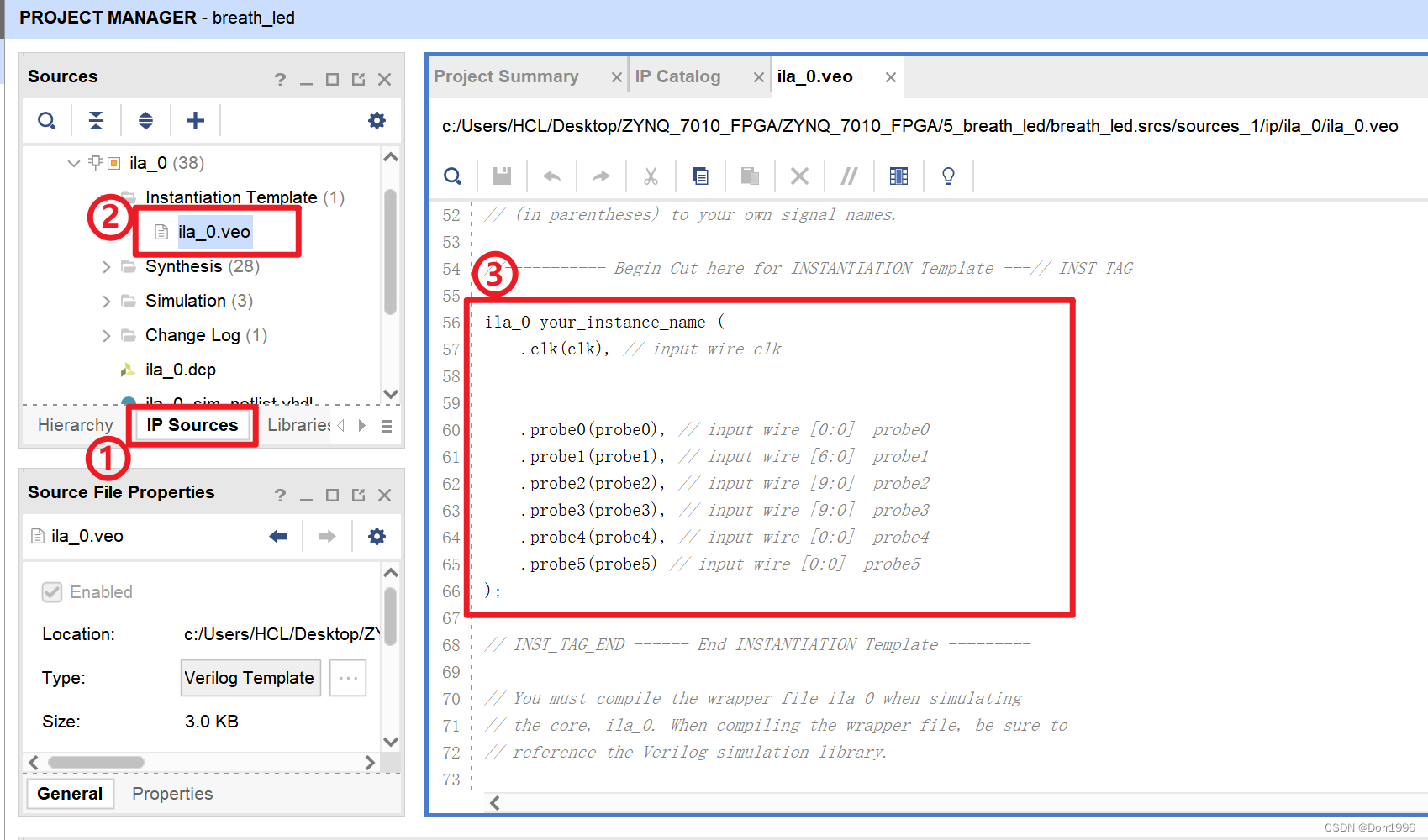

接下来将其例化到顶层的 HDL 代码中。双击“IP Sources”选项卡,找到ila_0.veo例化模板文本文件,找到例化模板的内容,如下图所示: