芯片原厂必学课程 - 第六篇章 - FPGA 设计篇

06-01 FPGA 芯片架构

新芯设计:专注,积累,探索,挑战

文章目录

引言

FPGA 芯片架构是非常重要的,如果你不了解 FPGA 芯片内部的详细架构,那么:

- 你就不了解自己的芯片设计的细节

- 你就不清楚如何有效安排各种资源

- 你就不熟悉如何合理例化内部模块

- 你就不了解如何权衡性能以及面积

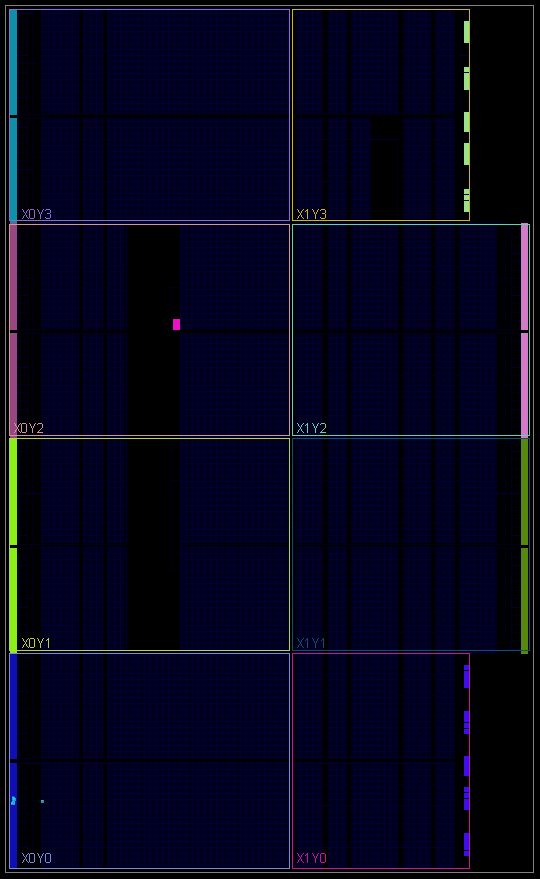

如下所示,基于 XILINX VIVADO 的 FPGA 开发而言,这是 PART 编号为 XC7A100TFGG484-2 的 FPGA 芯片内部的整体架构,通常是按照不同的时钟域进行划分的,对于时钟域,指的就是不同频率、不同相位的时钟所划分的不同区域

✅ 按照不同的工艺等级、器件速度及其对应的时钟源划分的话,可以划分成 8 个区域

✅ 按照不同的资源类型、功能部件划分的话,可以划分成 10 种资源

✅ 按照不同的模块划分的话,FPGA 芯片架构可以划分成 6 大模块,这也是本文的重点

NOTES:本文来自《芯片原厂必学课程 - 第六篇章 - FPGA 设计篇》技术专栏

🌏 一、输入和输出块(IOB:Input Output Block)

为了便于管理和适应各种电气标准,FPGA 的 IOB 被划分成了若干个组,英文是 BANK,每个 BANK 的接口标准由其接口电压 VCCO 决定,一个 BANK 只能存在一种 VCCO,而不同 BANK 的 VCCO 可以不同,只有相同电气标准和物理特性的端口才能够连接在一起,VCCO 电压一致是接口标准的基本条件

输入和输出块可编程为输入、输出和双向 IO 三种模式,类似于 ASIC 中的 GPIO 或者 PINMUX,这里也是通过 RTL 代码中信号的定义和 FPGA 引脚的约束即可实现

// 双向 IO 的设计: assign PAD = enable ? dout : 1'bz; assign din = (~enable) ? PAD : 1'b0; 🌏 二、可配置逻辑块(CLB:Configurable Logic Block)

在 XILINX 公司的 FPGA 器件中,一个 CLB 是由 2 个或者 4 个相同的 SLICE 和附加的逻辑组成的,SLICE 是 FPGA 的基本逻辑单元,SLICE 又分为 SLICE LOGIC 和 SLICE MEMORY,SLICE-L 和 SLICE-M 内部都各自包含了 4 个 6 输入查找表 LUT6、3 个数据选择器 MUX、1 个进位链 Carry-Chain 和 8 个寄存器 Registers,其中,查找表和选择器可以完成组合逻辑功能,寄存器可以完成时序逻辑功能

✅ 查找表:LUT6 类似于一个容量或者深度是 64 的 ROM(2^6 = 64),6 输入表示输入地址位宽为 6 比特,即存在 6 根地址线输入;对于查找表,目前主流 FPGA 都采用了基于 SRAM 工艺的 LUT 结构,所以 LUT 本质上就是一个 RAM,当用户通过原理图或 HDL 语言描述了一个逻辑电路之后,FPGA EDA 工具会自动计算逻辑电路的一切可能结果,列成一个真值表的形式,以一种输入到输出的映射关系写入 RAM,于是,输入信号的逻辑运算就等价于输入一个地址进行查表,索引地址的内容,然后输出即可,可以思考一下,单片机的程序计数器 PC 的取值不也是这样的嘛,CPU 的程序数据指令的载入不也是这样的嘛

✅ 选择器:这里的数据选择器通常在 FPGA 配置之后就定制下来了

✅ 进位链:通过基于进位链构成的加法器可以实现更快的加法功能

✅ 寄存器:可以配置成多种工作方式,比如 DFF 或 LATCH,同步复位或异步复位,复位高电平有效或复位低电平有效等等

SLICE-L 和 SLICE-M 的结构都是比较类似的,最大的区别在于是否以一个新的单元来代替 SLICE 中的查找表,这个新的单元可以配置为 LUT、RAM、ROM 或移位寄存器(SRL16 或 SRL32),从而可以实现 LUT 的逻辑功能,同时也能作为存储单元(多个单元组合起来可以提供更大的存储空间)和移位寄存器(提供延迟等功能)

其中,SLICE-M 中 LUT 的输入端读地址和写地址为 8 位,高两位可能是将 4 个 LUT 并联一起作为一个大的 RAM 或 ROM 时用,同时 SLICE-L 和 SLICE-M 的 LUT 均可设为 5 位或 6 位查找表

🌏 三、嵌入式块存储(BRAM:Block RAM)

BRAM 可被配置为 ROM、RAM、FIFO 等常用的存储模块,不同于分布式 RAM,分布式 RAM 主要由 LUT 组成的,不占用 BRAM 的资源,分布式 RAM 也可以被配置为 ROM、RAM、FIFO 等常用的存储模块,只是性能不如 BRAM,毕竟 BRAM 才是专用的,通常在 BRAM 资源不够用的情况下,才会去综合成分布式 RAM

BRAM 由一定数量固定大小的存储块构成的,综合成 BRAM 资源的话不占用额外的 CLB/LUT 逻辑资源,并且速度更快性能更高面积更少,综合消耗的 BRAM 资源只能是其块大小的整数倍,即使是单个比特综合成的 BRAM 也是要占用一个 BRAM 的

一个 BRAM 的大小为 36K 比特,可以分成两个小的 RAMB18 各自为 18K 比特,以及一个大的 RAMBFIFO36 为 36K Bits,例如,总共有 135 个 BRAM,又可以分为 135 个 RAMB36 或 270 个 RAMB18

🌏 四、互连线(Interconnect)

布线资源连通着 FPGA 内部的各个单元,连线的路径和工艺决定着信号在连线上的驱动能力和传输速率,FPGA 芯片内部具备丰富的布线资源,根据工艺器件、长短和位置的不同而划分成的 4 类不同的类别,如下:

- 第一类是全局的布线资源,是芯片内部全局时钟和全局复位的布线

- 第二类是长线资源,是完成芯片 BANK 间的高速信号、局部时钟和局部复位的布线

- 第三类是短线资源,是完成基本逻辑单元之间逻辑互连的布线

- 第四类是分布式的布线资源,是芯片内部专有时钟、专有复位和控制信号的布线

想要详细了解布局布线 Place & Route 的话,可以参考文章《数字 IC 笔试面试必考点(3)数字 IC 前端设计 + 后端实现》**

🌏 五、内嵌功能单元

内嵌功能单元主要指 DLL(Delay Locked Loop)、PLL(Phase Locked Loop)、DSP(Digital System Processing)、DCM(Digital Clock Manager)、和 CPU(Central Processing Unit)

DLL 和 PLL 具有类似的功能,可以完成时钟的高精度、低抖动的倍频或者分频,以及占空比调整和相移功能,XILINX 公司生产的芯片上集成了 DCM 和 DLL,Altera 公司生产的芯片上集成了 PLL,二者都可以通过 IP 核生成的方式进行管理和配置

DCM 是 FPGA 内部时钟资源的重要组成器件,提供了数字时钟管理和相位环路锁定,其主要有三个功能:消除时钟偏差(Clock De-Skew)、频率合成(Frequency Synthesis)和相位调整(Phase Shifting);DCM 的核心器件是延时锁相环 DLL 和锁相环 PLL,这是由一串固定时延的延时器组成的,每一个延时器的时延约为 30 皮秒,即精度为 30 皮秒(DLL 由数字电路实现,PLL 由数模混合电路实现)

对于时钟,最好不要对两个时钟通过一个与门或者或门之类的组合逻辑操作,这样的话容易产生毛刺,影响系统的稳定性,推荐基于 FPGA 内部的专用器件 BUFGMUX(原语 Primitives)或者 IP 核来对时钟进行操作

🌏 六、内嵌专用硬核

内嵌专用硬核是相对于底层嵌入软核而言的,底层嵌入软核指的是基于 RTL 代码实现的 IP 如 Micro-Blazer 软核,其等效于 FPGA 电路,内嵌专用硬核指的是 FPGA 处理能力强大的硬核如 ARM Cortex-A9 的硬核,其等效于 ASIC 电路

至于内嵌专用硬核的特点,主要是为了提升 FPGA 性能,例如,主流的 FPGA 中都集成了专用的 DSP 乘法器或者 FMC 等等