阅读量:0

1、概述

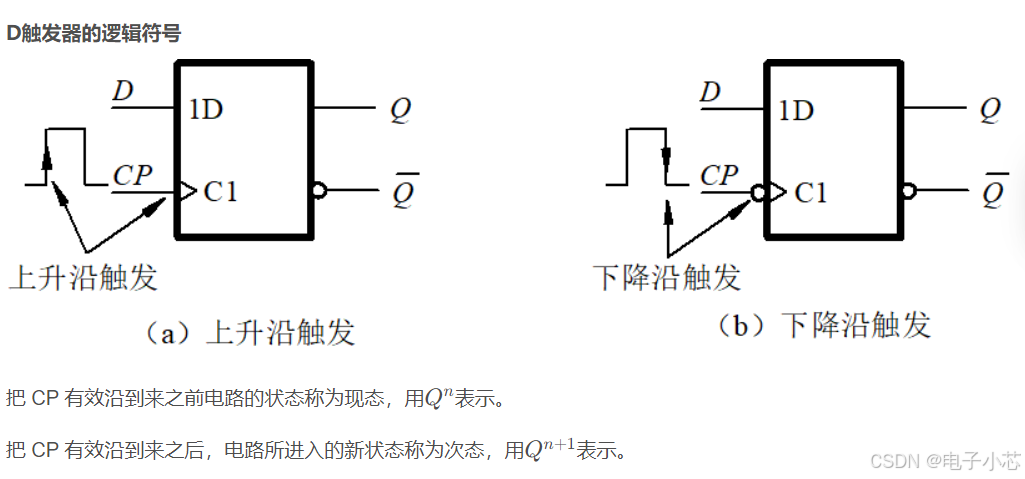

锁存器和触发器有时组合在一起,因为它们都可以在其输出上存储一位(1或0)。与锁存器相比,触发器是需要时钟信号(Clk)的同步电路。D 触发器仅在时钟从0 到 1(上升沿)或 1 到 0(下降沿)时存储来自 D 输入的新值。我们在FGPA开发中对D触发器进行设计,不同考虑其内部结构,只要根据需求实现当时钟信号上升沿或者下降沿到来时,输出的值等于输入D的值就行。

2、测试文件的编写

因为D触发器设计非常简单,这里就不多做介绍,直接上代码,新建一个d_ff.v文件(这里建立的.v文件必须和模块名一致,否则会报错):

//异步复位的D触发器 module d_ff( input clk, input rst_n, input d , output reg q ); always@(posedge clk or negedge rst_n) begin if(!rst_n) q<=1'b0; else q<=d; end endmodule这里开始用到了时序电路,所以在后面的仿真中我们需要注意时序电路慢一拍输出的特性。

3、测试文件的编写

新建一个d_ff_tb.v文件,如下:

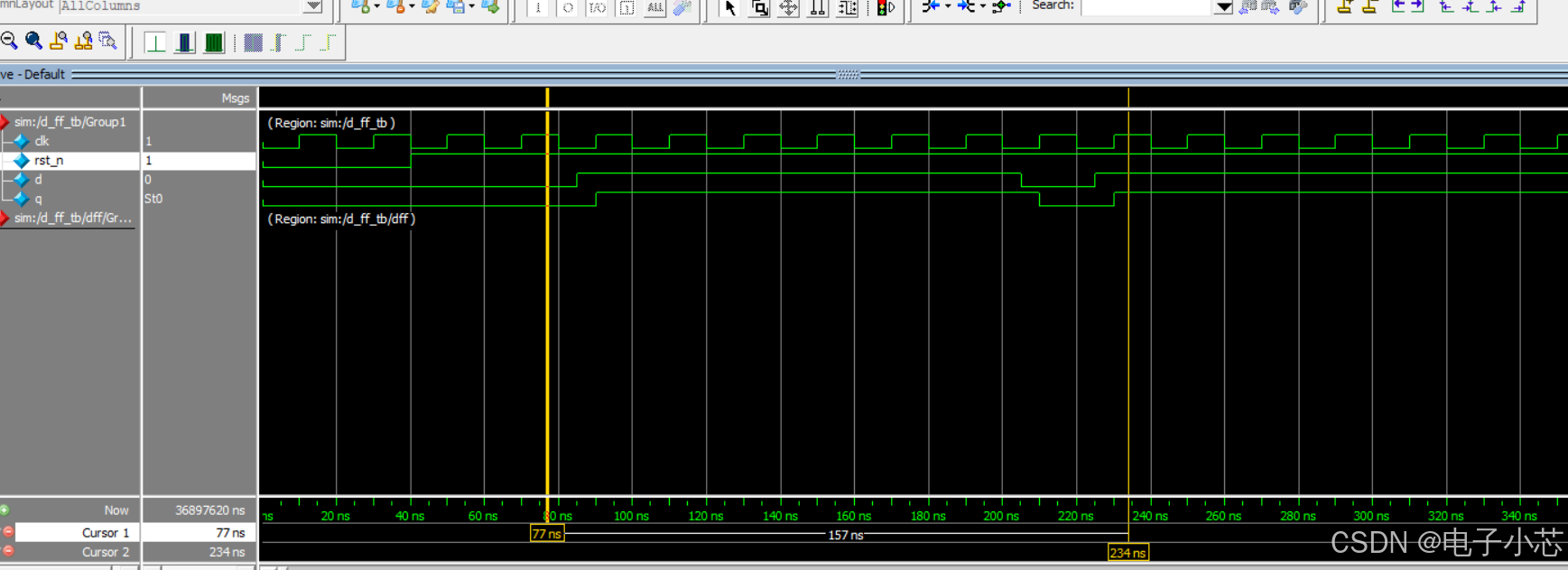

//定义时间尺度 `timescale 1ns/1ns module d_ff_tb; reg clk; reg rst_n; reg d; wire q; d_ff dff( .clk (clk), .rst_n (rst_n), .d (d), .q (q) ); //时钟 parameter CLK_CYC = 20; initial clk=1'b0; always #(CLK_CYC/2) clk=~clk; //复位 initial begin rst_n = 1'b0; #(CLK_CYC*2); rst_n = 1'b1; end //激励 initial begin d=1'b0; #(CLK_CYC*3); #5; repeat (10)begin d=$random; #(CLK_CYC*1); end end endmodule 这里在激励信号产生的代码中在延时3个周期#(CLK_CLY*3)之后再延时5ns——#5的目的是错开时钟上升沿,模拟实际输入,便于观察慢一拍输出的特性。

4、波形图仿真

在modelsim中进行波形仿真结果如下:

在波形图中我们可以看到当复位信号和时钟上升沿信号错开时,输出也是慢一拍输出,最大程度的还原了真实情况的输出,当复位信号拉高之后,时钟上升沿到来Q的值立马发生变化变成D的值,一致保持当前状态一致持续到下一个时钟信号上升沿。