平台:vivado2018.3

芯片:xcku115-flva1517-2-i

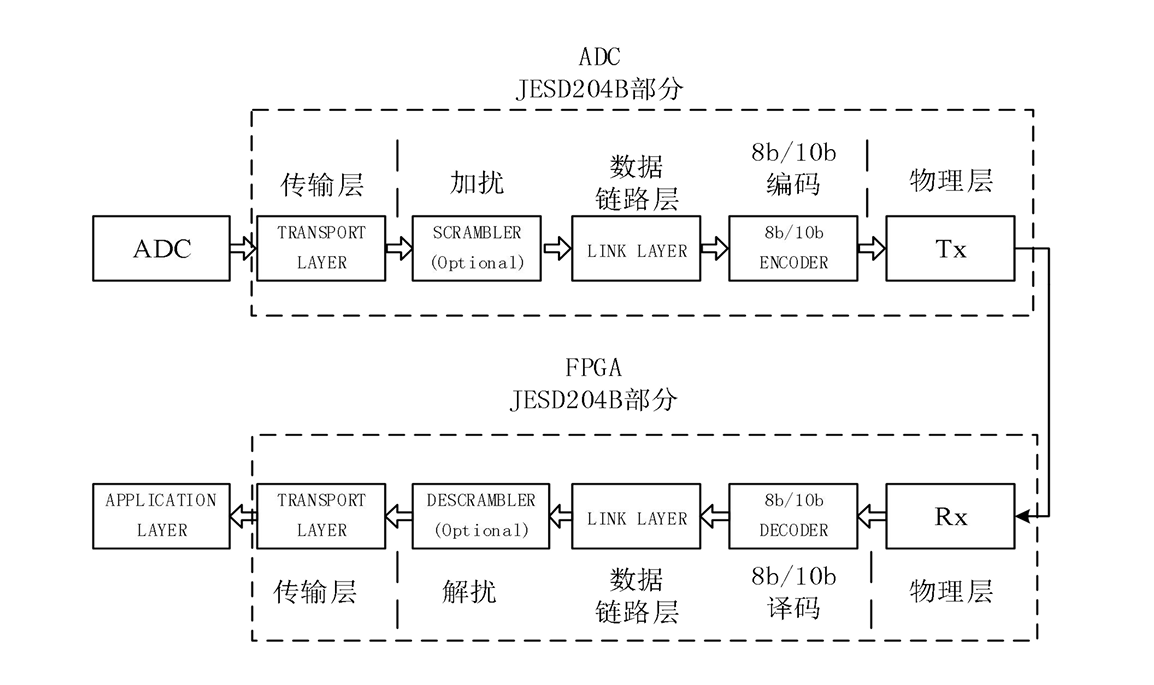

场景:在高速ADC和DAC芯片中,有使用源同步的时钟和数据同步传输的方式,但是需要在逻辑内部对其进行校准。如果使用jesd204b接口传输数据,设计人员不需要了解复杂的校准流程,只需要向该接口写入数据,或者从该接口读出数据。

IP手册下载地址:

IP介绍

LogiCORE™ IP JESD204 内核实现了一个 JESD204B 接口,在使用 GTX、GTH、GTP 或 GTY(仅限 UltraScale 和 UltraScale +)收发器的 1 至 8 条通道上支持 1 至 12.5 Gb/s(1)的线路速率。有关每个器件和系列所支持的最大线路速率,请参阅器件数据表。JESD204 内核可以配置为发送或接收,并且可以使用多个内核来实现需要超过 8 条通道的链路。

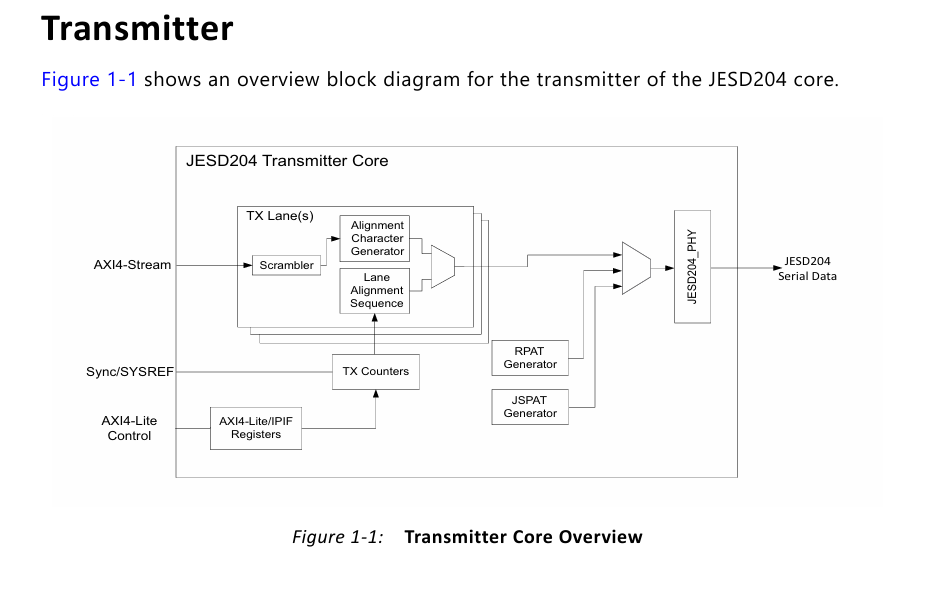

发射机(对应DAC)

数据流从axi_stream接入,经过加扰对齐操作后的数据进入phy中通过串行形式发送出去。同时外部的sync和sysref同步信号对加扰对齐操作进行校准。

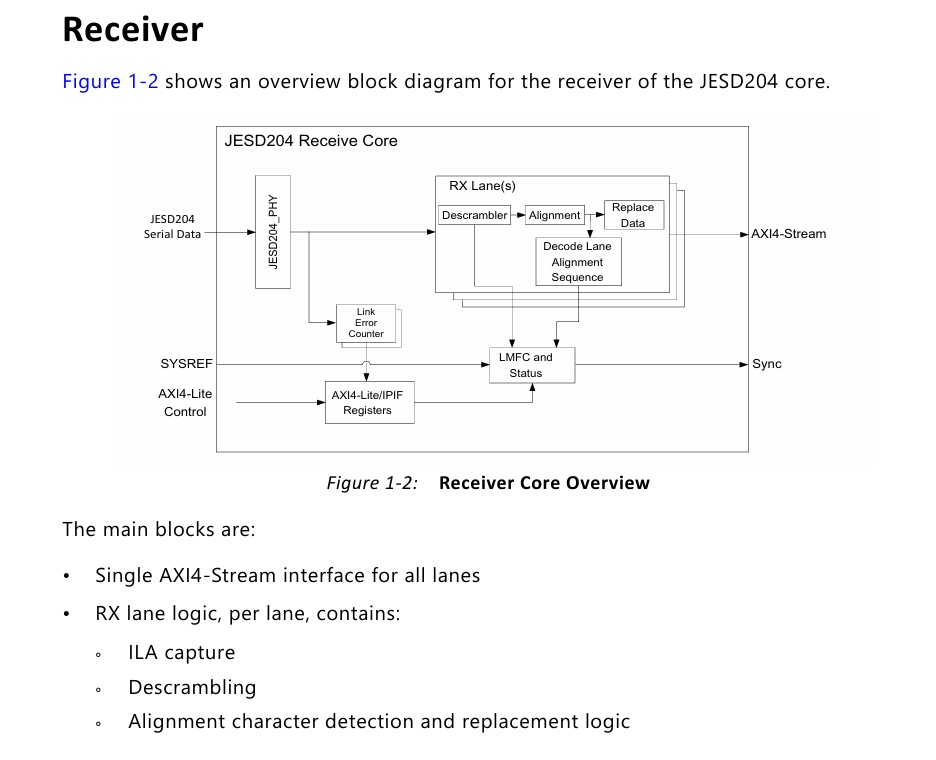

接收机(对应ADC)

与发射机类似,jesd204b串行数据进入phy中进行解串后,进入rx模块对数据进行解扰和对齐操作后通过axi-stream接口发送出去。同时外部sysref会对数据进行同步校准。

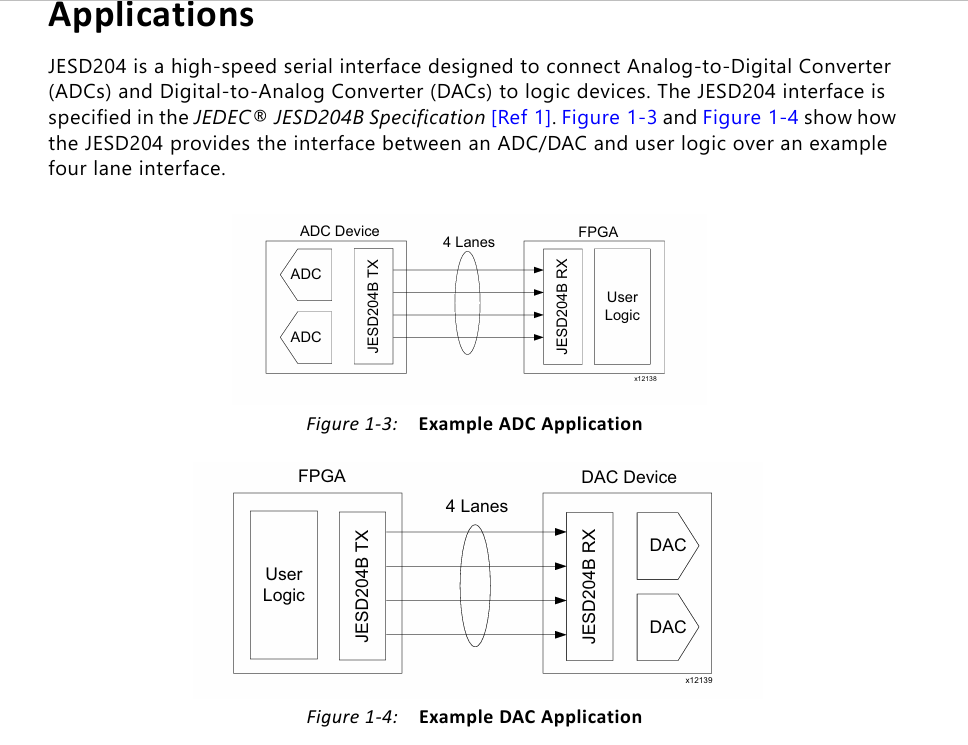

应用示例

示例四通道接口在ADC/DAC和用户逻辑之间提供接口。

端口说明

发射机时钟复位端口说明

| Signal Name | Direction | Description |

| tx_core_clk | In | 核心逻辑时钟输入。频率 = 串行线路速率/40。 |

| tx_reset | In | 内核异步逻辑复位。 |

| tx_reset_gt | Out | JESD204_PHY TX 数据路径复位输出。核心输出,用于在连接的JESD204B_PHY中复位传输数据路径。 |

| tx_reset_done | In | JESD204_PHY复位完成输入。表示JESD204B_PHY已完成传输重置过程。 |

| tx_aresetn | Out | AXI4-Stream 复位。低电平有效。与传输数据接口关联 |

| s_axi_aclk | In | AXI4-Lite 时钟。与管理接口关联。 |

| s_axi_aresetn | In | AXI4-Lite 复位。低电平有效。与管理接口关联。 |

| refclk_p/refclk_n | In | 差分收发器参考时钟输入。 收发器和四通道公共锁相环(PLL)的参考时钟 |

| glblclk_p/glblclk_n | In | 差分内核逻辑时钟输入。在子类 1 或子类 2 操作中,当参考时钟不能用于同步捕获 SYSREF(系统参考)或 SYNC(同步)时,需要额外的全局逻辑时钟。其频率 = 串行线路速率 / 40 |

| tx_core_clk | In | 核心逻辑时钟输入。频率 = 串行线路速率/40 |

| drpclk | In | 动态重配置端口(DRP)时钟。基于 UltraScale 架构的器件需要一个自由运行的 DRP 时钟。 |

| common0_pll_clk_out | Out | 与串行通道 0–3 关联的 QPLL (Quad 0) 的时钟输出。仅当使用 QPLL 时,此端口才存在。 |

| common0_pll_refclk_out | Out | 与串行通道 0–3 关联的 QPLL (Quad 0) 的参考时钟输出。仅当使用 QPLL 时,此端口才存在。 |

| common0_pll_lock_out | Out | QPLL (Quad 0) 的时钟锁定输出与串行通道 0–3 相关联。仅当使用 QPLL 时,此端口才存在。• 1 = 表示 QPLL 已锁定 |

| common1_pll_clk_out | Out | 与串行通道 4–7 关联的 QPLL (Quad 1) 的时钟输出。此端口仅适用于具有 5 到 8 个通道的配置,并且选择了 QPLL。 |

| common1_pll_refclk_out | Out | 与串行通道 4–7 关联的 QPLL (Quad 1) 的参考时钟输出。此端口仅适用于具有 5 到 8 个通道的配置。 |

| common1_pll_lock_out | Out | 与串行通道 4–7 关联的 QPLL (Quad 1) 的时钟锁定输出。此端口仅适用于具有 5 到 8 个通道的配置,并且选择了 QPLL。• 1 = 表示 QPLL 已锁定 |

| tx_core_clk_out | Out | 核心逻辑时钟输出。频率 = 串行线路速率/40 |

| tx_aresetn | Out | AXI4-Stream 复位。低电平有效。与传输数据接口关联。 |

| s_axi_aclk | In | AXI4-Lite 时钟。与管理接口关联。 |

| s_axi_aresetn | In | AXI4-Lite 复位。低电平有效。与管理接口关联。 |

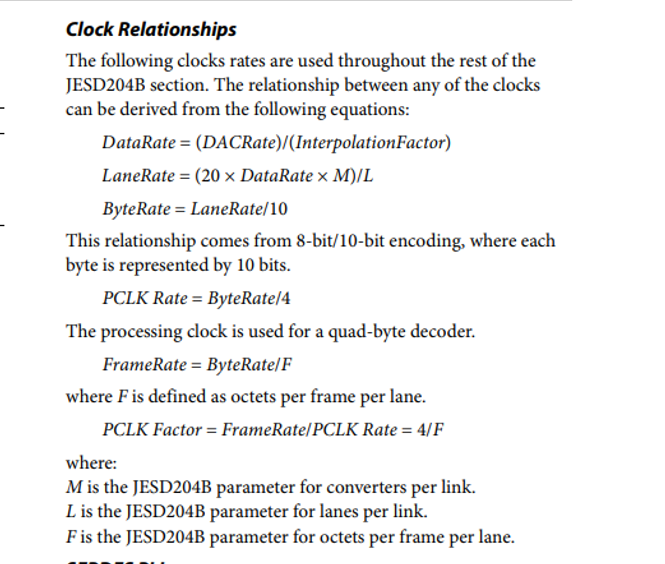

需要注意的是上述几个时钟

Core Clock

JESD204 核心的相关描述中提到,其使用 32 位(4 字节)数据路径运行,核心时钟频率始终是线路速率除以 40,并且 AXI-streaming RX 和 TX 数据接口也会以该核心时钟频率运行。

Reference Clock

JESD204_PHY中的GTP/GTX/GTH/GTY串行收发器需要稳定、低抖动的参考时钟,该时钟具有与设备和速度等级相关的范围。在某些情况下,核心时钟和参考时钟使用相同的时钟频率或源可能是有利的。然而,这可能并不总是实用的。了解对参考时钟和核心时钟施加的限制以及系统级的影响非常重要,例如SYSREF/SYNC对子类1或2确定性延迟的同步捕获。查看时钟以获取更多信息。

AXI4-Lite Interface Clock

内核通过AXI4-Lite处理器接口进行配置和监控。此接口的时钟是与核心时钟或参考时钟分开的时钟。此时钟与核心时钟或参考时钟之间没有依赖关系。

接收机时钟复位端口说明

和发射机基本一致。

JESD204 PHY 层和收发器接口端口

Table 2‐5: TX Core: JESD204 PHY Interface Ports – Shared Logic in Example Design

| Signal Name | Direction | Description |

| gtN_txdata[31:0] | Out | TX 数据到 JESD204 PHY。N = lanes- 1 |

| gtN_txcharisk[3:0] | Out | TX Char is K to JESD204 PHY. N = Lanes - 1 |

| gt_prbssel_out[X:0] | Out | TX PRBS 发生器对收发器的测试模式控制。位数 (X) 因收发器类型而异。有关详细信息,请参阅相关的收发器文档。 |

Table 2‐6: TX Core: Transceiver Interface Ports – Shared Logic in Core

| Signal Name | Direction | Description |

| txp[N:0] | Out | 差分串行数据输出 N = lanes- 1 |

| txn[N:0] | Out | 差分串行数据输出 N = lanes- 1 |

数据传输接口 – TX Core

| Signal Name | Direction | Description |

| AXI4-Stream Interface Signals (Transmit Only) | ||

| tx_aresetn | Out | 低电平有效复位(由所有通道共享) |

| tx_tdata[(32*N)-1:0] | In | AXI 传输数据(样本和控制字);首先传输最低有效字节。 tx_tdata 上的串行通道 0 的数据[31:0] tx_tdata上的串行通道 1 的数据[63:32] ... tx_tdata[((N + 1) × 32) - 1:(N × 32))] 上的串行通道 N 的数据 |

| tx_tready | Out | AXI 从数据做好准备 |

| Non-AXI Data Interface Signals (Transmit Only) | ||

| tx_start_of_frame[3:0] | Out | 帧边界指示。该信号为 4 位,用于指示下一个时钟周期中 tdata 中一帧的第一个字节的字节位置。 具体情况如下:

注意:在同一周期中,可以断言 tx_start_of_frame 的多个位,具体取决于每帧的八位组数(例如,对于 F = 1,tx_start_of_frame = 1111)。 |

| tx_start_of_multiframe [3:0] | Out | 多帧边界指示。每个多帧的第一个字节的位置的编码方式与start_of_frame |

| tx_sysref | In | SYSREF 输入。当选择子类 1 模式时,内核需要并使用此信号。JESD204B指定必须与内核时钟同步生成 SYSREF 信号(有关详细信息,请参阅时钟)。此输入应由生成 TX 和 RX 的 SYSREF 的外部设备驱动。 |

| tx_sync | In | 同步信号。同步信号被JESD204定义为低电平有效同步请求信号,因此在逗号对齐完成之前,此信号为低电平,在请求ILA和正常数据之前为高电平。 |

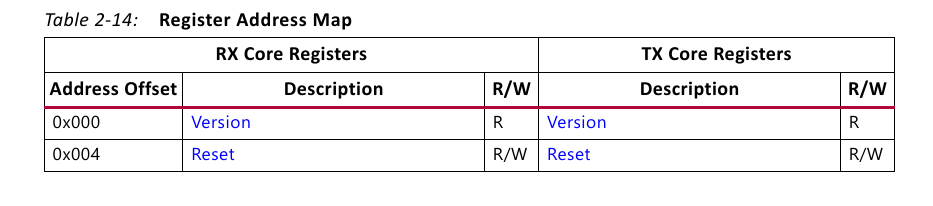

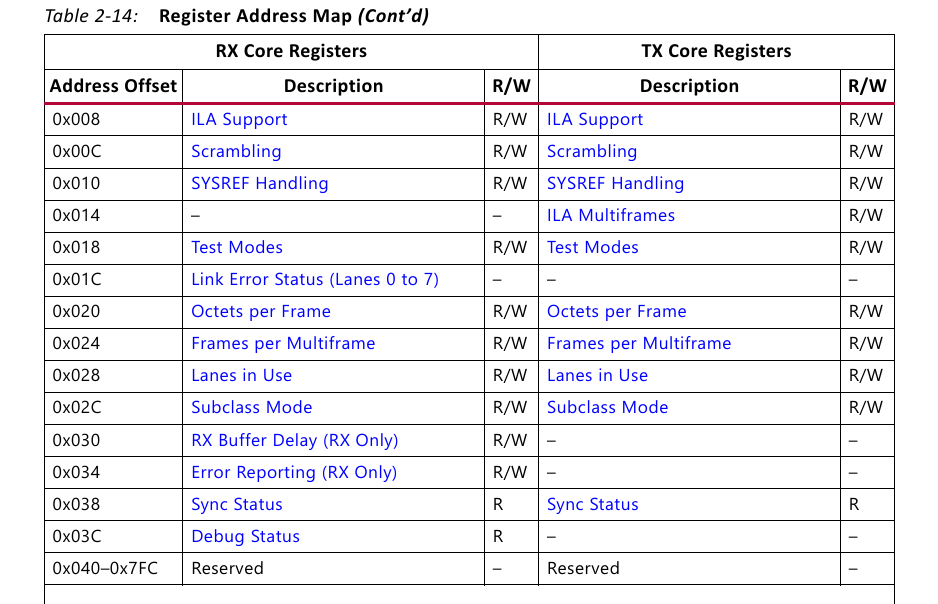

jesd204b寄存器空间

建议:Xilinx 建议,如果使用控制寄存器进行重大配置更改(特别是对成帧参数的更改),则应重置内核,以确保使用更新的参数重新同步链路。

寄存器介绍,我们在使用过程中,往往会存在需要将jesd204的寄存器在线修改。因为在硬件设计中jesd204的时钟来自于时钟芯片,如果时钟芯片的启动时间相对较慢,并且需要等待时钟芯片的锁定,所以在设计的过程中jesd204的寄存器往往做成可以在线修改的形式,方便在时钟锁定后对jesd204进行复位操作从而建链。

下面对几个重要寄存器进行介绍

| 地址 | 名称 | 含义 |

| 0x004 | reset | bit0:复位操作。高有效。 |

| 0x008 | ila support | bit0:写1,启用ila support |

| 0x00C | Scrambing | bit0:写1,启用加扰 |

| 0x010 | SYSREF Handling | bit16:重新同步时对 SYSREF 的要求 bit11-8:SYSREF延迟:添加额外的延迟到SYSREF重新对准LMFC计数器1111=15core_clk周期延迟……0000=0core_clk周期延迟 bit0:sysref always 1 = 表示内核在所有的 SYSREF 事件上重新对齐 LMFC(可能是某种计数器或时钟)计数器。 0 = 意味着内核仅在复位后检测到的第一个 SYSREF 事件上对齐 LMFC 计数器,而忽略后续的 SYSREF 事件。 |

| 0x014 | ILA Multiframes | bit7-0: 传输的初始通道对齐序列中的多帧。其相关参数范围是4至256,并且需要用所需值减1来对寄存器进行编程。 |

| 0x018 | Test Modes | 测试模式 |

| 0x01c | Link Error Status | 链路状态 |

| 0x020 | Octets per Frame | F参数。每个帧发送的8位字节数。 |

| 0x024 | Frames per Multiframe | K参数。每个多帧的参数范围。 |

| 0x024 | Lanes in Use | Lanes in Use:正在使用的lane数量。Bit:0-x设置为1,则对应的lane再使用。 |

| 0x028 | Subclass Mode | Subclass Mode:子类模式。 注:JESD204B共有三个子类:子类0、子类1、和子类2,最高支持12.5Gbps 的接口速度,使用器件时钟代替了帧时钟,子类0可向下兼容版本JESD204A,不过并不具有确定性延迟功能。此外子类1使用SYSREF同步信号在各器件之间发送并对齐本地多帧时钟。它实现数据传输同步功能,并在数据多链路之间实现已知的的、确定性的延迟。子类2需要使用SYNC信号,但没有SYSREF同步信号,由于存在SYNC信号的时序限制,子类2通常用于500MSPS以下的数据传输。 |

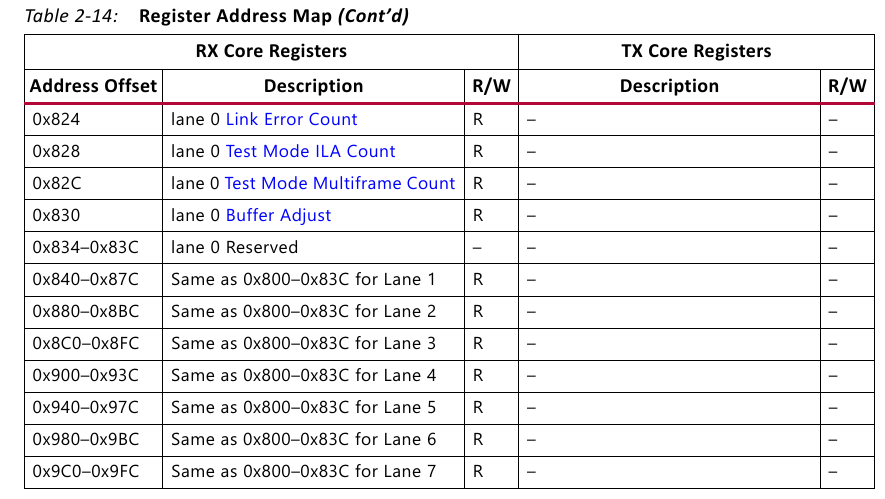

| 0x400-41C | Lane id | Lane id:在 JESD204B 协议中,数据通过多个通道进行传输,每个通道都有一个唯一的标识符,即 Lane ID。 ILA Config Data 0:SUBCLASS模式。 ILA Config Data 1:F参数。 ILA Config Data 2:K参数。 ILA Config Data 3: Bit28-24:L(每链路的通道数)[仅限 RX,TX 不可写] Bit20-16:通道 ID,用于标识 JESD204B 接口中的不同通道。取值范围为 0 到 31。 Bit11-8:存储体 ID,可能用于标识存储体或存储组。 Bit7-0:设备 ID,用于标识特定的设备。 ILA Config Data 4:bit25-24:cs参数。Bit20-16:N’参数。Bit12-8:N参数。Bit7-0:M参数。 ILA Config Data 5:bit28-24:CF参数。Bit12-8:S参数。Bit:SCR参数。 ILA Config Data 6:bit23-16:FCHK校验和。Bit15-8:RES2。Bit7-0:RES1。 ILA Config Data 7:bit16:ADJDIR。Bit8:PHADJ。bit3-0:ADJCNT。 |

| 0x800 | ILA Config Data 0 | ILA Config Data 0:SUBCLASS模式。 |

| 0x804 | ILA Config Data 1 | ILA Config Data 1:F参数。 |

| 0x808 | ILA Config Data 2 | ILA Config Data 2:K参数。 |

| 0x80C | ILA Config Data 3 | ILA Config Data 3: Bit28-24:L(每链路的通道数)[仅限 RX,TX 不可写] Bit20-16:通道 ID,用于标识 JESD204B 接口中的不同通道。取值范围为 0 到 31。 Bit11-8:存储体 ID,可能用于标识存储体或存储组。 Bit7-0:设备 ID,用于标识特定的设备。 |

| 0x810 | ILA Config Data 4 | ILA Config Data 4: bit25-24:cs参数。 Bit20-16:N’参数。 Bit12-8:N参数。 Bit7-0:M参数。 |

| 0x814 | ILA Config Data 5 | ILA Config Data 5: bit28-24:CF参数。 Bit12-8:S参数。 Bit0:SCR参数。 |

| 0x818 | ILA Config Data 6 | ILA Config Data 6: bit23-16:FCHK校验和。 Bit15-8:RES2。Bit7-0:RES1。 |

| 0x81c | ILA Config Data 7 | ILA Config Data 7: bit16:ADJDIR。 Bit8:PHADJ。 bit3-0:ADJCNT。 |

jesd204b接链同步

Subclass 1 Operation(以子类1模式为例子)

以ADC为例子,JESD204结构框架层次。

jesd204b参数接口

| M | 表示单片芯片上转换器的个数; |

| N | 表示转换器的分辨率,比如一个4通道16位的 ADC 器件,M为4,N为16; |

| N’ | 表示每个样本的总位数,以二进制值减1表示,N'等于N加上控制位(CS)和尾位(T)的数量,即 N'=N+CS+T; |

| CS | 表示每个样本的控制位数量,以二进制值表示; |

| S | 表示每一个转换器每一帧中的采样次数,一般情况下,S都是1,且S必须是整数,以防止数据的串扰。这样设计的一个好处是使得帧时钟(frame clock,FC)与采样时钟(sample clock)同频; |

| L | 表示数据传输的通道数量; |

| F | 表示1帧数据在每条LANE传输的字节数,如果1帧包含4个字节的数据,并且一共有4条LANE,可以得到F的值为1; |

| C | 表示插值系数,如果为1,表示没有插值,为2表示2倍插值; |

| R | 表示sysref时钟和多帧频率的关系,即一个sysref clock可以发R个multi frame; |

| K | 每个多帧的参数范围。 |

| LMFC | 本地多帧时钟的周期 |

| /R/ | 特定字符,代表八比特数00011100 |

| /A/ | 特定字符,代表八比特数01111100 |

| /Q/ | 特定字符,代表八比特数10011100 |

| /K28.5/ | 特定字符,代表八比特数10111100 |

| /F/ | 特定字符,代表八比特数11111100 |

扰码器加扰(解扰),链路建立,8b/10b编码是链路层的三个主要部分。发送端加扰器可以选择是否对数据进行扰码(接收端则为解码)。数据加扰的功能是可以避免数据帧之间首尾接续的相同字节带来的频谱尖峰等问题,该现象的存在容易造成电磁干扰的问题。

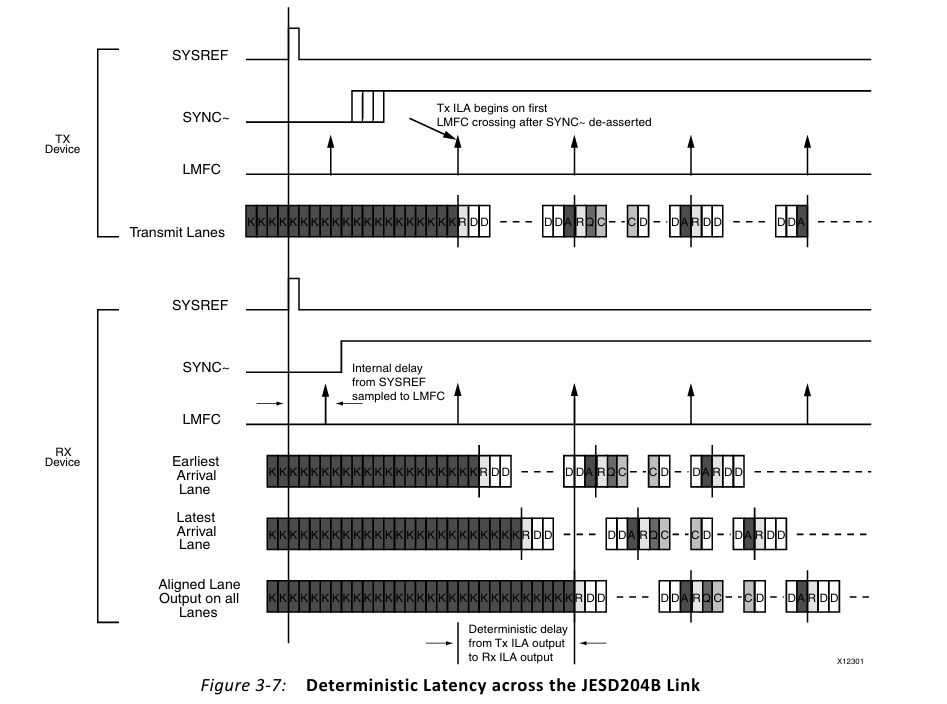

数据链路的建立有三个步骤。

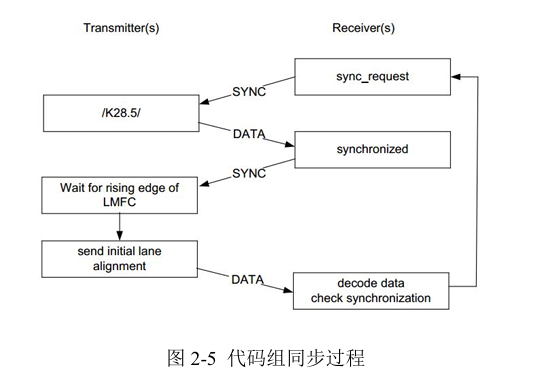

第一阶段,代码组同步

在发送端和接口端都复位后,时钟芯片产生的sysref信号,收发端利用该信号对齐设备内部的帧时钟和多帧时钟。

随后,接收端接收发送端设备发送的SYNC(同步开始请求信号)请求,当接收端检查到连续的逗号(K28.5)后,确认代码组同步建立,从而撤销SYNC请求。撤销SYNC请求后,在器件帧时钟的第一个有效沿表示代码组同步过程结束,在此之前一直发送K28.5。

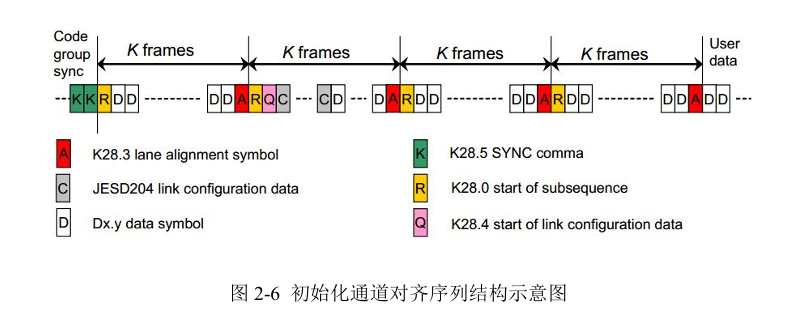

第二阶段,初始化通道对齐。

停止发送K28.5后,发送端开始发送初始化通道对齐序列。该步骤主要是依靠通道对齐序列来完成的。该序列由四个多帧组成,序列的每个帧头都以字符R表示多帧的开始,以字符A表示多帧的结束。通过初始通道对齐可识别出每一个链路上数据的多帧开始位置。

第一个多帧以R开头,然后发送一个多帧的递增数据,以A结束。

第二个多帧以R开头,后接Q字符,然后是14个配置8位字的链路配置参数,以A结束。

第三个多帧以R开头,同第一个多帧一致。

第四个多帧以R开头,同第一个多帧一致。

后续则是用户数据,不再发送斜坡数据字符和配置字符的多帧,而是开始发送应用数据,即用户实际采集的样本数据。

关于后续为什么要经过8b/10b编码后数据传输。可以看我的另外一篇文章。

Xilinx关于GTX的IP核serdes仿真和使用_gtx cdr-CSDN博客

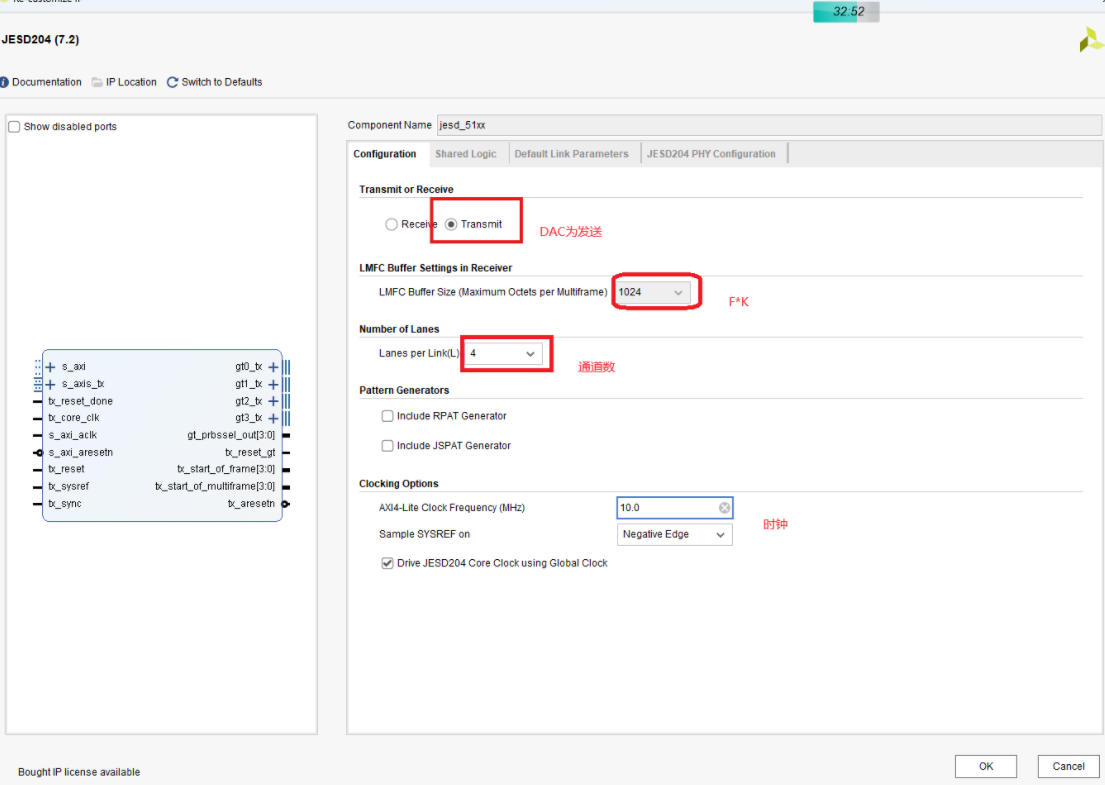

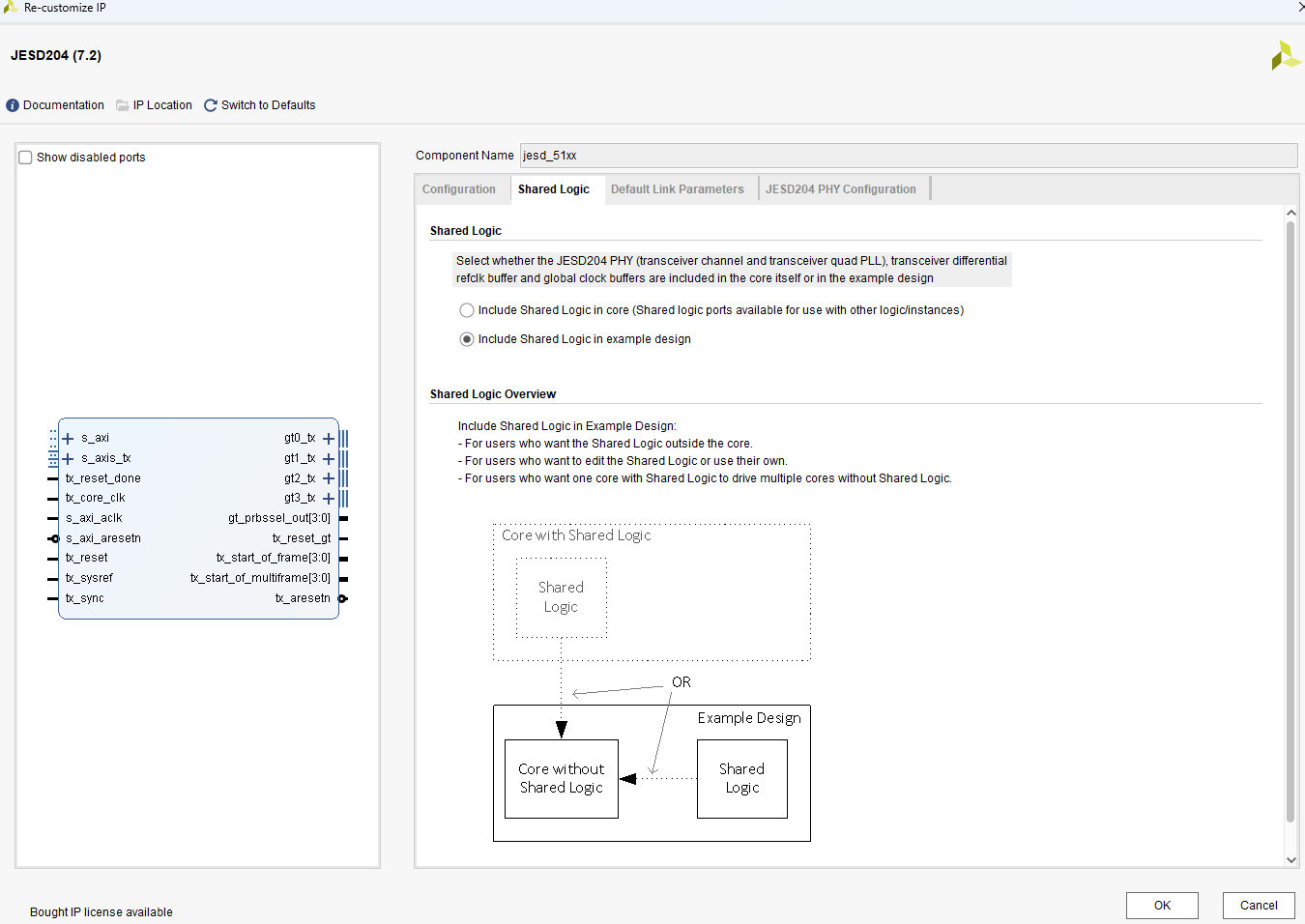

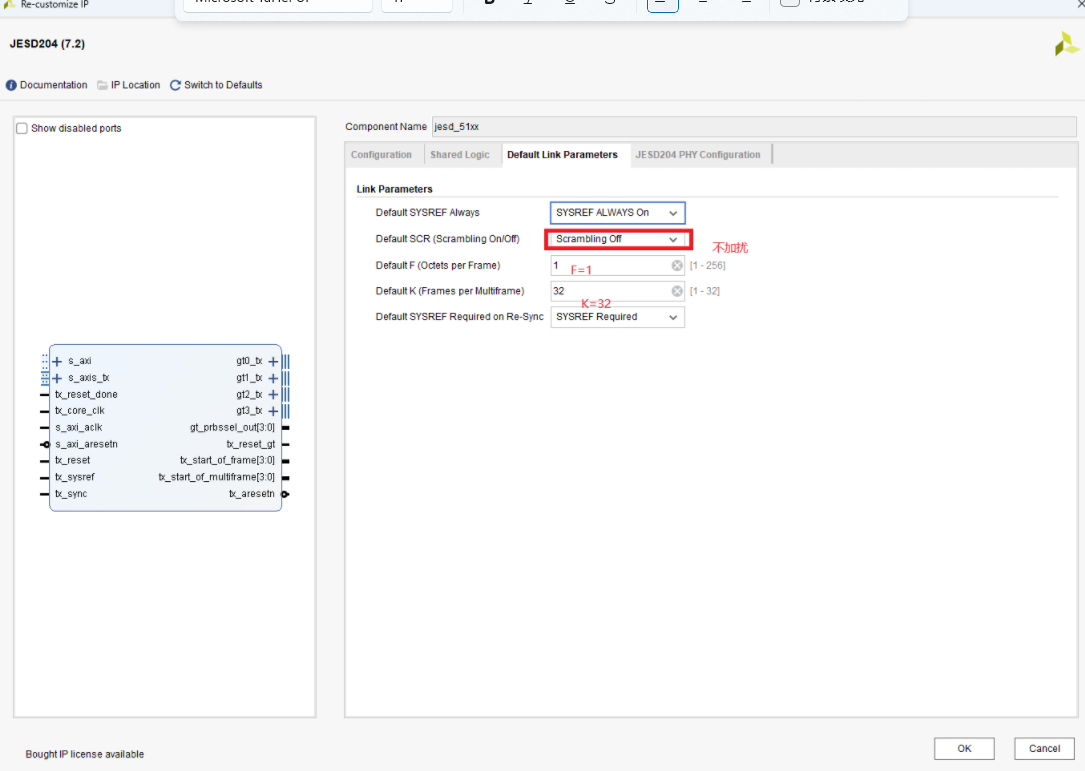

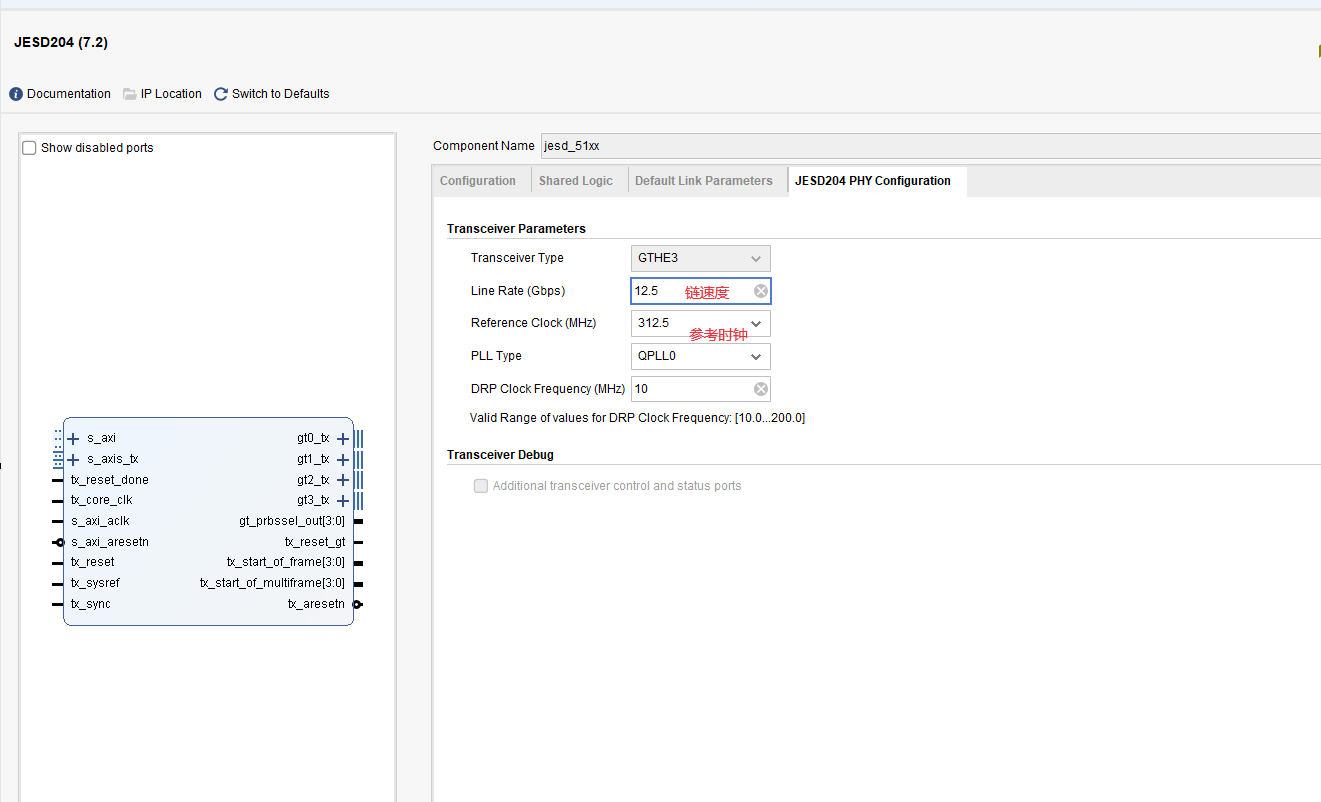

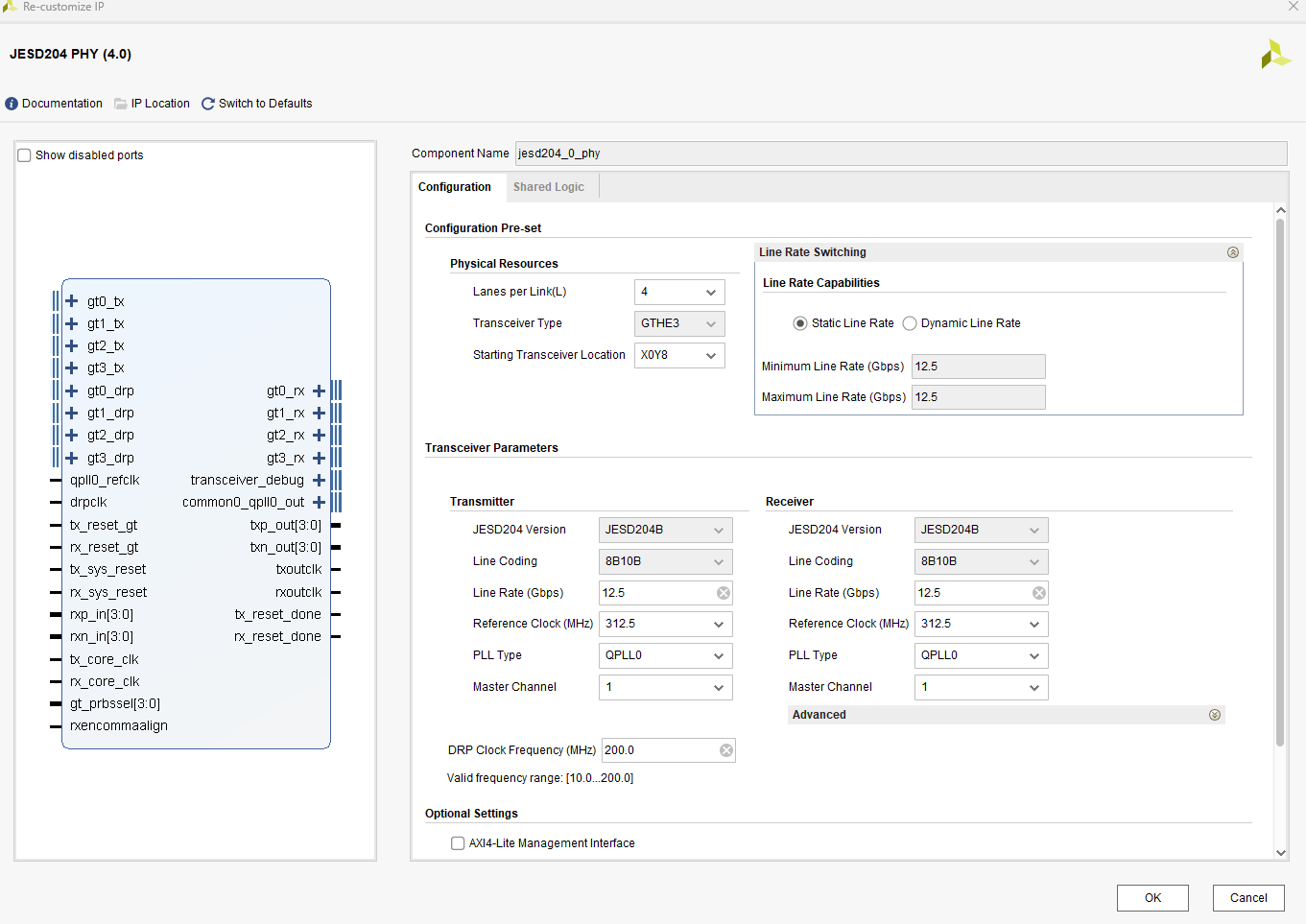

jesd204bIP的配置

jesd204b phy的配置

配置说明

AXI_LITE时钟,用于配置JESD204核。

链速度,需要结合ADC或者DAC芯片。

这里以AD9164为例子。

使用DAC采样率为5GSPS,使用4倍插值。

LaneRate=20*5/4*2/4=12.5Gbps。

refclk=12.5Gbps/40=312.5MHZ。

jesd204b的仿真

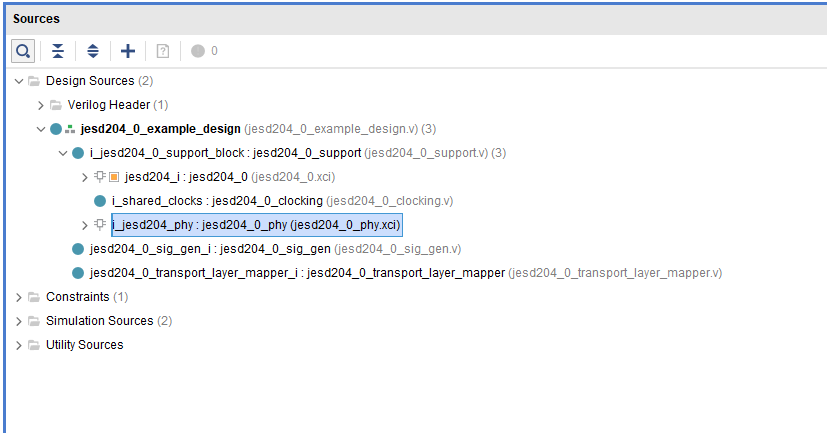

生成IP直接打开例子工程

包含顶层和IP核的例化。

以及测试数据产生模块。

和发送模块。

数据经过jesd204_0_sig_gen产生后,发送到jesd204_0_transport_layer_mapper模块打包成数据传输格式,发送到IP。

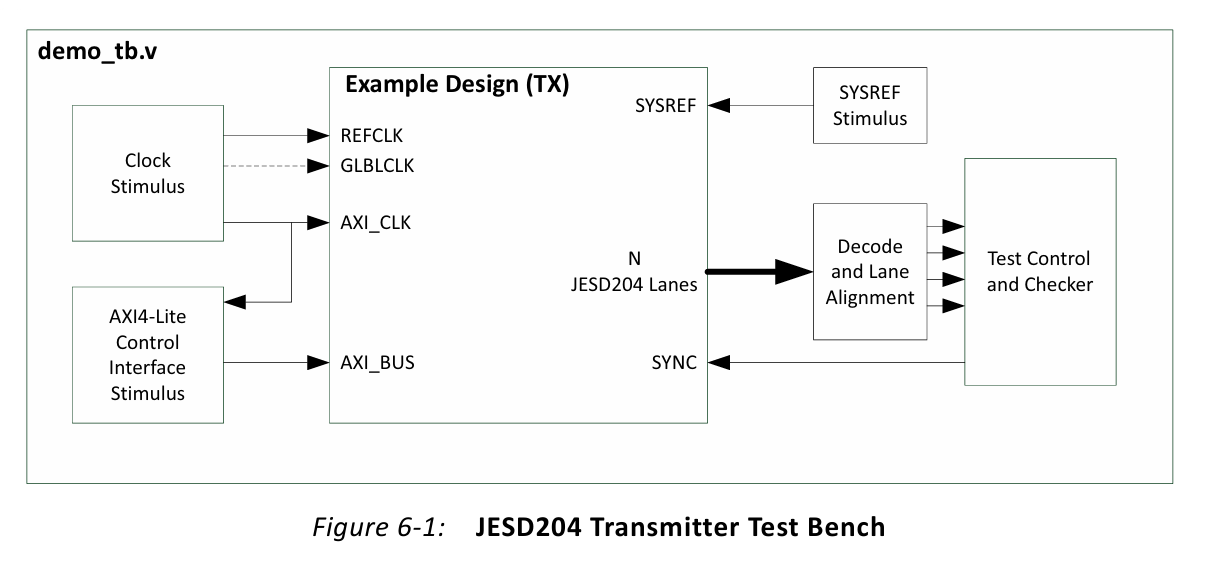

关于仿真架构

包含时钟产生模块,产生refclk和glbclk。

AXI4_lite配置寄存器模块。

SYSREF产生模块。

解码和链路对齐模块。

测试控制和检查模块。

先看一下仿真激励文件。

产生IP需要的时钟。

// Generate the 312.5MHz GTHE3 refclk initial begin refclk0p <= 1'b0; refclk0n <= 1'b1; forever begin refclk0p <= 1'b0; refclk0n <= 1'b1; #1600; refclk0p <= 1'b1; refclk0n <= 1'b0; #1600; end end // Generate the 200.0MHz DRP Clock initial begin drpclk <= 1'b0; forever begin drpclk <= 1'b0; #2500; drpclk <= 1'b1; #2500; end end // Generate the 100.0MHz CPU/AXI clk initial begin s_axi_aclk <= 1'b0; forever begin s_axi_aclk <= 1'b1; #5000; s_axi_aclk <= 1'b0; #5000; end end监测多个通道(pLanes),检测初始同步,进行通道对齐,并输出数据。

- 首先,定义了一系列的寄存器和变量来存储每个通道的相关信息,如

code_buffer用于存储每个通道的输入代码,decoded_data用于存储解码后的数据,data_align_buf和is_k_var_align_buf用于数据对齐缓冲等。 - 初始化了一些变量,如将

initial_sync初始化为 0,bit_count、comma_count和align_count等初始化为 0。 - 在

forever循环中,每个时钟上升沿进行以下操作:- 对于每个通道,将输入数据移位存储到

code_buffer中。 - 检测逗号,如果逗号数量未达到 20 或者复位未完成,增加逗号计数,否则设置

initial_sync为 1 表示初始同步完成,并设置bc_ok_i为 1 表示看到了特定的条件(可能是某种控制信号)。 - 如果初始同步完成且

bit_count为 0 ,调用decode_8b10b任务进行解码。 - 如果初始同步完成,增加

bit_count,并在达到 10 时重置为 0 。 - 检测

ILA信号,如果未看到则等待,看到后设置相关标志。 - 如果未完成所有通道的同步,增加对齐计数;如果完成同步,则将对齐缓冲中的数据按位赋值给输出。

- 将当前的

is_k_var和decoded_data存储到对齐缓冲中。

- 对于每个通道,将输入数据移位存储到

- 最后,检查所有通道的

bc_ok_i状态来确定bc_ok信号,检查所有通道的ila_sync状态来确定是否所有通道都已同步。

// The following code monitors each lane and detects initial sync. It then aligns the lanes // before outputting data. initial begin : p_decode_tx reg [0:9] code_buffer [pLanes-1:0]; reg [7:0] decoded_data [pLanes-1:0]; reg [7:0] data_align_buf [pLanes-1:0][pAlign_buf_size-1:0]; reg is_k_var_align_buf [pLanes-1:0][pAlign_buf_size-1:0]; reg is_k_var [pLanes-1:0]; reg initial_sync [pLanes-1:0]; integer bit_count [pLanes-1:0]; integer comma_count [pLanes-1:0]; integer align_count [pLanes-1:0]; reg ila_sync [pLanes-1:0]; reg bc_ok_i [pLanes-1:0]; reg ila_seen [pLanes-1:0]; integer I, J, K; all_lanes_synced = 0; for ( I = 0; I < pLanes; I = I + 1 ) begin initial_sync[I] = 1'b0; bit_count[I] = 0; comma_count[I] = 0; align_count[I] = 0; ila_seen[I] = 1'b0; end // for loop forever begin @(posedge tx_bitclock); for ( I = 0; I < pLanes; I = I + 1 ) begin code_buffer[I] = {code_buffer[I][1:9], txp[I]}; // comma detection if (is_comma(code_buffer[I][0:9])) begin if ((comma_count[I] < 20) || (axiReset_done == 1'b0)) begin comma_count[I] = comma_count[I] + 1; initial_sync[I] = 1'b0; bc_ok_i[I] = 1'b0; end else begin initial_sync[I] = 1; bc_ok_i[I] = 1'b1; //BC seen end if (!initial_sync[I]) bit_count[I] = 0; end if (bit_count[I] == 0 && initial_sync[I]) begin decode_8b10b( code_buffer[I][0:9], decoded_data[I][7:0], is_k_var[I]); end if (initial_sync[I]) begin bit_count[I] = bit_count[I] + 1; if (bit_count[I] == 10) bit_count[I] = 0; end //Waiting for ILAs if (ila_seen[I] == 1'b0) begin if (is_ila(code_buffer[I][0:9])) begin ila_sync[I] = 1'b1; ila_seen[I] = 1'b1; end else if (axiReset_done == 1'b0) begin ila_sync[I] = 1'b0; ila_seen[I] = 1'b0; end else ila_sync[I] = 1'b0; end if (ila_sync[I] !== 1'b1) begin align_count[I] = 0; end else if (all_lanes_synced !== 1'b1) begin //increment the alignment counter align_count[I] = align_count[I] + 1; end else begin //All lanes have synced //So now do a bitwise assignment to the output data word for ( J = 0; J < 8; J = J + 1 ) tx_decoded_data[(I*8)+J] = data_align_buf[I][align_count[I]][J]; tx_decoded_is_k[I] = is_k_var_align_buf[I][align_count[I]]; end //Buffer data and is_k into alignment shift register is_k_var_align_buf[I][0] <= is_k_var[I]; //must do a bitwise copy for ( J = 0; J < 8; J = J + 1 ) data_align_buf[I][0][J] <= decoded_data[I][J]; for ( J = 1; J < pAlign_buf_size; J = J + 1 ) begin is_k_var_align_buf[I][J] <= is_k_var_align_buf[I][J-1]; //must do a bitwise copy for ( K = 0; K < 8; K = K + 1 ) data_align_buf[I][J][K] <= data_align_buf[I][J-1][K]; end end // for loop end //This will notify that BCs have been on all lanes //and can now assert SYNC bc_ok = 1'b1; for ( I = 0; I < pLanes; I = I + 1 ) begin if (bc_ok_i[I] !== 1'b1) bc_ok = 1'b0; end //Check if all lanes are synced yet all_lanes_synced = 1'b1; for ( I = 0; I < pLanes; I = I + 1 ) begin if (ila_sync[I] !== 1'b1) all_lanes_synced = 1'b0; end // for loop end end // forever begin end // initial使用AXI_LITE来配置寄存器。

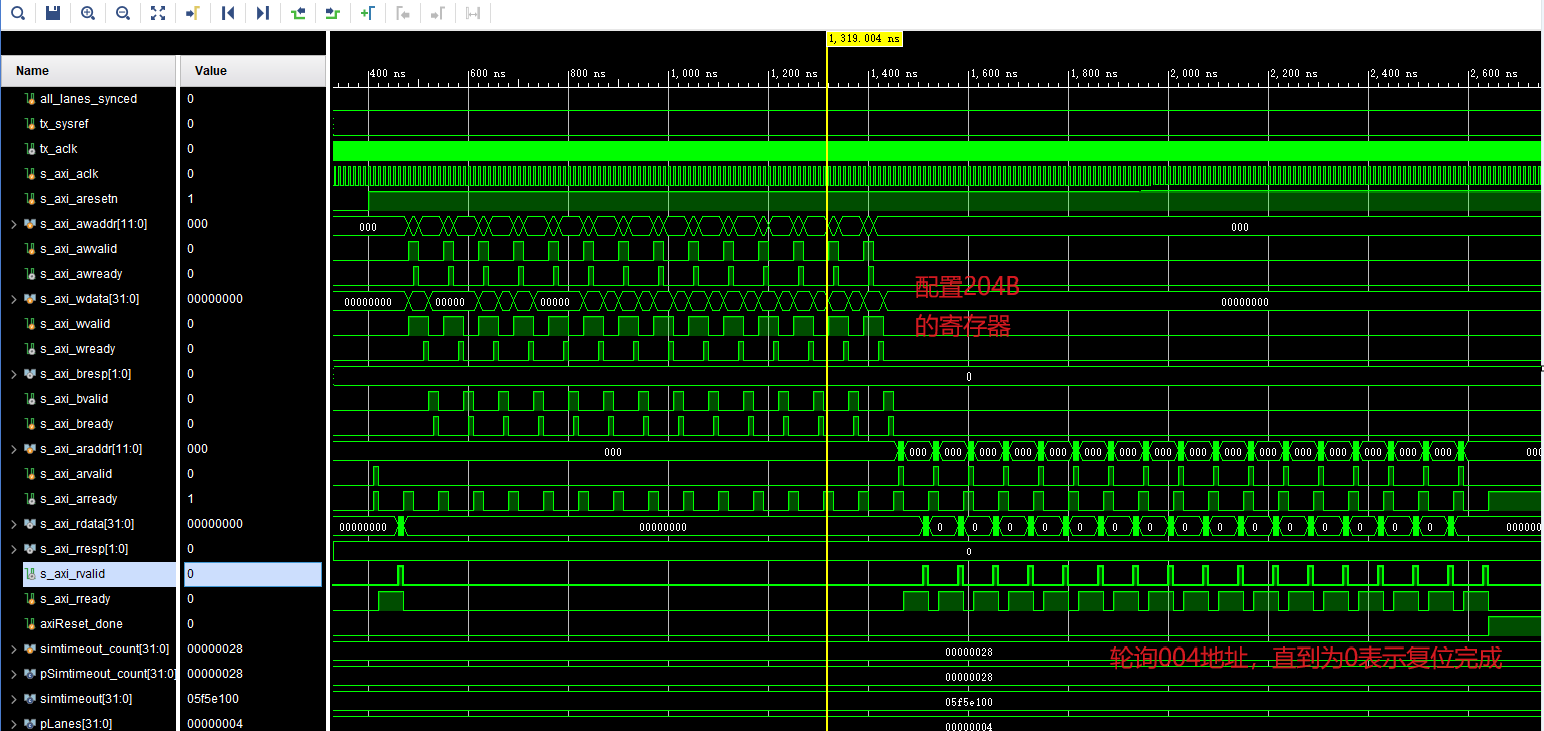

// Program the link configuration registers initial begin : p_axi_stimulus reg [31:0] register_val; s_axi_aresetn <= 1; reset <= 0; #1000; // Generate the core reset. $display("Resetting the core..."); reset <= 1; s_axi_aresetn <= 0; #400000; s_axi_aresetn <= 1; reset <= 0; // 0x000: Read Version axi_read(0,register_val); $display("Version = Major %d Minor %d Rev %d", register_val[31:24], register_val[23:16], register_val[15:8]); // 0x004: Reset later once configured // 0x008: Support ILA axi_write(2,32'h00000001); // 0x00C: Scrambling dissabled axi_write(3,32'h00000000); // 0x010: Sysref once axi_write(4,32'h00000001); // 0x014: Multiframes in ILA = 4 axi_write(5,32'h00000003); // 0x018: Test mode = Normal operation axi_write(6,32'h00000000); // 0x020: Octets per Frame F=2 axi_write(8,32'h00000001); // 0x024: Frames per Multiframe K=32 axi_write(9,32'h0000001F); // 0x028: Lanes in use axi_write(10,32'd15); // 0x02C: Device subclass 1 axi_write(11,32'h00000001); // 0x030: Rx only register // 0x034: Rx only register // 0x80C: L, DID, BID axi_write(515,{3'b0, pL, 12'b0, pBID, pDID} ); // 0x810: CS, N', N, M axi_write(516,{6'b0, pCS, 3'b0, pNt, 3'b0, pN, pM} ); // 0x814: CF, HD, S, SCR axi_write(517,{3'b0, pCF, 7'b0, pHD, 3'b0, pS, 7'b0, pSCR} ); // 0x818: RES1, RES2 checksum generated automatically axi_write(518,{16'b0, pRES2, pRES1}); // Link configuration has changed so reset the interface // 0x04: Write reset axi_write(1,32'h00000001); // Now poll register until reset has cleared register_val = 32'h00000001; while ( register_val[0] !== 32'b0 ) begin #1000 //wait for a time then read axi_read(1,register_val); end $display("AXI Configuration and Reset complete...."); axiReset_done = 1'b1; //Signal to notify that AXI has been configured end // p_axi_stimulus看一下仿真。

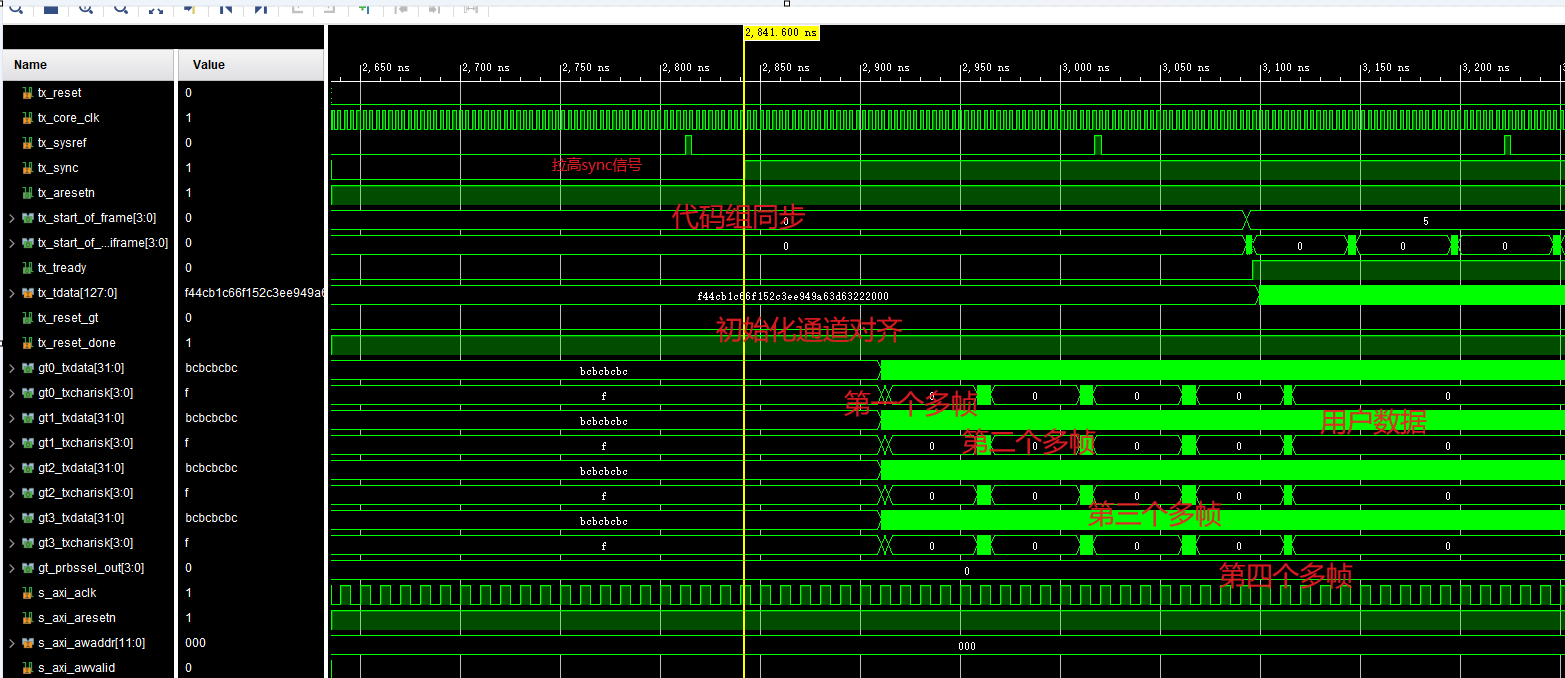

过程1,按照上述仿真文件中值配置寄存器。

轮询004地址,直到复位完成数据为0。

复位完成后

开始准备接链

代码组同步阶段。接收端拉高SYNC信号,在检测到连续的4个K28.5后。

进入初始化通道对齐阶段。发送连续数和配置信息。

之后发送用户数据。