在使用时序约束的设计过程中,综合(synthesis)是第一步。

一、综合的解释

在电子设计中,综合是指完成特定功能的门级网表的实现。除了特定功能,综合的过程可能还要满足某种其他要求,如功率、操作频率等。

有时,针对特定种类或者电路有专门的综合工具。如:

- 时钟树综合——创建时钟树

- 数据路径综合——在数据路径中创建重复的结构

- 逻辑综合——用于实现各种逻辑电路

在更高层次的视角来看,综合是指自动将上一个设计层次的数据转换成下一个层次的设计数据,可大大减少人工消耗,提高设计效率、准确度和复用性。一般来说,综合可以分成以下3类:

- 行为综合:将基于HDL描述的行为级代码自动转换为RTL级代码,只考虑逻辑不考虑延时,发展缓慢。

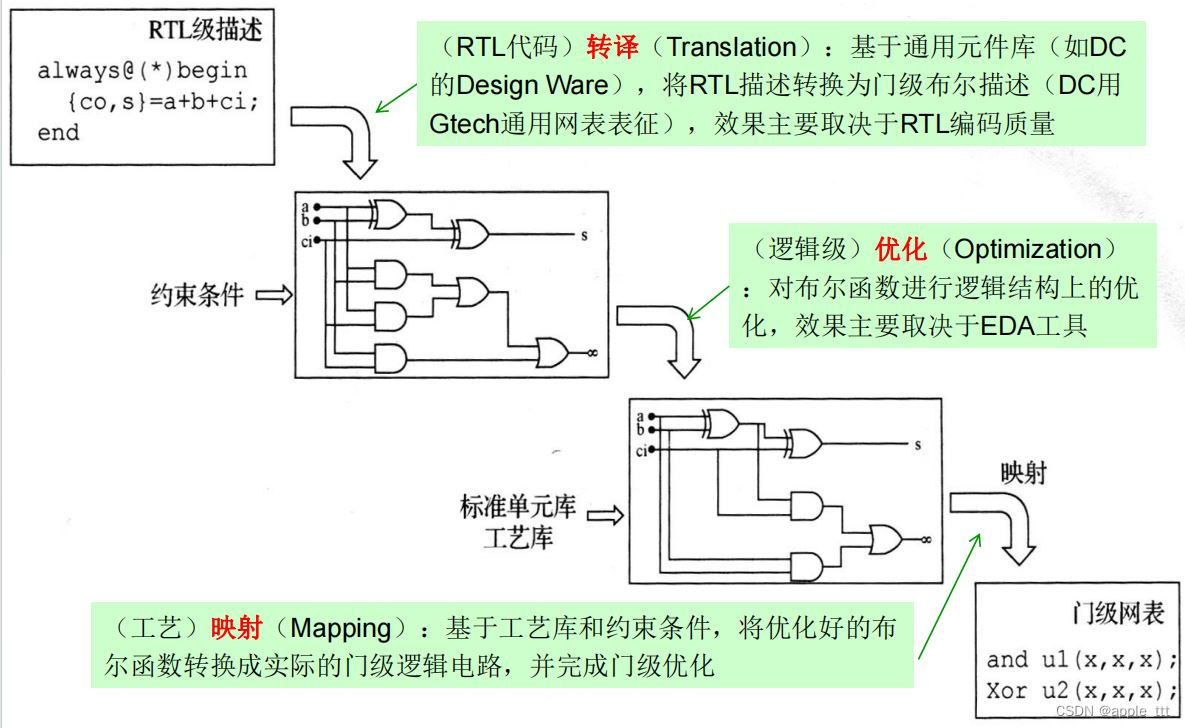

- 逻辑综合:将基于HDL描述的RTL级代码自动转换为门级网表,所用连线延时是理论预估值,普遍使用。

- 物理综合:将基于HDL描述的RTL级代码自动转换为门级网表,所用连线延时是布局布线后提取的真实值,运算量巨大。

在后文中,我们所提到的综合都是指的逻辑综合

二、时序约束在综合中的作用

设计过程中包含很多的步骤,这些步骤可以分成不同的种类,如:

- 明确目的

- 验证设计是否符合我们的期望

- 评估某些特性

- 真正实现设计

最后的一系列步骤也成为实现步骤(implementation step),综合是这些实现步骤中的第一步。

2.1 优化

对于实现网表的综合工具,它需要一些信息。第一个信息就是所实现网表需要完成的功能,该信息来自RTL描述。

对于一个设备而言,显然功能是最重要的因素。但是,设计者还必须对一下问题敏感:

- 面积:我们希望在同一单位面积上实现尽可能多的功能。

- 功率:我们希望节省电池电量,并减少结点发热。

- 性能:我们希望在设备上获得尽可能高的速度。

然而,上述目标的每一个可能影响其他目标,大部分时候这样的影响都是我们不期望看到的。所以我们经常可以听到这样一句话,没有最好的设计,只有最合适的设计。

设计者可以通过约束来将他对面积、功率、性能的要求传达给综合工具。一旦综合工具能够满足这些目标的电路,则该工具不需要进一步努力来实现“更好”的电路。进一步尝试改善任何一方面都有可能使其他方面恶化。

因此,约束是用来告诉综合工具——在实现相同功能的许多可能的实现方式中,应该选择哪个以同时满足其对面积、功率和性能的要求。

2.2 输入重排序

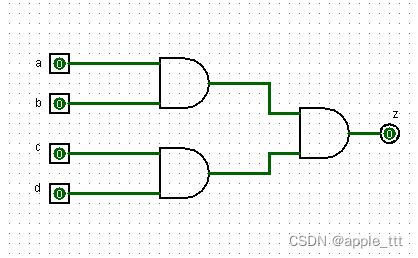

我们考虑对于4个输入a,b,c,d进行“与”操作,一个该电路最简单的实现方式如图所示:

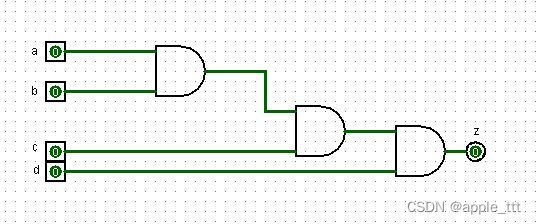

然而,现在想象输入d比其他输入来得晚,该电路取值必须等到d到达并通过两个与门。另一方面,相同功能还有另一种可替代的实现,如下图:

在该电路中,等到d到达的时候,其他三个信号已经被使用,而d只需要通过一个与门。

虽然这两个设计实现的是完全相同的功能并且占用了相似的面积(3个与门),但是对于不同的设计需求来说设计者就会有各自的倾向性。

因此,根据进入相同组合逻辑中不同的相对到达时间,综合工具可能需要在可用的选择中决定使用哪种设计,使得最后到达的信号必须通过最少的逻辑电路。

设计者使用约束来向综合工具传达各种输入信号的到达时间。

2.3 输入缓冲

驱动可以理解成载流能力。因此,更高的驱动意味着输出将切换得更快,并且可以连接更多的负载。例如,某个特定的输入必须驱动一个巨大的扇出锥(fanout cone)。该特定输入是否可以驱动这种巨大得锥体取决于输入信号的驱动能力。如果驱动输入的信号不能驱动整个扇出锥的负载,那么该信号在被输送到此巨大的锥体之前就需要进行缓冲。

设计者需要告诉综合工具驱动外部输入信号的驱动能力,以便综合工具决定是否放置额外的缓冲器。而约束用于传达外部输入驱动能力的信息。

2.4 输出缓冲

与输入缓冲类似,如果输出端口预计要驱动外部的大负载,则可能需要设计使输出端具有额外的驱动能力。

因此,设计者需要向综合工具传达端口必须驱动外部负载的信息。然后综合工具将选择适当的元器件或者缓冲器,使其具有合适的可驱动负载的能力。而使用约束可以传达输出端口需要驱动外部负载的信息。

三、综合中面临的普遍问题

3.1 设计划分

虽然综合技术使设计者的生产力得到了重大飞跃,但是综合工具的最大瓶颈是它可综合设计的规模。与综合工具可以综合的设计规模相比,当今的设计规模是巨大的。

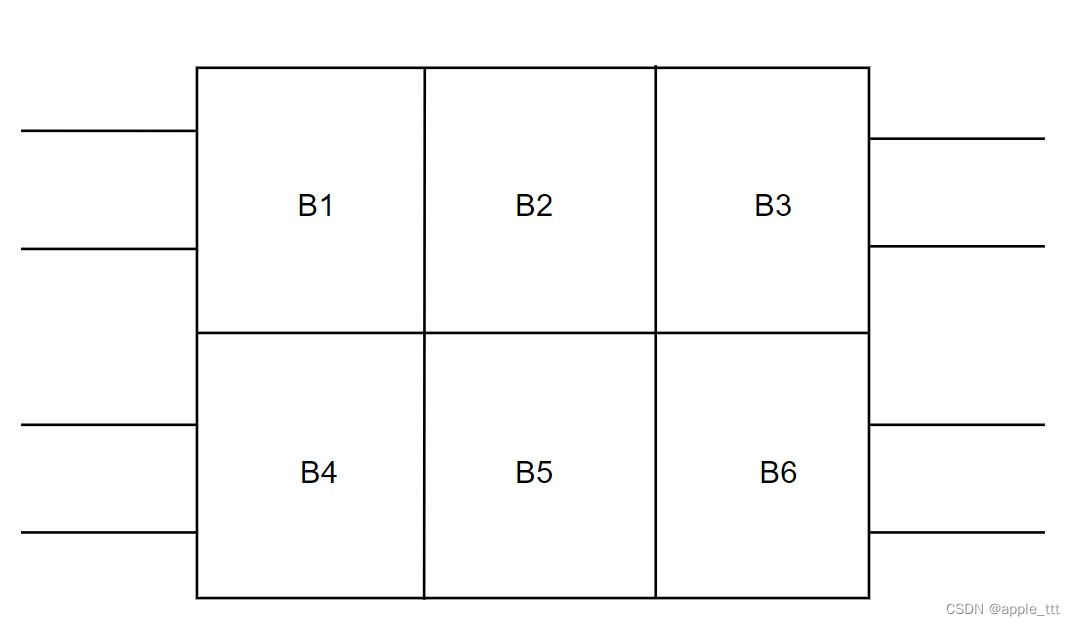

因此,一个完整的设计必须被拆分成更小的单元,称之为电路单元(block)。在综合阶段,基于设计的逻辑视图可以创建电路单元,即将相关的功能放入一个电路单元中,这种划分称为逻辑划分(logical partition)。综合工具将一个电路单元综合为一个单位,因此,综合工具在任何给定时间仅能查看一个电路单元,并且它看不到电路单元如何与设计的其余部分进行交互。下图展示了设计是如何由逻辑单元组合的。

最外面的矩形边框代表完整的设计,通常它满足整个设计的所有要求。因为综合工具无法综合整个设计,所以设计被划分为较小的电路单元(B1~B6),它们由内部较小的矩形表示。

在任何时刻,综合工具都可以查看一个电路单元,同时它对完整设计的要求是已知的,因此完整设计的顶层约束必须分解为各个电路单元的约束。对于各个电路单元,这些约束必须基于这个电路单元与其他所有电路单元的交互来创建。例如,对于电路单元B1,必须指定约束以定义其与设计的主要输入之间的交互关系和它与其他电路单元B2和B4之间的交互。

所以,本应只在顶层的约束现在被转换成在每个接口定义的更多约束。而随着约束数的增加,错误概率也随之增加。在上图中,划分表示为规则的矩形块。实际上,所有电路单元与多个电路单元交互,这就增加了整个约束集的复杂度。

让我们来考虑电路单元B1和B2之间的交互。基于该交互,将存在一些用于电路单元B1的约束和用于电路单元B2对应的约束。很多时候,在这些电路单元上工作的人员和团队是不同的。在很多情况下,为接口单元电路编写的约束也是不一致的。例如,B1的设计者可能假设他将获得该电路单元总路径时间(total path time)的50%,而剩下的50%用于路径的其他部分。类似地,B2的设计者可能也假设可用该电路单元总路径时间的50%。因此,在这两个电路单元之间,它们可能消耗掉整个路径时间,而没给连接这两个电路单元的顶层布线留下时间。

3.2 更新约束

这种不一致可能发生在同一设计的不同电路单元之间,这看起来有点奇怪。然而,由于某些电路单元没有满足其初始要求,所以各电路单元不断受到影响,这种不一致通常会逐渐蠕变。

我们假设电路单元B1不满足它的一些时序要求,这些时序会影响B2。电路单元B2的设计者现在可能必须更新其约束,并且可能影响B2/B3和B2/B5 的接口。但是,在这个阶段,B3 或B5的约束可能与B2更新的约束不同步,而且在许多情况下,这些改变的约束可能干扰面积、性能和功率之间的微妙平衡。因此,电路单元级约束可能必须根据电路单元如何集成在子系统或芯片中来更新。

3.3 多时钟设计

目前大多数设计具有多个处理器核(multiple processing cores),运行在不同的时钟频率。这些核可能有不同的外设。这些核是由多个设计组同时开发的,在集成它们的过程中。在初步实现期间可能会忽略用低频约束来约束高频核的无意错误。这些错误可能最终会在全芯片STA和后综合期间遇到,所以现在必须重新搭建电路单元约束以符合最初的设计规格,这将引起在芯片综合中增加了不必要的反复,这有可能会非常慢。