文章目录

1.概述

相信很多人都清楚,在I2C总线上需要接上拉电阻?但是您针对对I2C上拉电阻足够了解吗?本文带您详细掌握一下I2C的上拉电阻。目录如下:

- 上拉电阻的含义、上拉电阻在 I2C 电路中的作用

- 根据VOL和IOL计算I2C上拉电阻的最小值

- 根据总线电容计算上拉电阻的最大值

2 I2C的上拉电阻

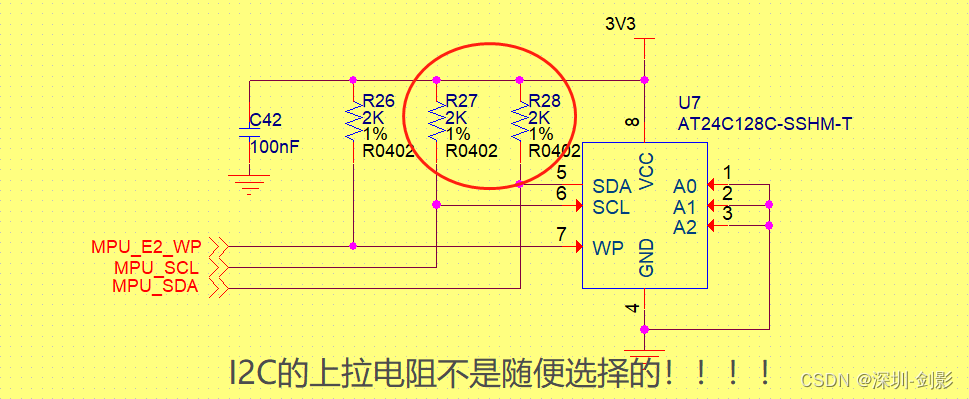

我们知道,在I2C的电路中,在SCL、SDA线与电源之间通常会接一个电阻,这个电阻称之为上拉电阻。

但什么是上拉电阻?

上拉电阻主要用于为信号线或GPIO引脚提供默认状态。通常选择几K或几十K阻值的电阻。阻值较大的电阻确保不会通过电阻不断地将过多的电流引入到信号线上(5V Vdd / 10KΩ = 0.5mA 电流)。在常见的MCU中有大约几十K的电阻可以通过代码启用的上拉电阻将 GPIO 引脚预设为逻辑高电平状态。

在I2C 的电路中,I2C设备(芯片)的 SCL 和 SDA 的内部电路是“开漏”的,这意味着它们可以吸收电流,但无法提供电流。通俗点讲就是:这种信号可以被设置为低电平,但不能被设置为高电平。

所以我们在电路中以逻辑高电压的形式给这些信号提供电流,在常见的芯片中,电压通常为5V或3.3V。为了提供这个高电压,你需要分别在在 5V 和 SCL 、SDA 总线之间连接了一个上拉电阻。如下图所示:

但是,I2C上拉电阻的阻值和封装可不是随便选择的。也是有理论依据的。

3 上拉电阻最小值计算

在数字TTL电路中,通常情况下定义的高低电平电压值如下:

- 低电平的电压 VL= 0.3 x Vdd

- 高电平的电压 VH=0.7 x Vdd

所以,我们将I2C设备接到5V系统的电路中时,SDA和SCL的电压高于3.5V时被识别为“高电平”,低于1.5V时被识别为“低电平”。在1.5V-3.5V之间的电平,我们不能确定为高or低~

I2C设备内是有mosfet的,我们需要保证电压值高于一定值才能使mosfet导通,但电压值也不能高太多,否则容易造成mosfet损坏。

此处以LED举例:假设LED的压降是1.7V,需要高于1.7V的电压才能使LED导通,但是电流必须在LED的限定值以内。如压降为1.7V、额定电流为30mA的LED,想要LED点亮的理想情况是:(5V-1.7V)/30mA=110欧。所以针对该LED选用的限流电阻为110欧。

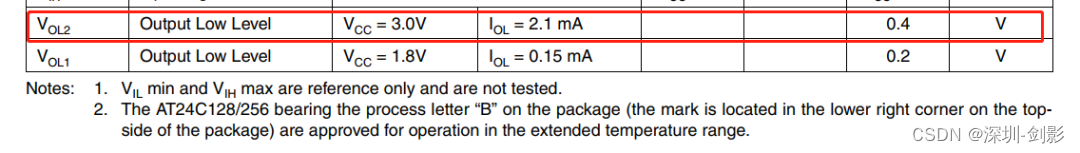

对于I2C引脚,在芯片手册中可以清楚的查到VOl(输出低电压)和IOL(输出低电流)。以AT24C128 EEPROM芯片的手册为例:

按照上述参数计算:(5-0.4)V / 2.1mA=2.2K。

我们计算出的这个值,就是I2C总线上拉电阻的最小值。我们如果选用更小的电阻值,就可能对I2C设备造成损坏。

4 上拉电阻最大值计算

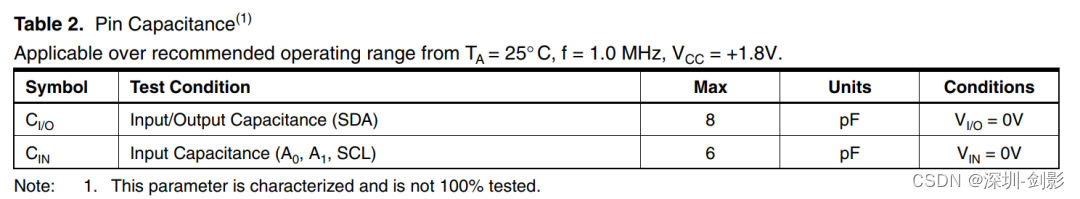

电容是无处不在的,I2C总线也不例外。I2C电路中SDA和SCL引脚也会存在某种形式的引脚电容。

同样,查看AT24C128的数据手册可以查到对应的引脚电容。如下图所示。

包括引脚电容、PCB电容等所有的叠加,我们可以理解成有一堆的小电容连到I2C总线上,现在暂且将这些电容的累加定义为Cbus。

我们之所以关心Cbus,是因为在信号变化的过程中,其实是对Cbus进行充电和放电,这样会影响到信号的延时时间。

这些电容是如何充电的呢?就是通过VCC和上拉电阻给电容充电。

从AT24C128手册中可发现,SDA的引脚电容为8pF,SCL的引脚电容为6pF。假设PCB的电容平均值为10pF。则,在SDA总线的电容总计18pF;在SCL总线的电容总计为16pF。

我们现在关注的是上拉电阻的阻值最大值应该是多少才能保证SDA和SCL在要求的时间内进行信号高低电平的切换。引入总线电容就是为了确定上拉电阻最大值。

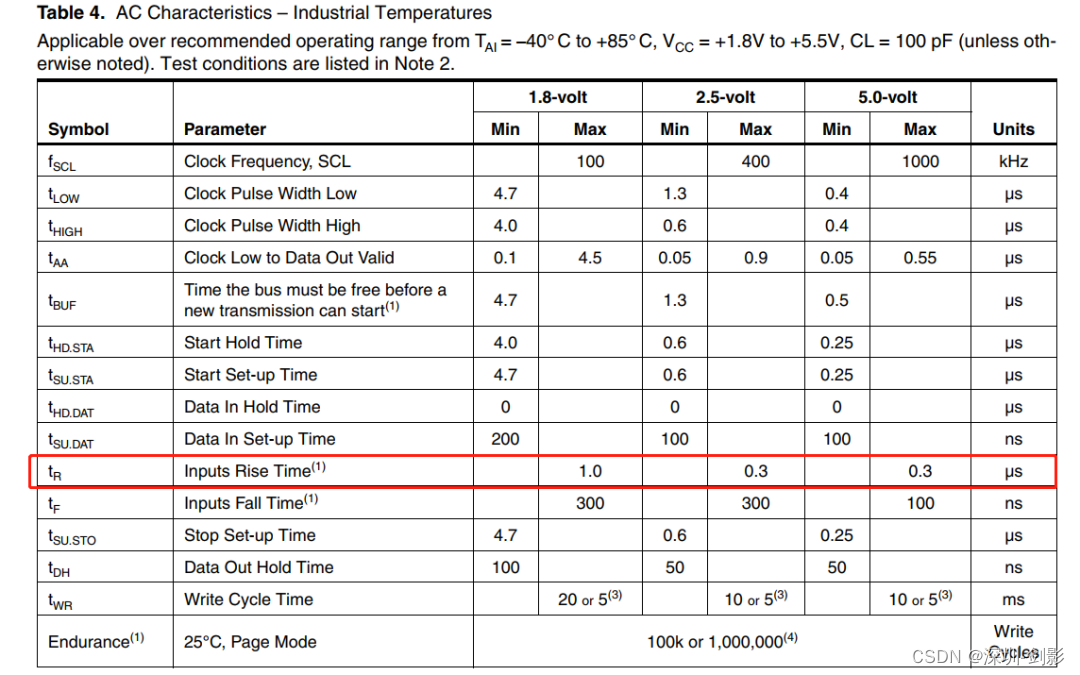

在AT24C128的收据手册中,也可以查询到上升时间tR的值,如下图。

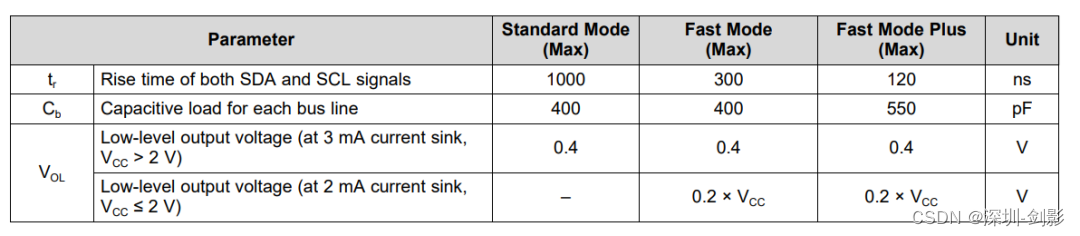

tR就是I2C总线最大允许的上升时间。除了芯片手册有规定tR值,I2C总线也规定了tR的值如下:

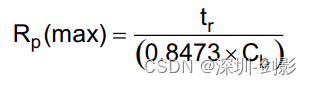

下面引入上拉电阻计算的重量级公式:

到目前为止,我们已经确定了tR和Cb的值,就可以计算出上拉电阻的最大值。以400KHz的快速模式I2C为例计算:

Rp sda max=300ns/(0.8473x18pf)≈ 18K

Rp scl max=300ns/(0.8473x16pf)≈ 18K

所以,18K就是我们确定的I2C总线上拉电阻的最大值。

结合2.2K的最小值,I2C总线的上拉电阻只能选择:2.2K~18K之间的阻值,一般选择4.7K或10K。

5 总结

上面的计算我们是只计算了I2C总线只有AT24C128的情况,只需要选用2.2K~18K之间的电阻即可。

当I2C总线挂接的设备增加、PCB布线不同等多个方面都会影响到上拉电阻阻值的选择。

声明:转载处