阅读量:0

✅作者简介:CSDN内容合伙人、信息安全专业在校大学生🏆

🔥系列专栏 :本科生课设-计算机组成原理实验

📃新人博主 :欢迎点赞收藏关注,会回访!

💬舞台再大,你不上台,永远是个观众。平台再好,你不参与,永远是局外人。能力再大,你不行动,只能看别人成功!没有人会关心你付出过多少努力,撑得累不累,摔得痛不痛,他们只会看你最后站在什么位置,然后羡慕或鄙夷。

文章目录

- 1 Verilog与Vivado基础

- 2 CPU 部件实现之 ALU 和寄存器堆实验

- 3 CPU 部件实现之 PC 和半导体存储器 RAM

- 4 单周期 CPU 设计与实现——单指令 CPU实验

- 5 总结与心得

- 参考文献

- 写在后面

手懒,word直接转的markdown,所以格式很乱

1 Verilog与Vivado基础

1.1 设计要求

熟悉并掌握 Verilog HDL 与 的使用。

请使用 Verilog 完成4选1 多路选择器(MUX) 、4 位全加器、8 位比较器、74138 译码器等模块设计,然后编写测试文件进行仿真验证。

1.2 方案设计

1.2.1 实验目标

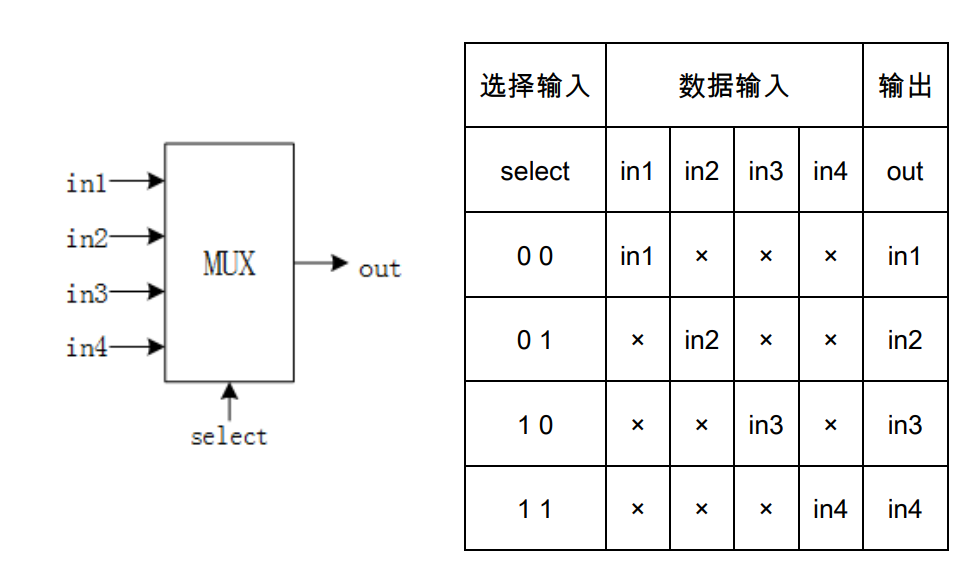

**1)多路选择器(MUX41)**是一种在多路数据传送过程中,能够根据需要将其中任意一路选出来的电路,其原理图和真值表如图 1.1所示。

图 .