阅读量:2

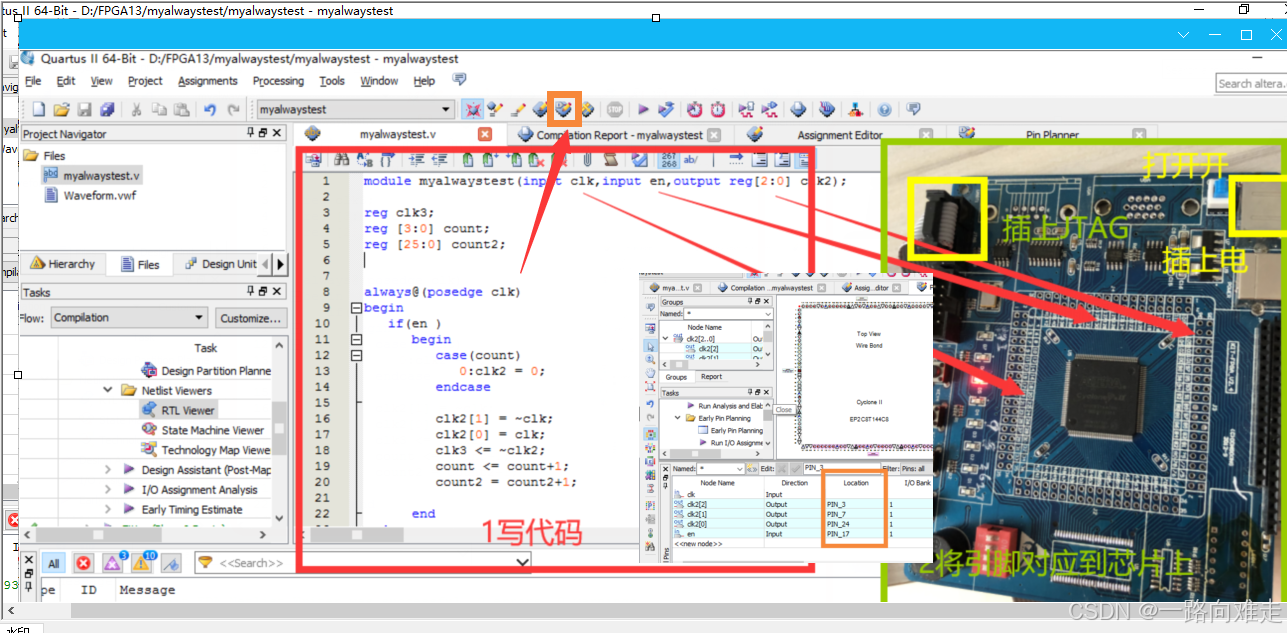

写代码,并将引脚对应到板子相应的引脚上

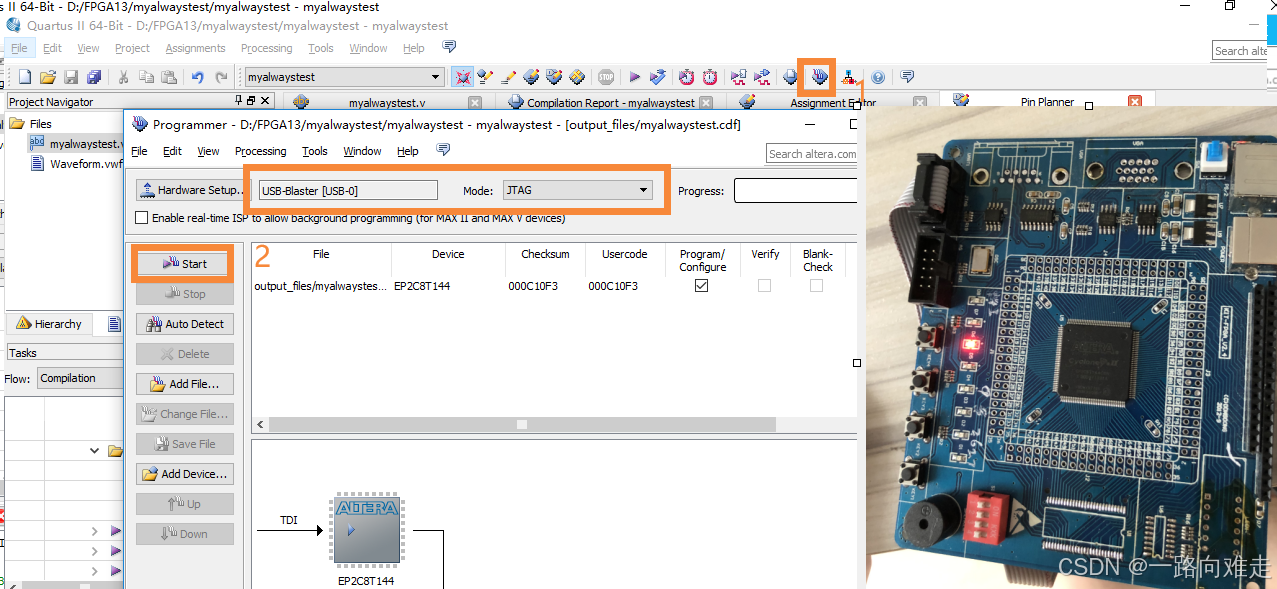

下载程序到板子上

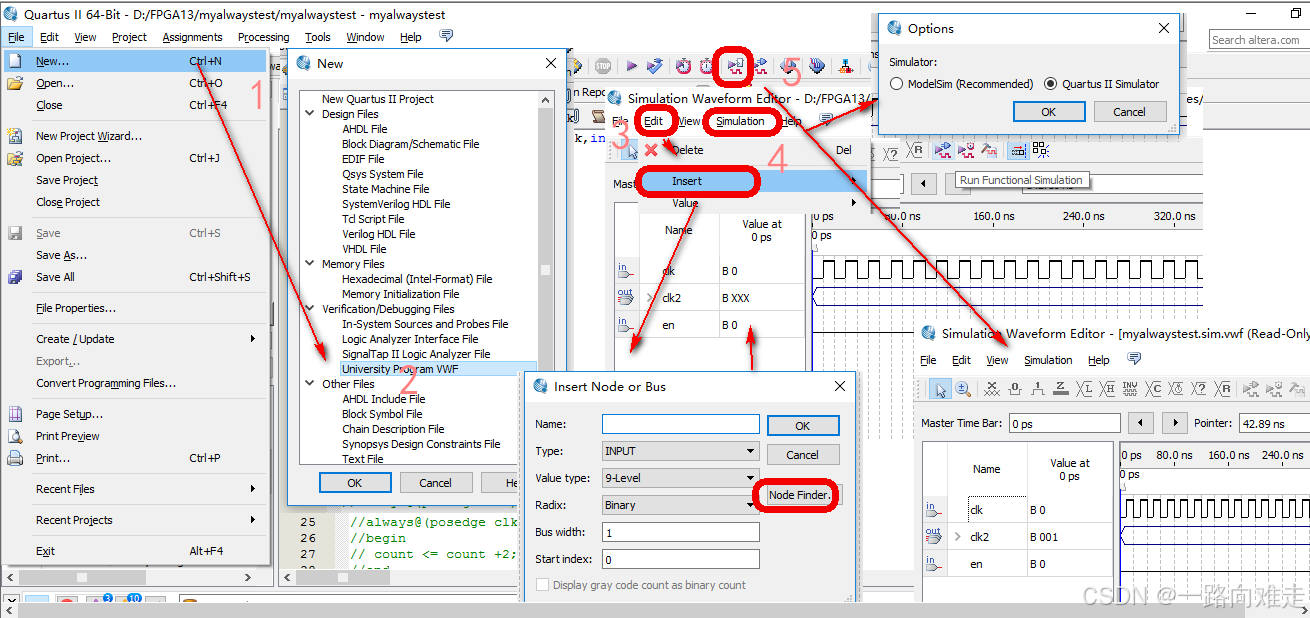

遇到错误了,不按想的来的了,进行仿真

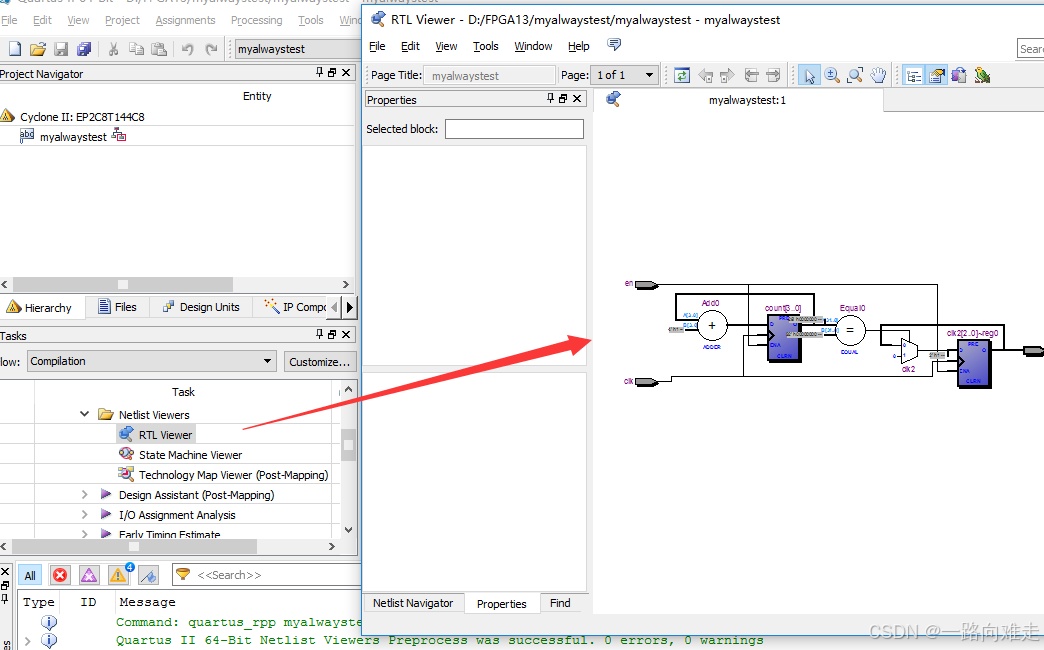

查看网表图查看问题所在

简化了一些步骤:未使用引脚的设置,电压设置;

通过画网表结构图来构成电路

【第三期:CycloneIV E最小系统板设计(一)从Datasheet上获取FPGA的基本参数-哔哩哔哩】 https://b23.tv/dQgwTz5

时钟 计数

input clk;

reg [24:] count;

always@(posedge clk)

count = count +1;

module myled3(input clk,output reg[7:0] led); reg[24:0] count; reg[2:0] count2; always@(posedge clk) begin count = count+1; end always@(posedge clk) begin if(count == 25'hfff) count2 = count2 +1; case(count2) 0:led = 0; 1:led = 1; 2:led = 'b10; 3:led = 'b100; 4:led = 'b1000; 5:led = 'b10000; 6:led = 'b100000; default: led = 'b11111111; endcase end endmodule 使用计时器 进行状态判断与顺序执行