目录

- 1.ARMCore的时间线

- 2.ARM术语小结

- 3 ARMv7的软件架构

- 4 安全状态切换模型

- 5 Interprocessing-执行状态切换模型

- 6.特权模型/安全模型/异常模型

- 小结 aarch64和aarch32对比总结

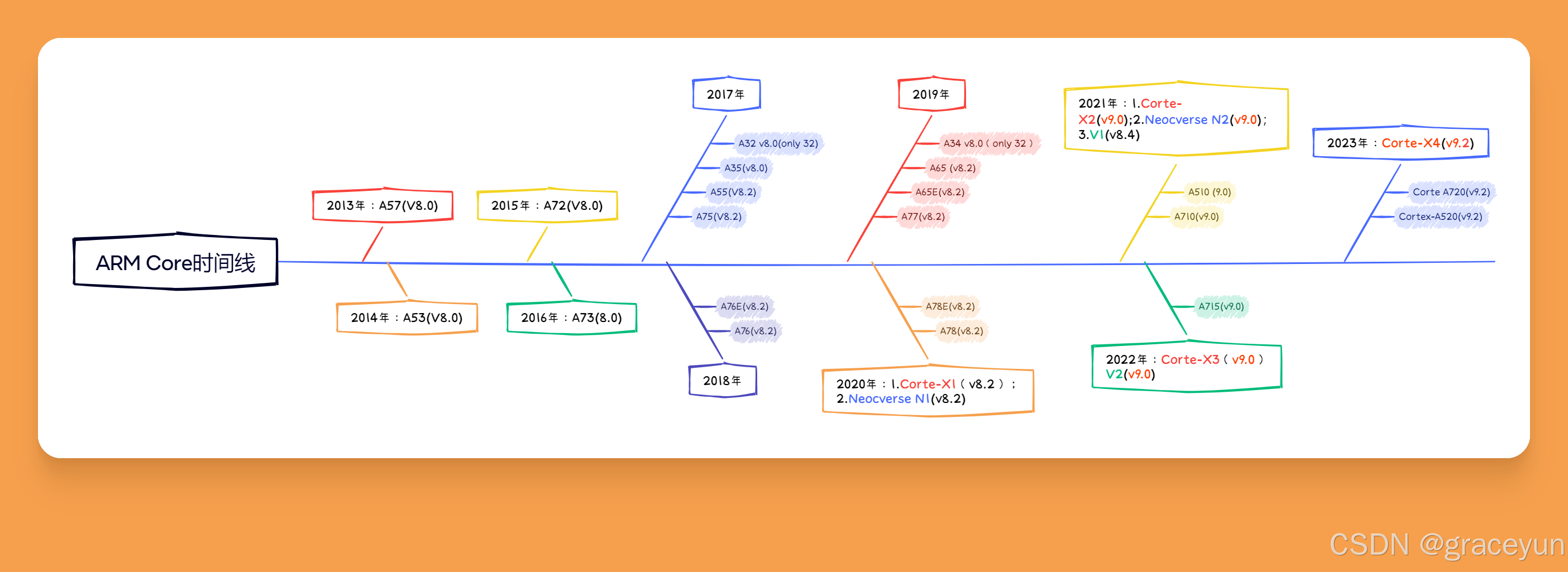

1.ARMCore的时间线

tips:加E后缀的是车规级别的芯片,是给车辆使用的。

2.ARM术语小结

2.1 A64和arrch64

- A64:是指令集。

- arrch64:是64位的架构。

2.2ARM架构现在的5个系列

- 1)A系列:应用于移动终端;2)R系列:应用于高实时性要求;3)M系列:应用于嵌入式;4)X系列:超大核;5)N系列:应用于服务器。 其中X和N系列都是A系列下的。

2.3 微架构

微架构:微架构是在架构的基础上实现的具体IP产品,比如ARM v8.0 架构的 A72,ARM v9.0的A715都是微架构。

2.4 PE

- PE:Processing Element :ARM体系结构定义了抽象机器的行为,称为处理元素(缩写是PE),不仅仅指的ARM Core 其他GPU,NPU的处理单元也可以这么叫。一般将arm核和PE画等号。但是多核比如A65里面,一个核包含两个线程,一个线程就是一个PE,此时就不可以画等号了。

2.5 Banked

- Banked:一个地址多份拷贝,一个SOC有4个核, ldr x0,[x1] 这个x1寄存器,哪个核去调用,这个x1就是这个核的x1寄存器。

2.6 ARM文档术语

1.TRM(Technical Reference Manual):Arm Cortex processor has a Technical Reference Manual,ARM 核的文档,具体实现定义的,比如查看某个寄存器的具体实现;

2.Arm ARMs(ARM Architecture Reference Manual):架构类文档,最常用;

3.CIM(Configuration or Integragtion Manual):Arm Cortex processor also has a Configuration or Integragtion Manual,一般给ASIC看的,会有板卡飞线等信息。

2.7 IMPLEMENTATION DEFINFD 和 DEPRECATED

- IMPLEMENTATION DEFINFD:实现定义的,有两个意思1)ARM IP 产品是实现定义的,比如架构文档中某寄存器是实现定义的,这时候要具体查看它的Core文档,2)是有些实现定义的,ARM没有规定如何实现,需要芯片厂商自己决定如何实现,这个也叫实现定义的。

- DEPRECATED:弃用的,在架构更新的时候,可能前面版本的某些实现被弃用了,一般不需要详细研究。

- RES0/RERS1 Reservwd,should be Zero /Reserved ,should be one (后续继续补充)

2.8 EL1t和EL1h

- EL1t和EL1h的后缀t和h分别表示什么?1)t 表示SP_EL0;h表示SP_ELn。

| Exception Level(EL) | Stack pointer(SP) options | 含义 |

|---|---|---|

| EL0 | SP_EL0t | EL0下的 SP_EL0 |

| EL1 | SP_EL1t ,SP_EL1h | 在EL1中使用SP_EL0,SP_EL1 |

| EL2 | SP_EL2t ,SP_EL2h | 在EL2中使用SP_EL0,SP_EL2 |

| EL3 | SP_EL3t ,SP_EL3h | 在EL3中使用SP_EL0,SP_EL2 |

SP 栈指针一共有4个寄存器SP_EL0,SP_EL1,SP_EL2,SP_EL3。

在EL0只能使用SP_EL0寄存器;在EL1不仅能能使用SP_EL1寄存器,还能使用SP_EL0寄存器;在 EL2不仅能能使用SP_EL2寄存器,还能使用SP_EL0寄存器;在EL3不仅能能使用SP_EL3寄存器,还能使用SP_EL0寄存器;

t:就是SP_EL0 ;h:就是SP_ELn

3 ARMv7的软件架构

1、ARM有多少种模式?

7种,8种,9种都正确。在ARMv7中大部分都是9种模式;部分核是8种模式,不支持Hyp模式;部分是7种,不支持Hyp模式和Secure Monitor 模式

| 架构 | 微架构 | User | Privilege | Secure Monitor | Hypervisor |

|---|---|---|---|---|---|

| ARMv4 | ARM 7 | √ | √ | ||

| ARMv5 | ARM 7 | √ | √ | ||

| ARMv7 | Cortex-A8 | √ | √ | √ | |

| ARMv7 | Cortex-A9 | √ | √ | √ | |

| ARMv7 | Cortex-A5 | √ | √ | √ | |

| ARMv7 | Cortex-A7 | √ | √ | √ | √ |

| ARMv7 | Cortex-A15 | √ | √ | √ | √ |

| ARMv8 | Cortex-A53 | √ | √ | √ | √ |

| ARMv8 | Cortex-A53 | √ | √ | √ | √ |

| ARMv8 | Cortex-A57 | √ | √ | √ | √ |

| ARMv8 | Cortex-A72 | √ | √ | √ | √ |

| ARMv8 | Cortex-A35 | √ | √ | √ | √ |

| ARMv8 | Cortex-A73 | √ | √ | √ | √ |

| ARMv8 | Cortex-A55 | √ | √ | √ | √ |

| ARMv8 | Cortex-A75 | √ | √ | √ | √ |

| ARMv8 | Cortex-A76 | √ | √ | √ | √ |

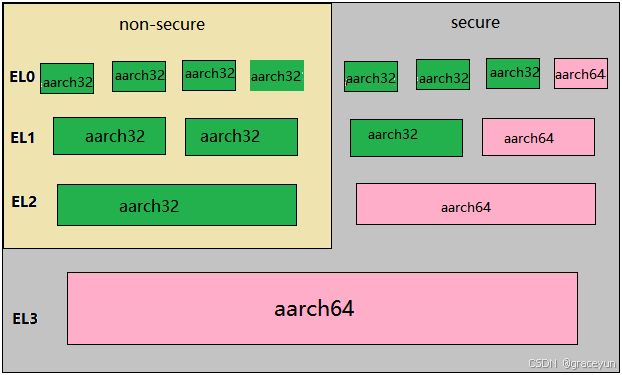

4 安全状态切换模型

4.1 Secure state和Non-secure state介绍

在不考虑RME扩展的前提下

1.ARM架构定义了两种安全状态 Secure state和Non-secure state;

2.ARM架构定义了两套物理地址空间:Secure和Non-secure;

3.如果PE是Non-secure state,那么它只能访问非安全物理地址空间:

4.如果PE是Secure state,那么它既能访问安全物理地址空间,也能访问非安全物理地址空间;

5.EL3永远是Secure state;

6.EL2/EL1/ELO是安全状态还是非安全状态,要根据SCREL3.NS比特:

7.SCR EL3.NS比特只能在EL3被修改

8.EL2是安全状态必须满足以下条件:(1)FEAT SEL2 is implemented(2)The Effective value of SCR EL3.EEL2 is 0b1(3)The Effective value of SCR EL3.NS is 0b0.

5 Interprocessing-执行状态切换模型

这个是由于v8中最初是32位架构,后面推出64位架构,V9第一款也是支持32和64,但是后面出的就是全支持64位架构,所以需要学习下这个执行状态切换,但是在未来都会使用64位架构,就不会存在这个问题了。

5.1 执行状态切换的要求

1.执行状态只能在异常从lower Exception level进入higher Exception level时,或从higher Exception level异常返回到lower Exception level时发生修改

2.如果异常进入或异常返回没有发生Exception Level变化,那么此时执行状态是不能被修改的

3.当产生一个异常从lower Exception level进入higher Exception level时,此时执行状态可能不变,或从aarch32变成arch64,不能从aarch64变成aarch32

4、当一个异常返回从higher Exception level到lower Exception level时,此时执行状态可能不变,或从aarch64变成aarch32,不能从aarch32变成aarch64

5.reset也能导致执行状态的变化

5.2、大系统软件中执行状态模型

在64位架构上可以运行64位或者32位,但是在32位架构之上只能运行32位

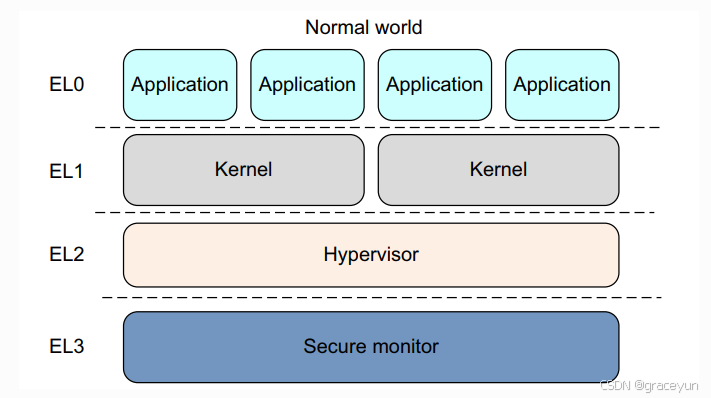

6.特权模型/安全模型/异常模型

在 ARMv8 中,执行发生在四个异常级别之一。在 AArch64 中,异常级别决定了特权级别,类似于ARMv7中定义的特权级别。异常级别决定特权级别,因此在ELn执行对应于特权PLn。类似地,具有比另一个更大的n值的异常级别处于更高的异常级别。一个数字比另一个小的异常级别被描述为处于较低的异常级别。

异常级别提供了适用于 ARMv8 架构的所有操作状态的软件执行权限的逻辑分离。它类似于并支持计算机科学中常见的分层保护域的概念。

- ELO Normal user applications.

- EL1 Operating system kernel typically described as privileged

- EL2 Hypervisor.

- EL3 Low-level frmware, including the Secure Monitor.

小结 aarch64和aarch32对比总结

AArch64,64位执行状态:

1.提供31个64位通用寄存器,其中X30用作过程链接寄存器。

2.提供64位程序计数器(PC)、堆栈指针(SPs)和异常链接寄存器(ELRS)。

3.为SIMD向量和标量浮点支持提供32个128位寄存器。

4.提供单个指令集A64定义了ARMV8异常模型,有四个异常级别,EL0-EL3,提供了一个执行特权层次结构

5.提供对64位虚拟寻址的支持

6.定义许多包含PE状态的进程状态(PSTATE)元素。A64指令集包括直接操作各种PSTATE元素的指令

7.使用表示可以访问寄存器的最低异常级别的后缀来命名每个系统寄存器。

AArch32,32位执行状态:

1.提供13个32位通用寄存器,以及一个32位PC、SP和link寄存器(LR)。LR同时用作ELR和过程链接寄存器。其中一些寄存器具有多个存储实例,用干不同的PE模式,

2.为从Hyp模式返回的异常提供一个ELR。

3.为高级SIMD向量和标量浮点支持提供32个64位寄存器。

4.提供两个指今集,A32和T32

5.支持基于PE模式的ARMv7-A异常模型,并将其映射到基于异常级别的ARMV8异常模型。

6.提供对32位虚拟寻址的支持。

7.定义许多包含PE状态的进程状态(PSTATE)元素。A32和T32指令集包括直接操作各种PSTATE元素的指令,以及使用应用程序(APSR)或当前程序状态寄存器(CPSR)访问PSTATE的指令