阅读量:1

- 实验目的:

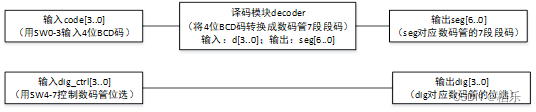

- 熟悉7段数码管显示译码电路的设计。

- 掌握数码管显示原理及静态、动态扫描电路的设计。

- 实验任务:

- 基本任务1:利用FPGA硬件平台上的4位数码管做静态显示,用SW3-0输入BCD码,用SW7-4控制数码管位选;

- 基本任务2:利用FPGA硬件平台上的4位数码管显示模10计数结果(以1S为节拍);

- 基本任务3:利用FPGA硬件平台上的6位数码管显示模100计数结果(以1S为节拍);

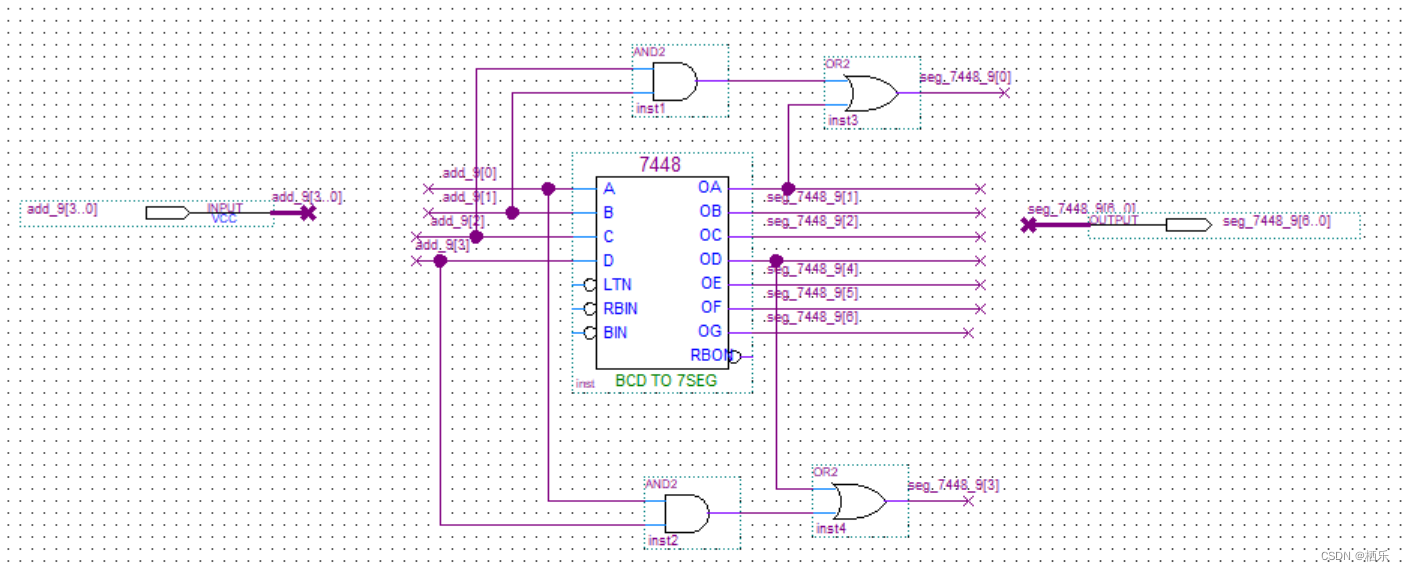

- 拓展任务1:对7448译码结果中的“6”和“9”进行补段;

- 拓展任务2:用按键控制计数器从0-9计数,4位数码管显示计数结果;(注意按键消抖)

- 拓展任务3:dig_select、decoder和code_select三个模块做波形仿真。(注意输入设置)

- 任务1指导(重点掌握数码管的静态显示原理和译码电路的设计)

- Top-level设计

2.译码模块decoder设计

7448为共阴极数码管译码器,可将4位8421BCD码译为七位段码,驱动共阴数码管以十进制数形式显示数字字形。

(拓展任务1:对7448译码结果中的“6”和“9”进行补段)

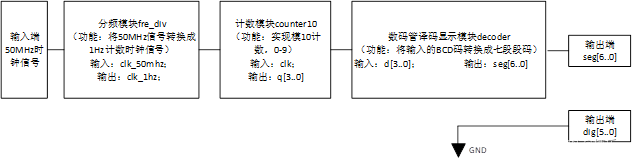

- 任务2

- Top_level设计:根据任务要求,需要一个秒信号产生模块,一个模10的计数模块以及一个译码显示模块:秒信号产生模块将开发板上的50MHz信号分频为1Hz信号,用作模10计数模块的时钟;模10电路完成0000-1001的计数,计数结果送译码模块;译码模块将4位BCD码转化为7段数码管段码。以上模块就是我们在之前的实验中已经设计过的:fre_div、cnt10、decoder。

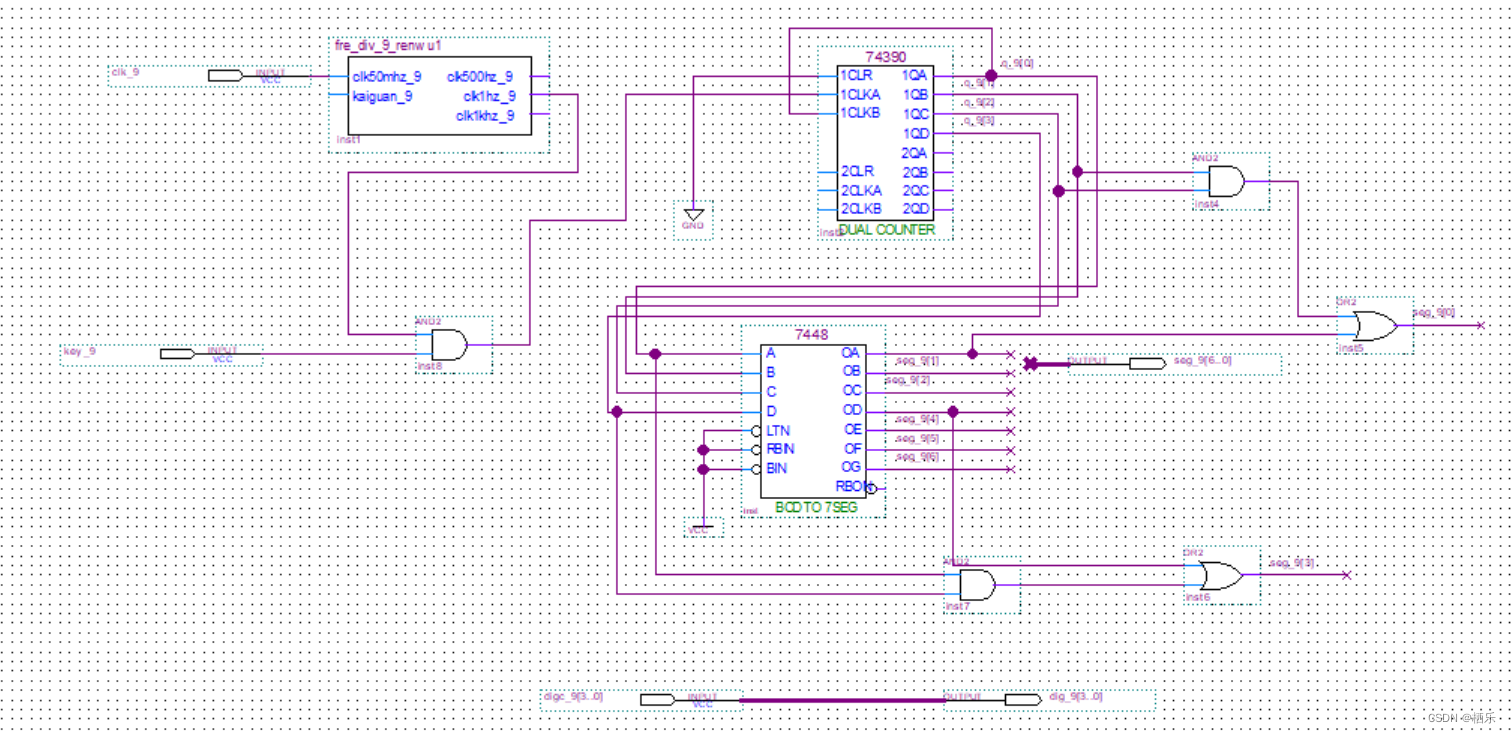

- 任务3(重点掌握数码管的动态显示原理及动态扫描电路的设计)

- 顶层电路框架设计

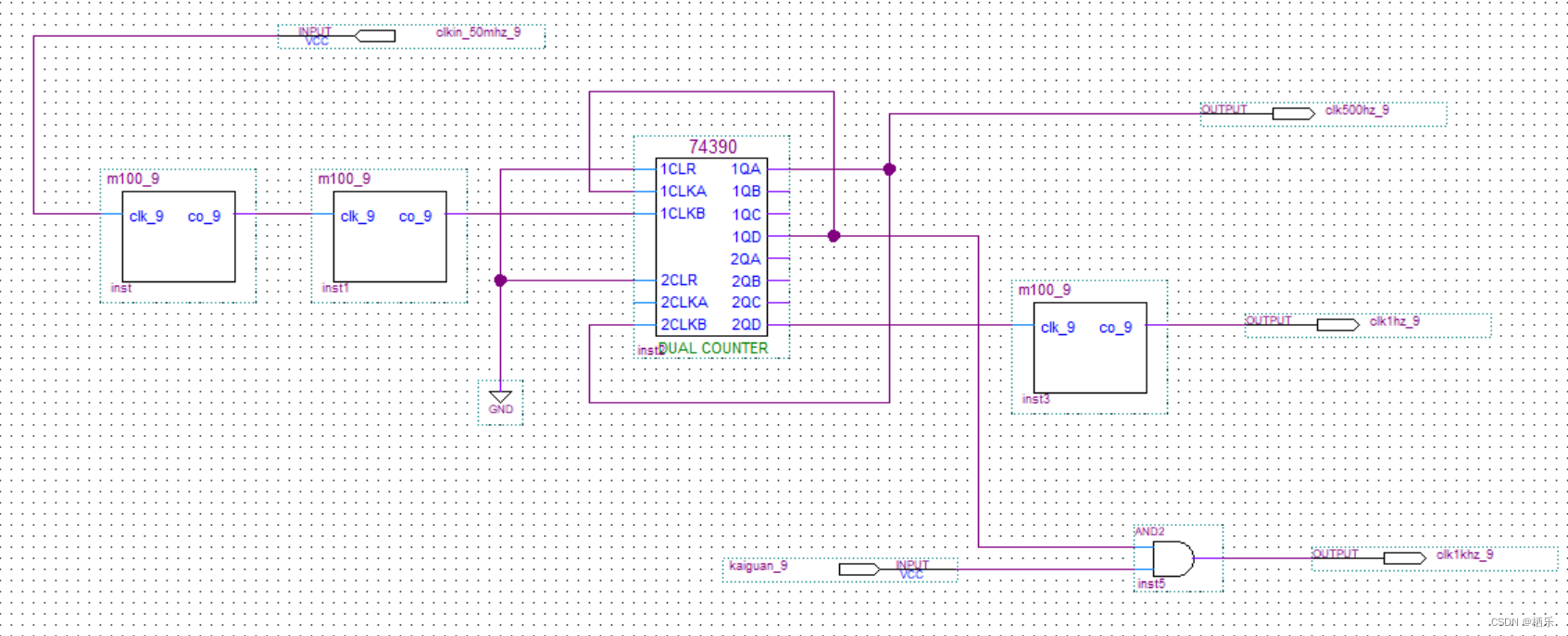

由分频模块fre_div,计数器模块counter100,动态显示模块diaplay构成。分频模块fre_div将可将实验平台晶体振荡器提供的50MHz时钟信号分频,输出500Hz,1KHz及 1Hz三种信号备用,conter100模块实现模100计数功能,display模块为数码管动态显示模块,实现计数数字在6位数码管上的动态显示。

任务3顶层设计

- 分频器模块fre_div

该模块已经在之前的实验中设计完成,请将设计文件和封装文件拷贝至当前工程文件夹待用。

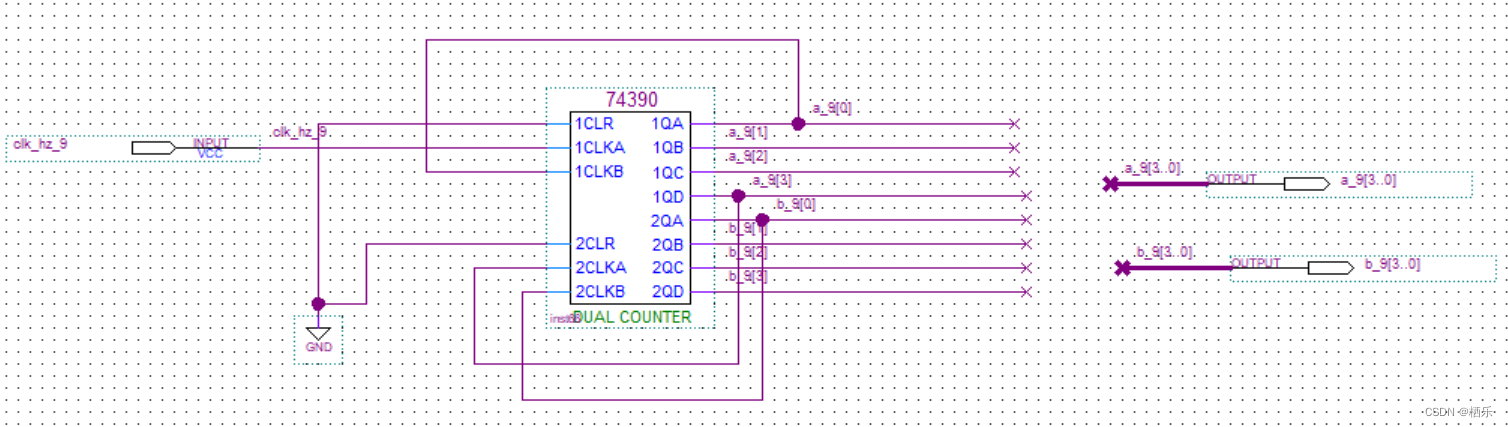

- 计数器模块counter100

可使用74390设计实现00-99的模100计数。输入1Hz时钟信号,输出shi[3..0]和ge[3..0]。

- 数码管动态显示模块display

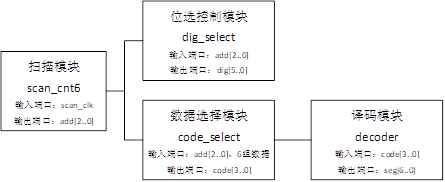

该模块主要功能是通过数码管的动态扫描实现6位数码管显示计数结果,本模块由扫描模块scan_cnt6,位选控制模块dig_select,数据选择控制模块code_select以及译码模块decoder构成,如图9-5所示。

display模块功能框图

- 扫描模块(scan_cnt6):产生dig_select和code_select模块所需要的地址信息,扫描时钟决定位选信号和数据切换的速度。

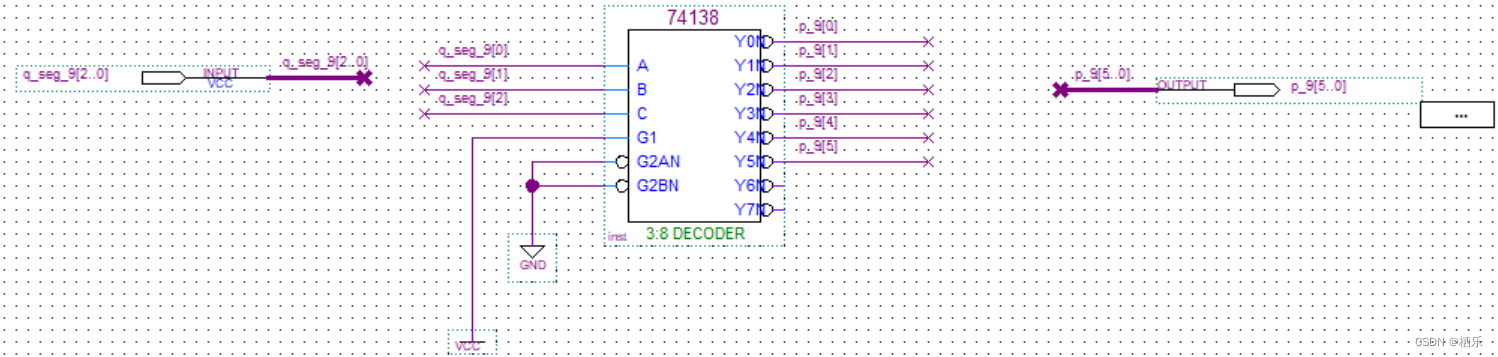

- 位选控制模块:在地址端的控制下,产生位选信号。

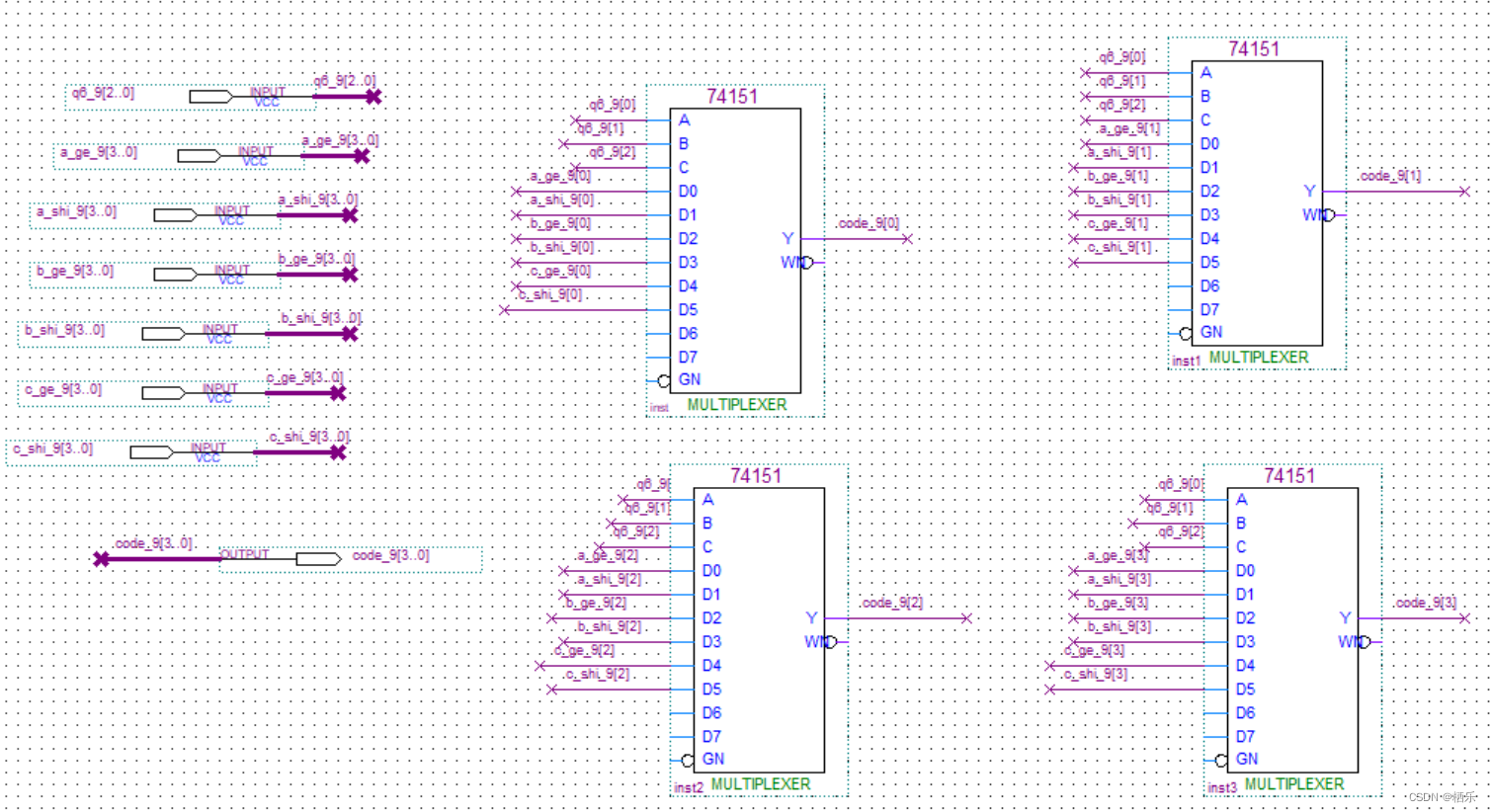

- 数据选择模块(code_select):输入6组数据,每组数据4bit,本模块完成在地址端的控制下从6组数据当中选择1组输出。

- 译码模块(decoder):本模块实现将从code_select模块送过来的4位BCD码转换为共阴数码管的段码数据。

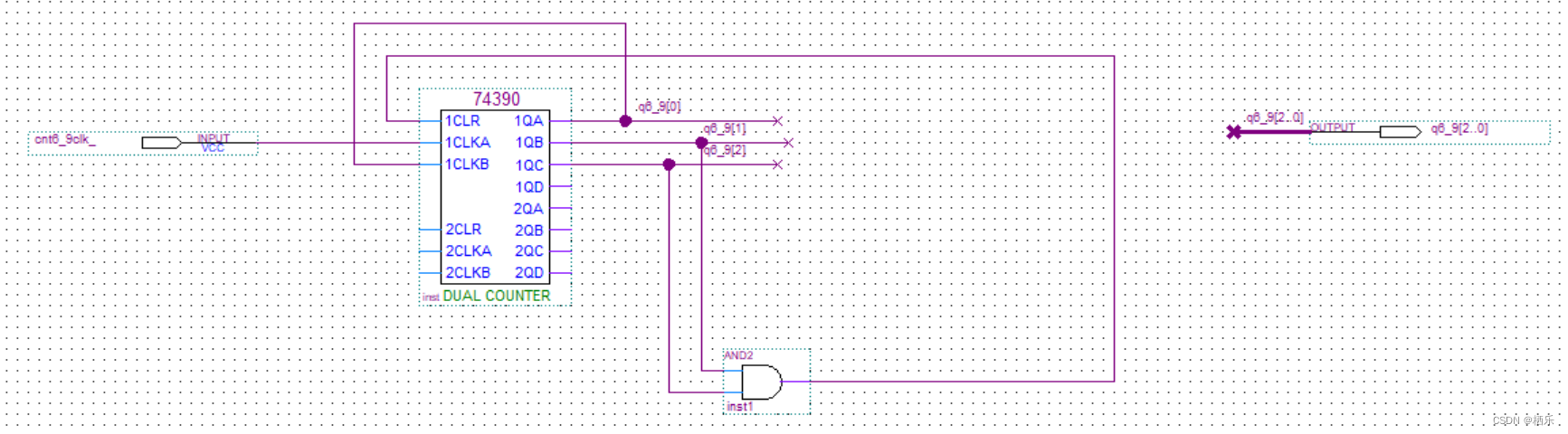

①扫描模块(scan_cnt6)的设计

模块输入端口:scan_clk; 模块输出端口:add[2..0]

②位选控制模块(dig_select)的设计

模块输入端口:add[2..0]; 模块输出端口:dig[5..0]

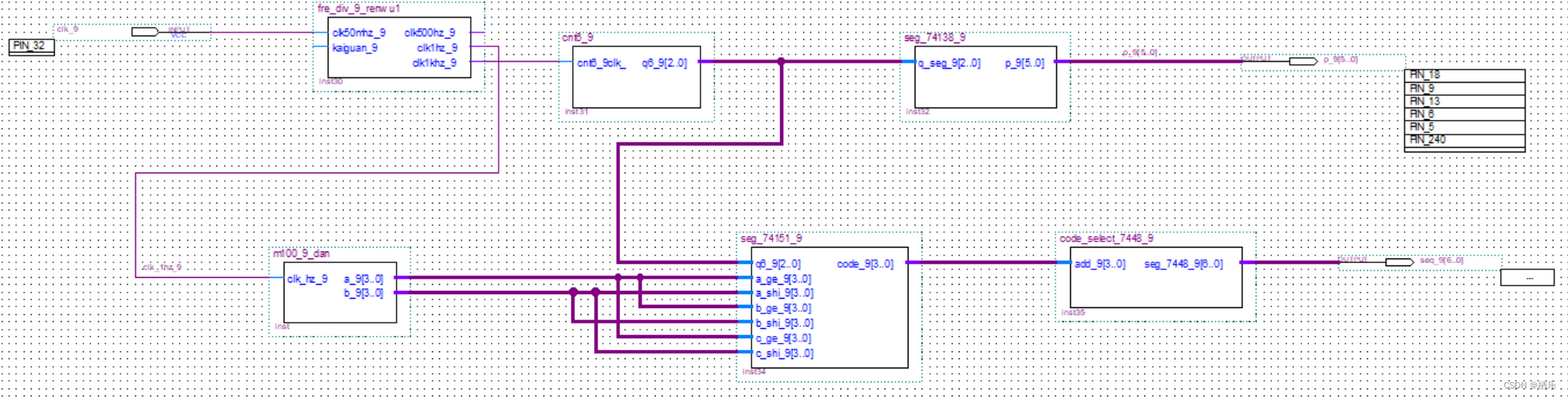

[ 顶层设计图 ]

seg_74138_9

m100_9_dan

cnt6_9

fre_div_9_renwu1

seg_74151_9

code_select_9

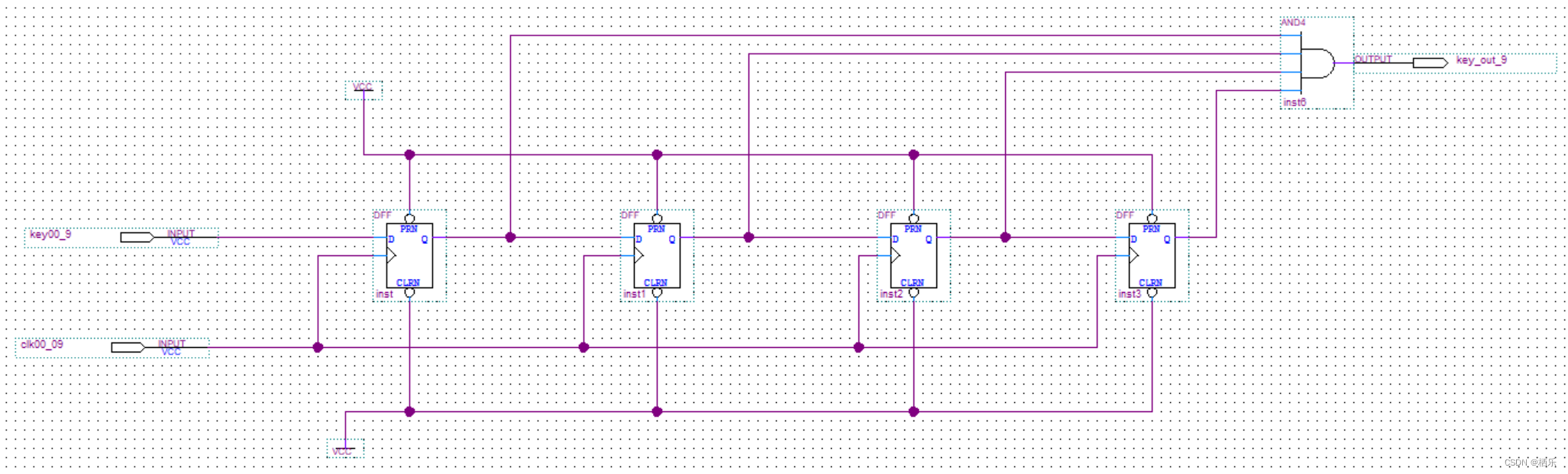

[ 按键消抖 ]