1.定义

属于时序例外的一种。(时序例外是:某条路径在默认参数下没有被正确地分析时序,在这种情况下,需要告知时序分析工具这条路径是一个例外,需要按照我地特殊指示来执行这条路径地时序分析。举例:一个数据被一个寄存器同步采样,但不是每个时钟沿都采,而是每隔一个时钟 沿采一次,这时候就需要采用多周期路径时序例外进行约束,否则这条路径就会按照默认的单周期进行分析,可能不会产生时序违例,但是较紧的要求(没必要)会占用额外的时序收敛资源)

set_max_delay/set_min_delay定义的是一条路径的最大和最小延迟,这个延迟对应的路径就是从路径源(端口、时钟、时序元件时钟端)到目的(时序元件数据端)的延迟。

2.语法

常用形式(其他选项还有很多,可以参考手册):

set_max_delay <delay> [-datapath_only] [-from <node_list>] [-to <node_list>] [-through <node_list>]

set_min_delay <delay> [-from <node_list>] [-to <node_list>] [-through <node_list>]

3.实际意义

set_max_delay/set_min_delay覆盖了时序路径上setup/hold分析中的requirement(set_max_delay对应setup,set_min_delay对应hold),啥是reruirement,可以参考其他博客中的介绍,这是Xilinx时序分析的基础概念。

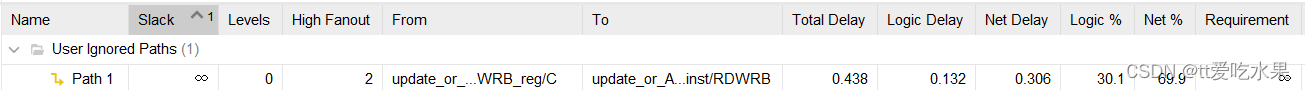

这里做一个对比方便记忆,set_false_path和set_clock_group是忽略路径时序分析,本质是把该路径的require变为∞(无穷),所以slack变成了无穷大,如下图所示我把一条路径设置为false path之后的requirement的变化。 而set_max_delay/set_min_delay是什么呢,是把requirement按照我说的来,我给你赋个值,综合工具按照我设定的这个延迟去布局布线以及时序分析。

而set_max_delay/set_min_delay是什么呢,是把requirement按照我说的来,我给你赋个值,综合工具按照我设定的这个延迟去布局布线以及时序分析。

4.特殊选项分析

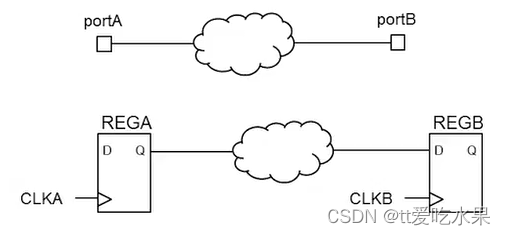

注意看语法可以发现,set_max_delay比set_min_delay多了一个命令选项-datapath_only,这个选项的意思就是,这条路径我不仅用户规定一个最大延迟(通过覆盖原有requirement实现),而且在这条路径的时序分析中,忽略时钟skew和jitter,只考虑数据通路。我们知道,针对时序余量分析,不仅要考虑数据路径延迟,也要考虑时钟路径延迟(skew=目的时钟延迟-源时钟延迟,jitter是时钟抖动),设置了datapath_only之后,计算slack时候skew和jitter就不考虑了。为啥要不考虑这两个东西,主要是因为在源时钟和目的时钟异步的情况下,这个skew可能会很大,但是在这种情况下还不能直接把这个路径设置为false path(例如格雷码异步跨时钟域传输问题,要考虑格雷码所有数据位在CDC路径上的延迟,如果延迟差别过大会造成采样错误)。

- set_max_delay可以用来约束任何有效起点(时钟、输入端口)到有效终点(时序元件D端、输出端口)之间的路径:

- set_max_delay -datapath_only就是用来约束异步信号时序路径;

- -datapath_only只有在set_max_delay中才能用(为啥看下一条括号中);

- set_max_delay -datapath_only之后会忽略该路径的hold分析(大多数hold requirement为0,那么hold分析主要是比较clock skew和data path之间的差异,如果使用datapath_only忽略clock skew,hold分析也就没有了意义);

- set_max_delay -datapath_only命令中必须得有-from选项;

- -datapath_only选项只能用在异步跨时钟域上(两个时钟没有已知的相位关系)。

- -datapath_only可以用来保证cdc路径尽可能短

5.典型例子

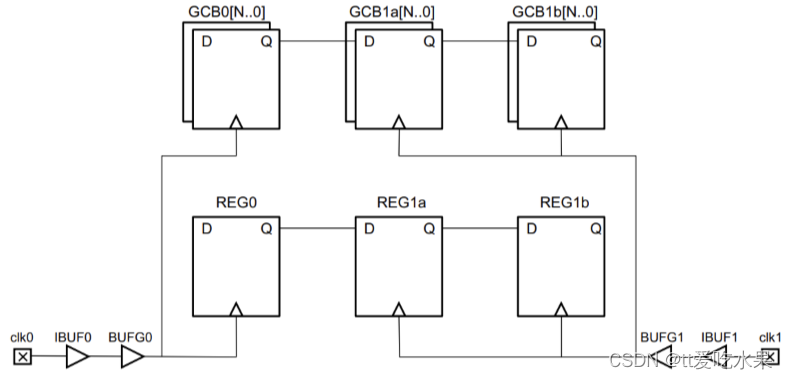

clk0、clk1异步。他们之间有两条路径,一条为1位数据同步,另一条为多位格雷码总线同步。这样的结构在异步fifo中十分常见,那么这里不能直接对两个时钟set_false_path或者set_clock_groups,这样会隐藏格雷码同步路径中的问题,如果多位格雷码数据间在GCB0到GCB1a的路径延迟差距过大,超过了目的端时钟频率,那么有可能采样段就会采到错误的数据,或者如果多位格雷码的延迟过大,即使没有很大的bit间skew,接收端也需要更长的时间才能接收到正确的值,会造成异步fifo的性能下降。所以此时的约束应该为:

set_max_delay [expr $period_fast_clk] -from [get_pins GCB0[*]/clk] -to [get_pins GCB1a[*]/D] -datapath_only

set_false_path -from [get_cells REG0] -to [get_cells REG1a]

6.其他用法

(1)通过收紧setup/hold的requirement,来对设计中一些路径进行过约束

(2)在某些情况下替代多周期路径:这种方法是唯一能够以单个时钟周期几分之一的幅度对多周期路径进行过约束,以达到时序收敛目的的方法。例如:clk=5ns,多周期路径为3的路径有200ps的建立时间违例,则可以使用如下约束代替多周期路径:

set_max_delay -from [...] -to [...] 14.5

这样,能达到时序收敛的目的。

(3)约束input port到output port路径延迟

7.注意事项

时序例外的使用有严格的优先级,高优先级的会覆盖低优先级的设置,优先级规则如下:

1.约束越明确,优先级越高,比如:

set_max_delay -from [get_clocks clkA] -to [get_pins inst0/D] 12

set_max_delay -from [get_clocks clkA] -to [get_clocks clkB] 10

第一个set_max_delay的优先级就更高,应为-to选项的参数pin比clock更加明确

2.时序例外优先级排序:

(1)set_case_analysis(最高优先级)

(2)set_false_path

(3)set_max_delay/set_min_delay

(4)set_multicycle_path