零.前言

在学习FPGA课程时,感觉学校机房电脑用起来不是很方便,想着在自己电脑上下载一个Quartus II 来进行 基于 vhdl 语言的FPGA开发。原以为是一件很简单的事情,没想到搜了全网文章发现几乎没有一个完整且详细的流程教学安装(也可能是我没搜到,,ԾㅂԾ,,)【视频b站上有,搞完才发现T.T】,因此想做一个纯小白式安装教程,将网上分享的几位大佬关于安装部分的流程都总结到一文当中,包括软件及软件配套仿真和芯片库的安装,让大家花最少的时间完成安装。相关文章链接在文末。

多图预警

一.Quartus安装

1.首先需要先去百度网盘下载相关资料

下载链接:百度网盘 请输入提取码

提取码:qomk

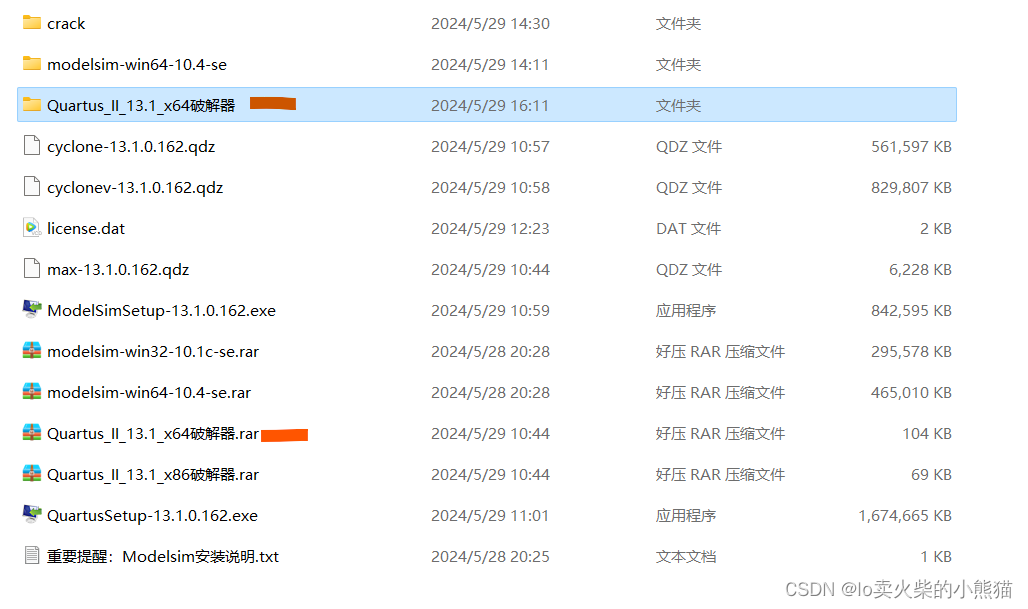

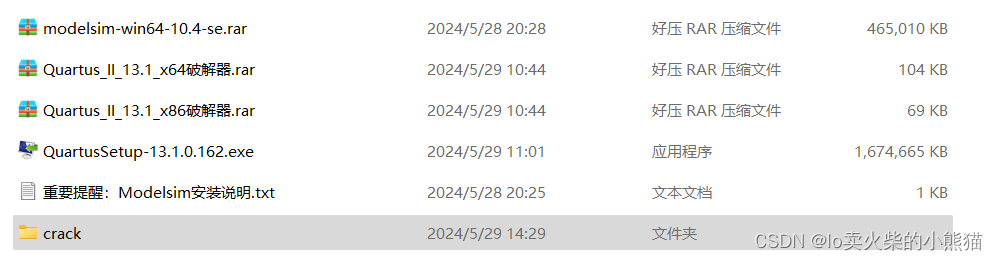

2.下载的是压缩包,解压后可以看到13个文件

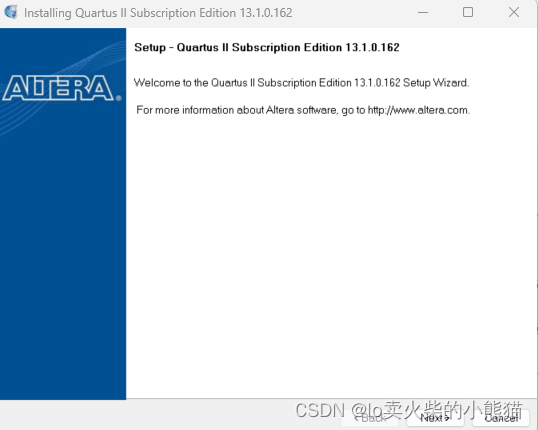

先打开QuartusSetup-13.1.0.162.exe文件开始安装。

3.安装流程

(1)打开后点击next

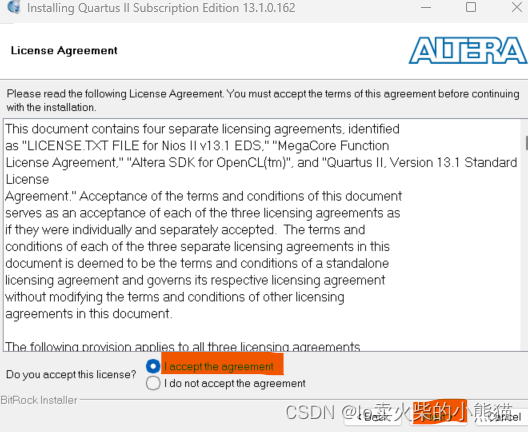

(2)选择第一个accept,再点击next

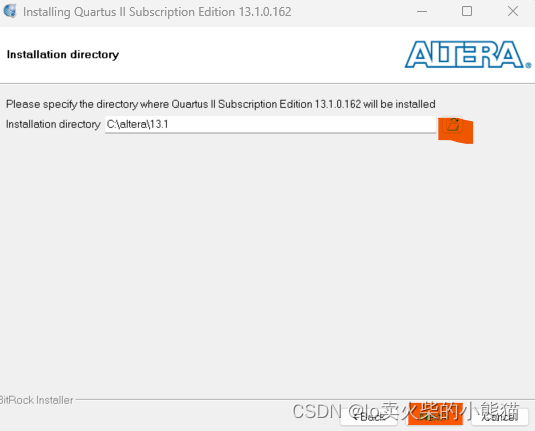

(3)选择文件夹可以自定义安装的位置,尽量建立一个新的文件夹(路径不包括中文和特殊符号)来存放,不然很多子文件夹可能会填的很乱....,选择好后点击next

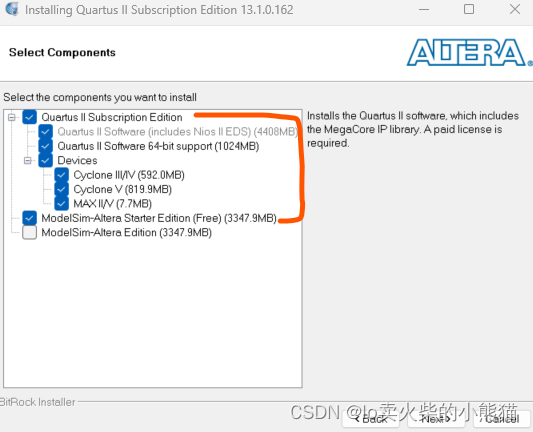

(4)除了最后一个不勾选外,其他全选(默认情况),当然也可以根据自己的芯片包需要更改Devices里面的内容,然后Next

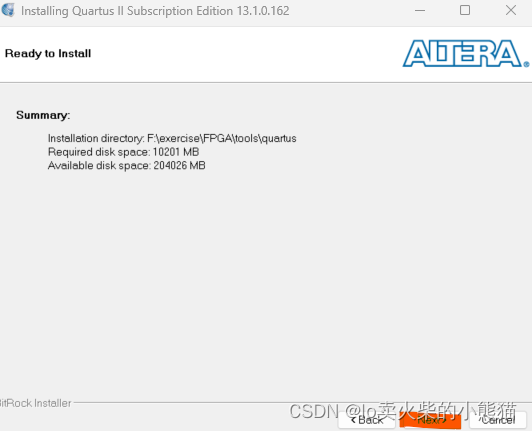

(5)Summary确保有足够的安装空间,确认后点击Next

(6)这里就开始自动安装了,需要等待一段时间

如果你之前安装过quartus却没有删除干净的话,它可能会问你是不是要建立quartus(copy),最好还是先把之前的卸载完全再重装(卸载教程在后面)

(7)完成安装后直接点击Finish,最后一个feedback不用框选

4.破解流程

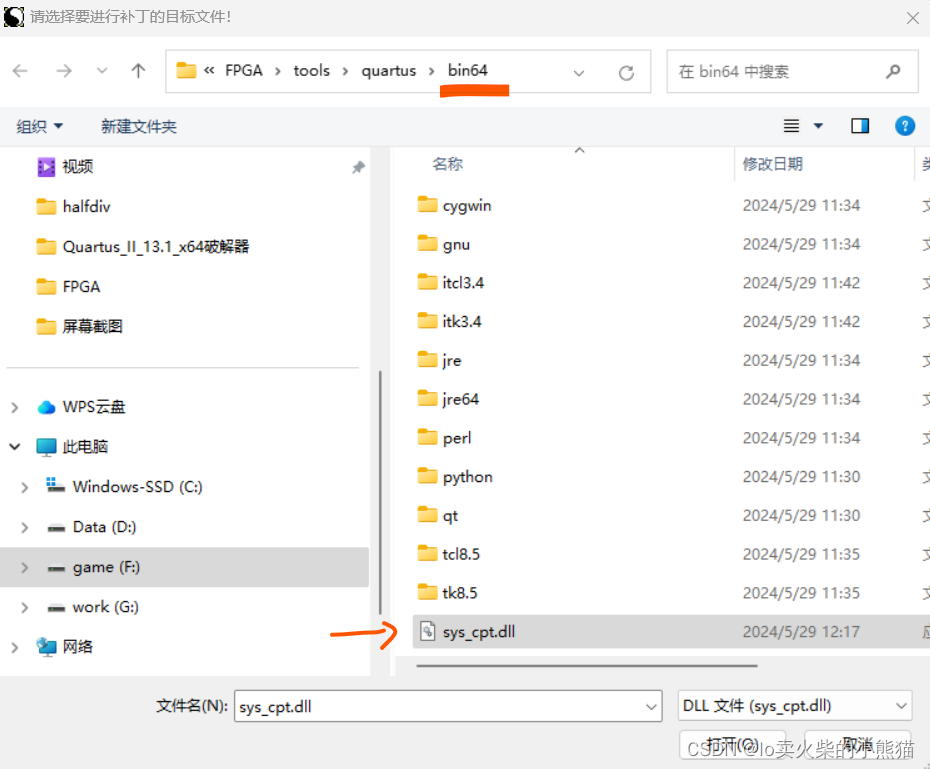

(1)64位系统解压x64破解器文件,打开破解器.exe文件

选择quartus安装目录下/bin64下的sys_cpt.dll文件,打开后点击破解器的下一步(一定要关闭软件先!!!),完成破解1后再点完成,进行gcl_afcq.dll的破解

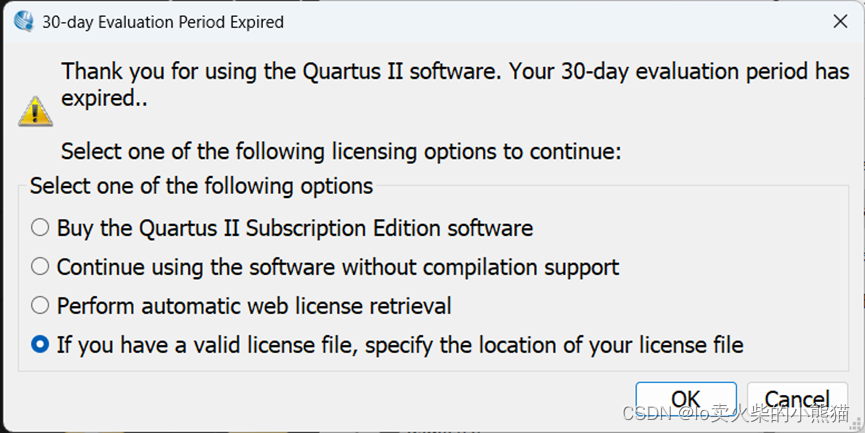

打开软件会提示30日试用,选择最后一项,选择

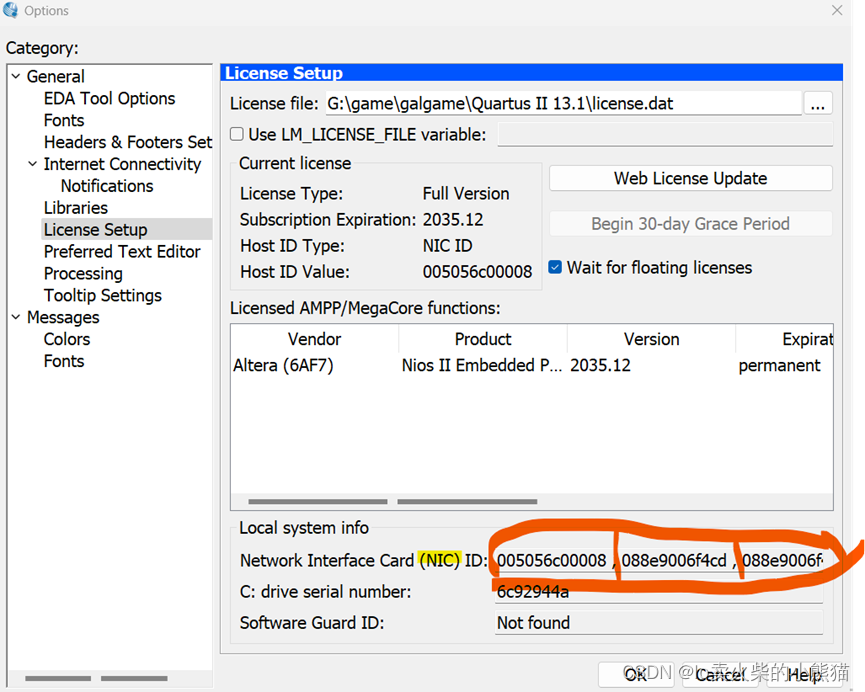

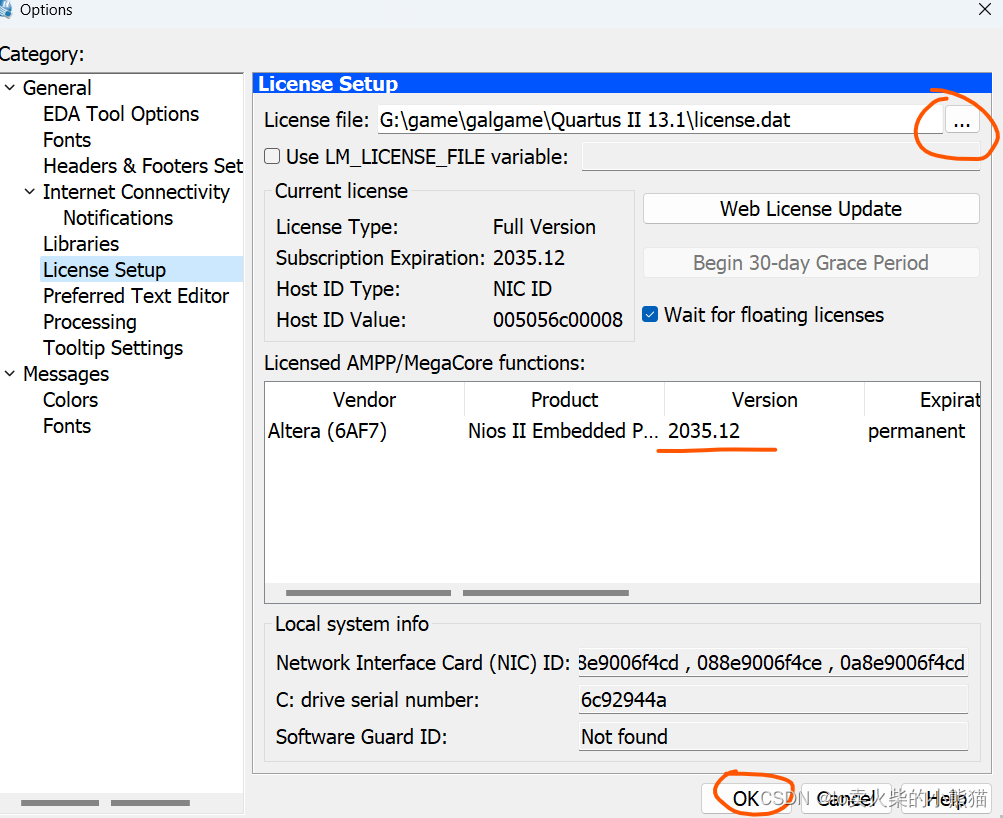

再用记事本打开license.dat文件将三个HOSTID的值改为NIC的任一值(我这里选择了第一个,默认=XXXXX),更改完成后点击文件->保存

在option中选择更改后的license.dat的地址,显示Version到2035即说明成功破解,点击OK即可打开软件

二.Modelsim-altera安装

1.选择ModelSimSetup-13.1.0.162.exe运行,开始安装

2.安装过程

(1)点击next

(2)选择第一个安装,next

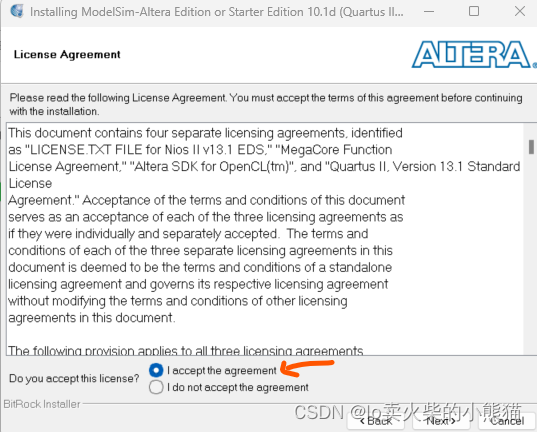

(3)选择accept然后next

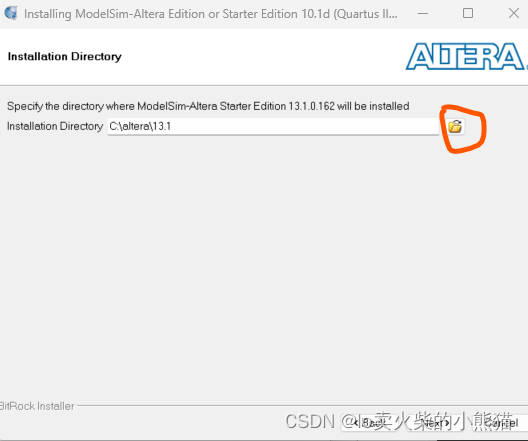

(4)单击文件夹可以更改安装位置,选择完成后next

(5)确认空间充足后next

(6)等待安装完成

(7)不用点框选,直接Finish

三.ModelSim安装

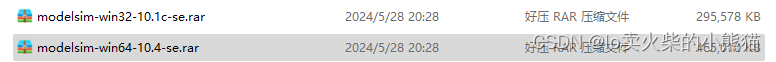

1.版本选择,32位系统选择上面win32,64位系统选择下面win64,这里我以64位的安装为例

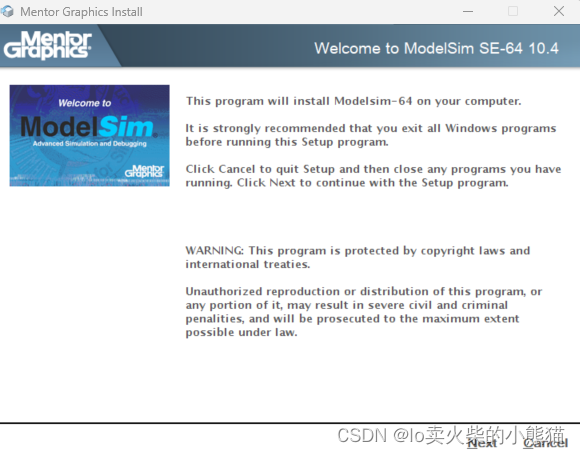

2.解压缩文件,双击运行win64-10.4-se.exe文件

3.安装流程

(1)直接单击next

(2)单击Browse可以更改安装位置,单击next

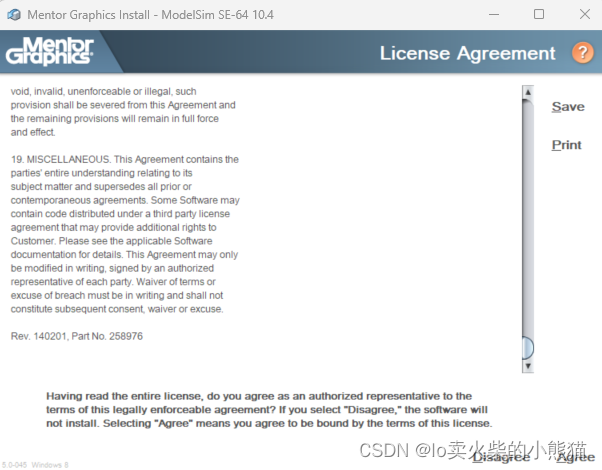

(3)直接点击Agree

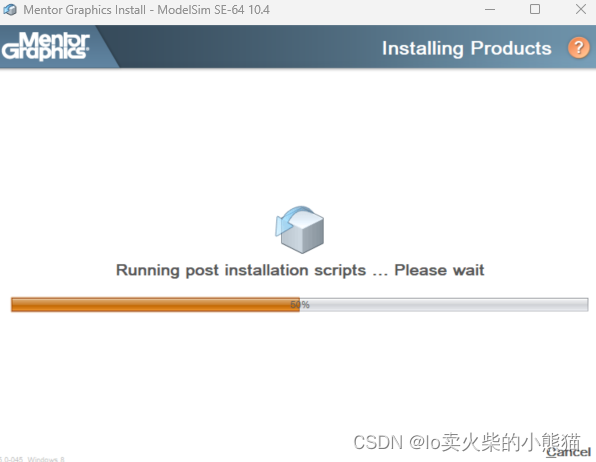

(4)等待安装完成

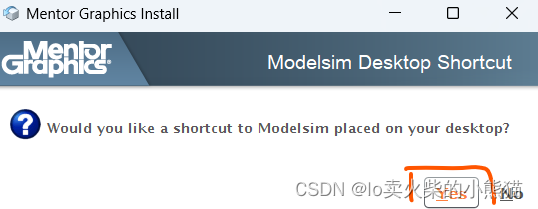

(5)50%时候会跳两个选型全选YES

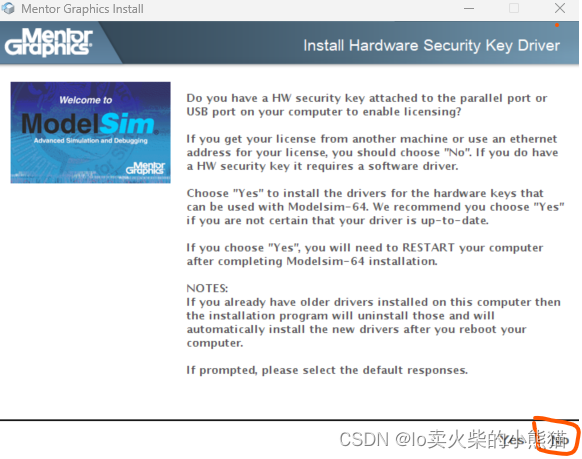

(6)最后跳出的窗口选择NO,禁止自动更新

(7)最后Done完成安装

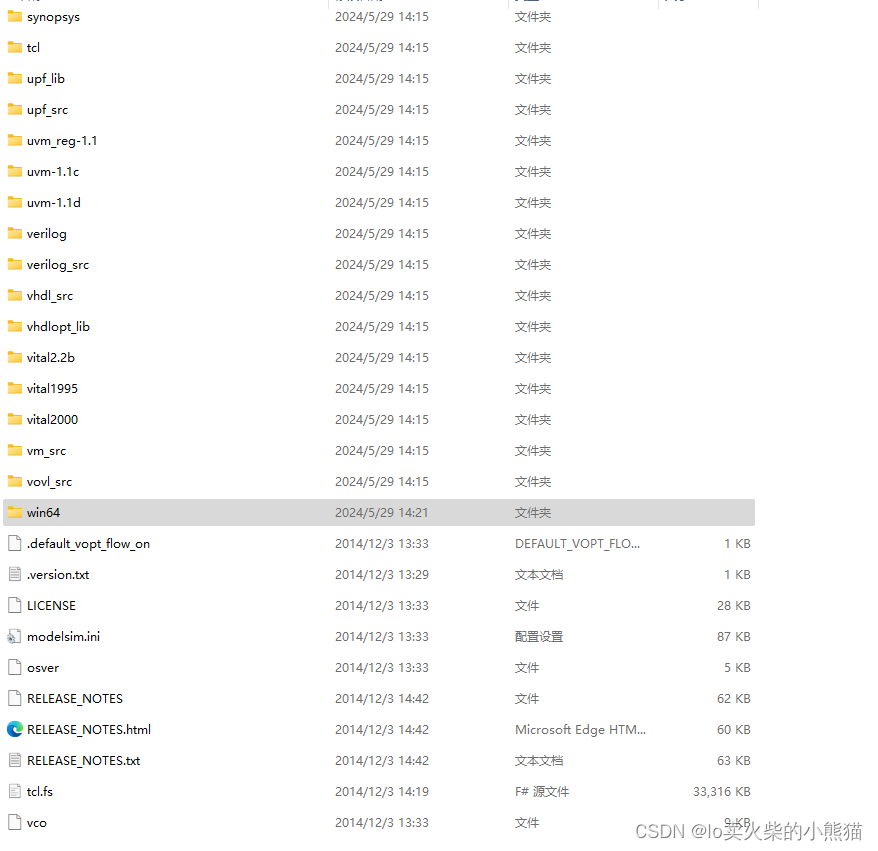

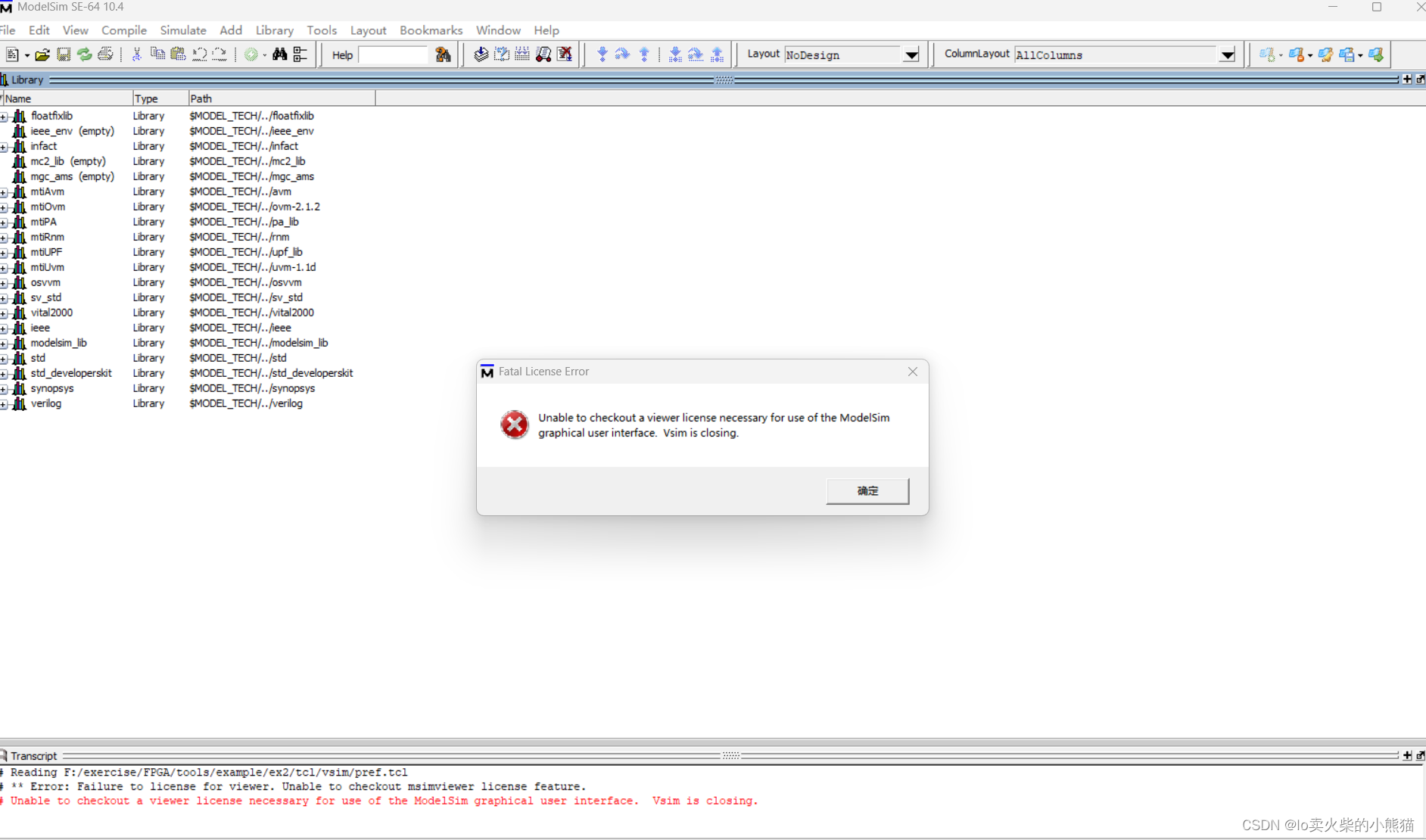

4.破解过程

(1)直接打开/win64/modelsim.exe会提示无注册,软件会自动关闭

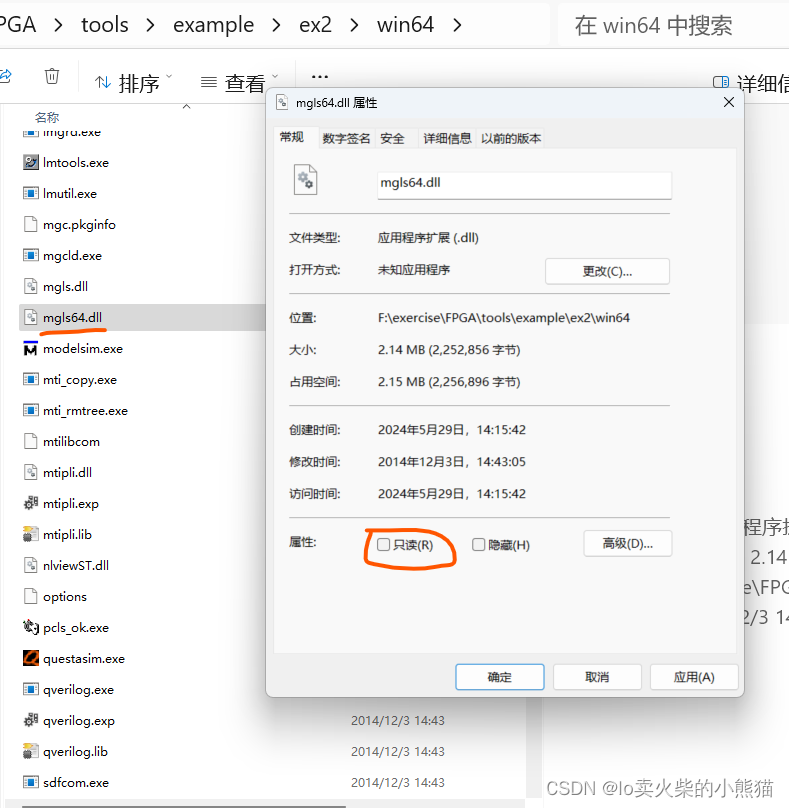

(2)修改win64文件夹中mgls64.dll的属性,取消勾选只读

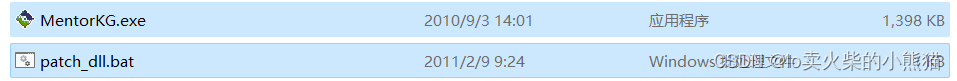

(3)打开crack文件夹,将里面的MentorKG.exe和patch_dll.bat一起拷贝到modelsim安装目录里的win64/win32(看第一步选择了哪个系统)下

(4)先确认关闭了杀毒软件,到之前win64文件夹中,运行patch_dll.bat,会自动打开cmd窗口,生成license文件,直接将其另存为win64文件夹当中

(默认存放在C:\Users\user\AppData\Local\Temp)

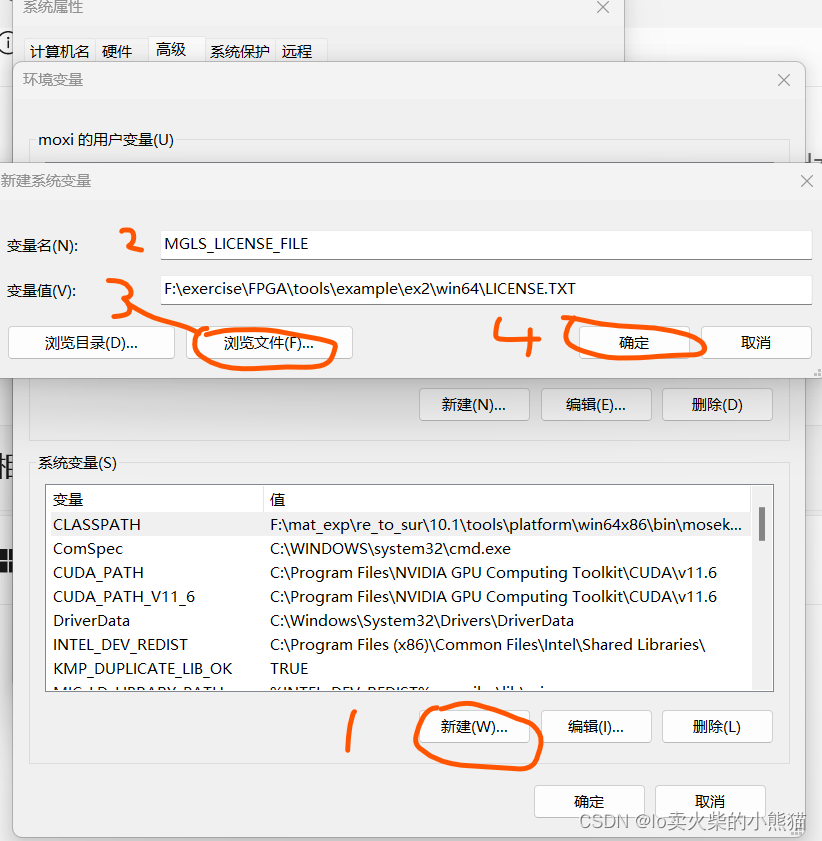

(5)右键我的电脑点击属性,在系统界面中先点击高级系统设置,再点击环境变量

(6)点击新建系统变量,设置环境变量名MGLS_LICENSE_FILE,变量值为license放置的路径,最后确定

(7)返回后在系统属性界面再点击确定

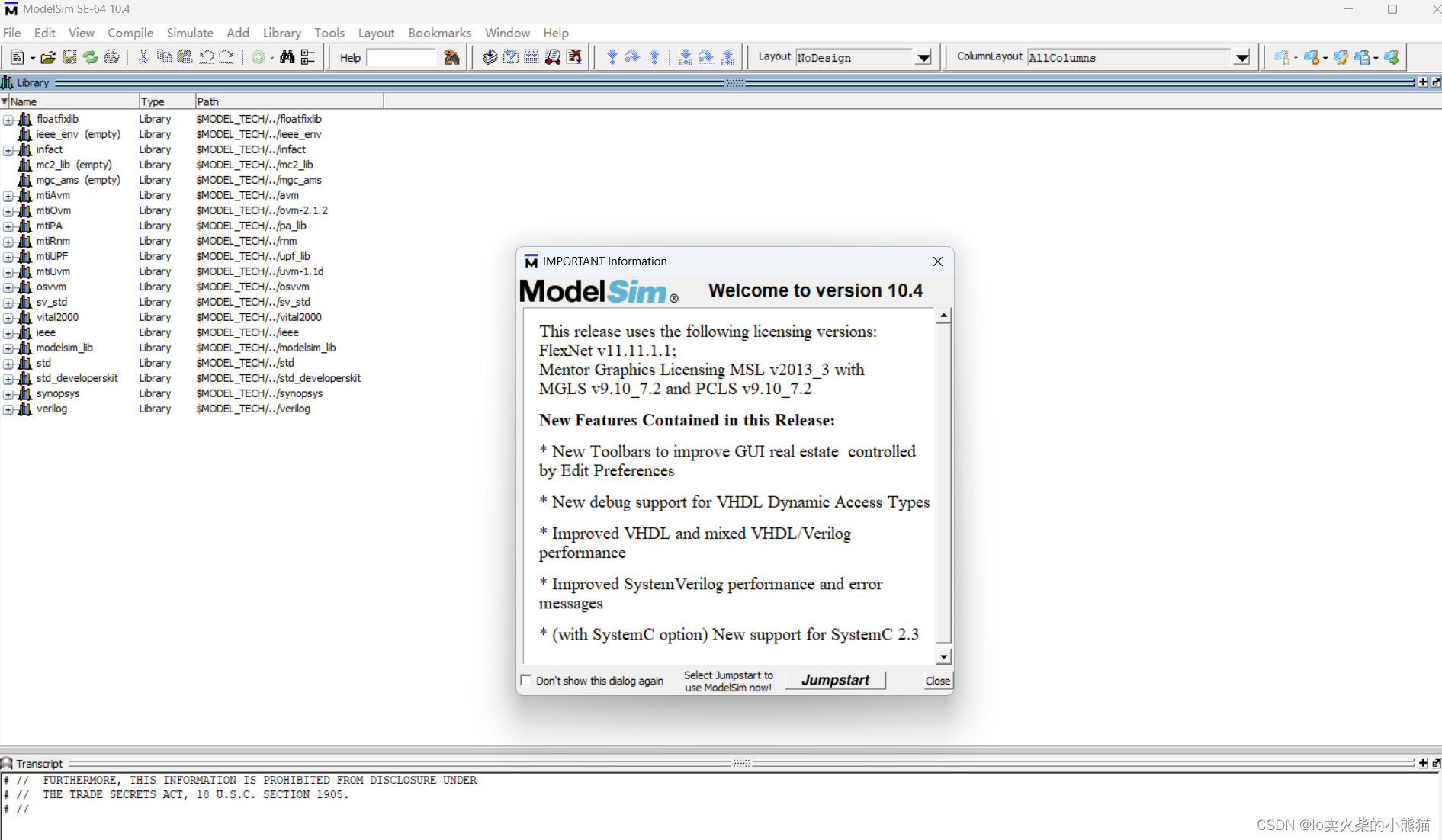

(8)重新打开modelsim se-64成功运行说明破解成功

四.Quartus和Modelsim的配置

1.通过软件快捷方式或者开始界面搜索打开quartus ii

2.

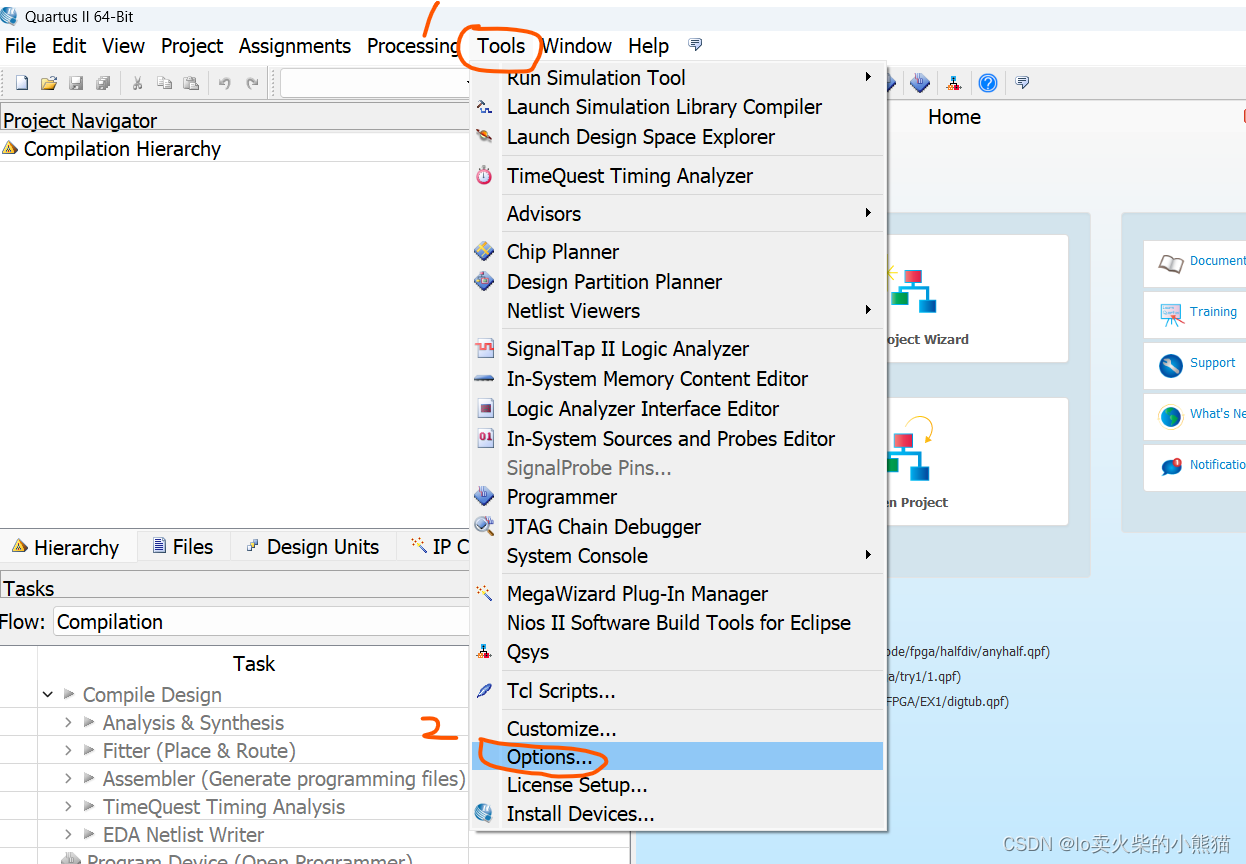

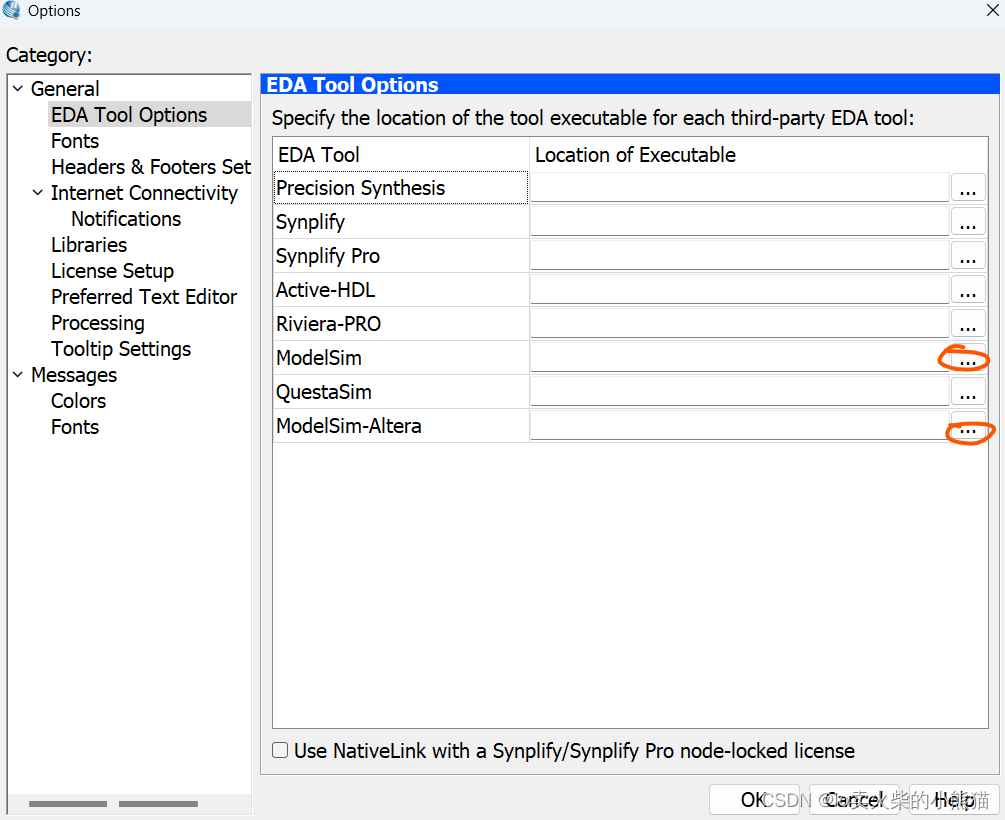

(1)打开Tools->option界面,选择EDA Tool Options,点击ModelSim和ModelSim-Altera的...选择文件

(2)ModelSim中选择win64文件夹,ModelSim-Altera中选择win32aloem文件夹,最后点击OK

3.

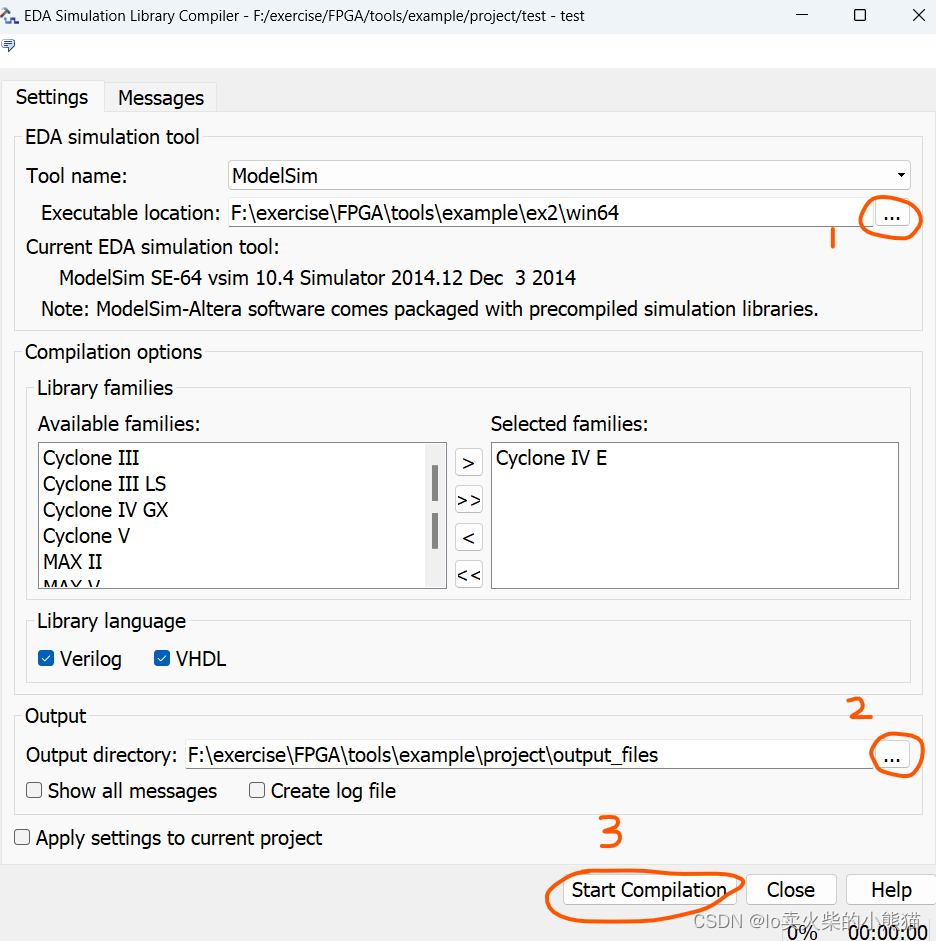

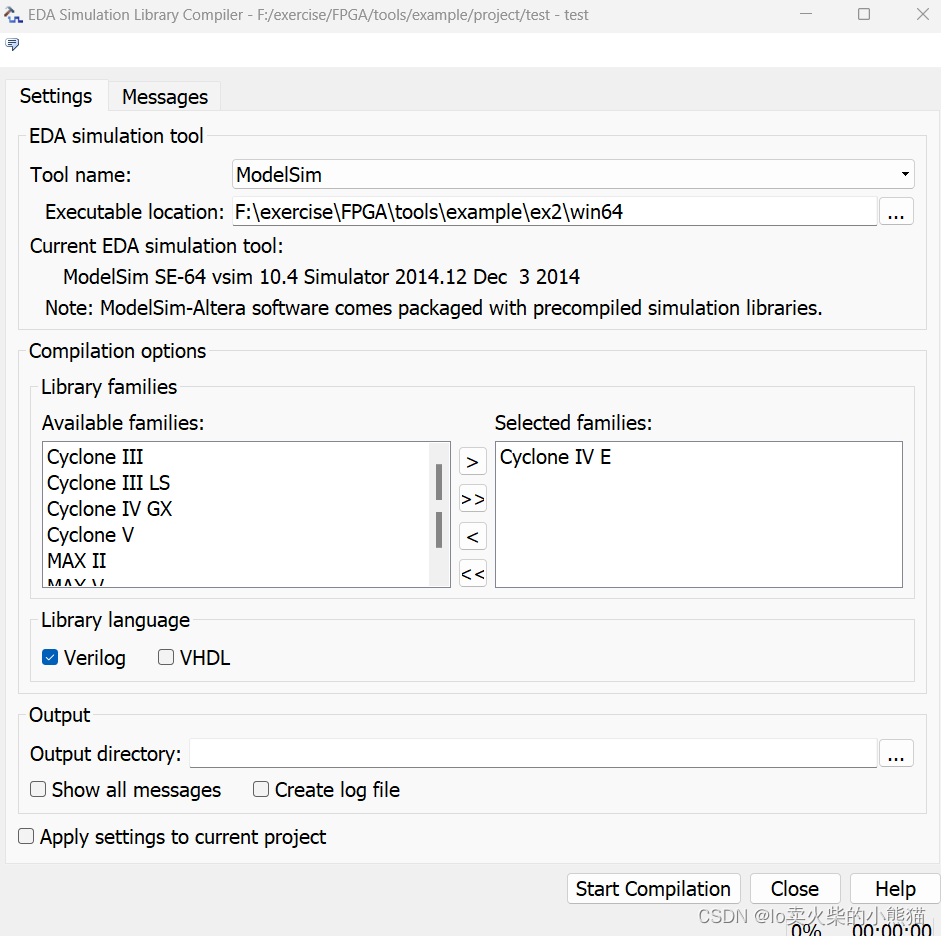

(1)配置compiler,Tools->Launch Simulaton Library Compiler

(2)Executable location选择Modelsim的win64文件夹,Output directory选择output_files(可以换其他文件夹),点击Start

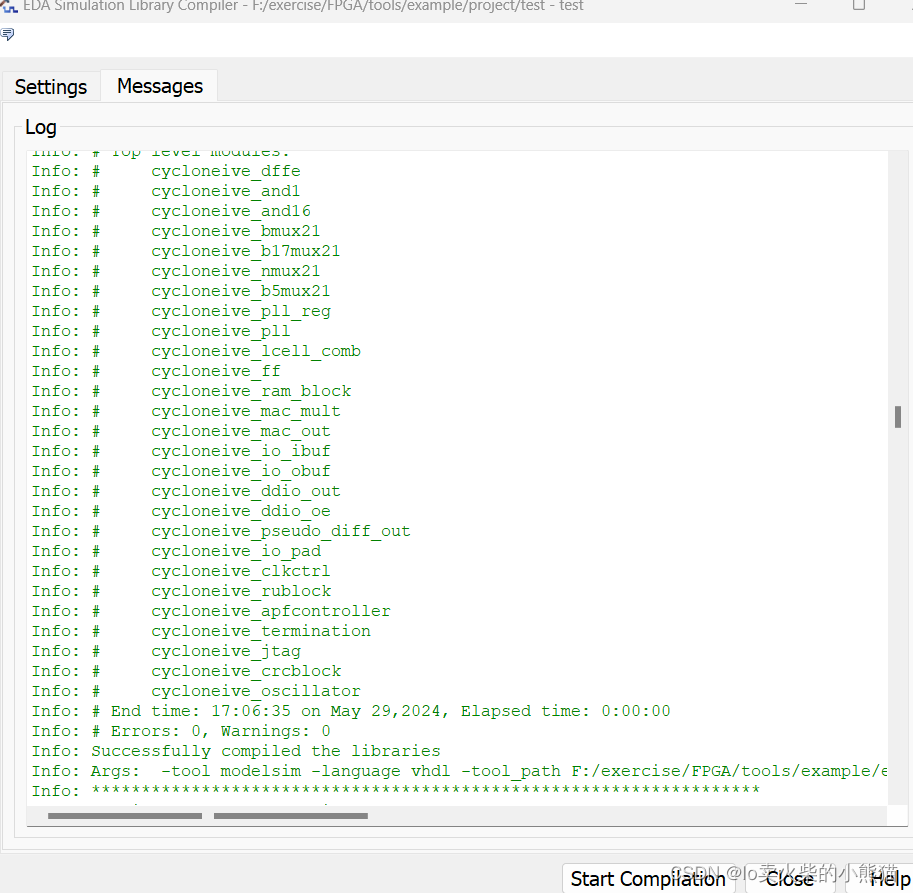

(3)编译成功显示全绿(有warning可以不管)

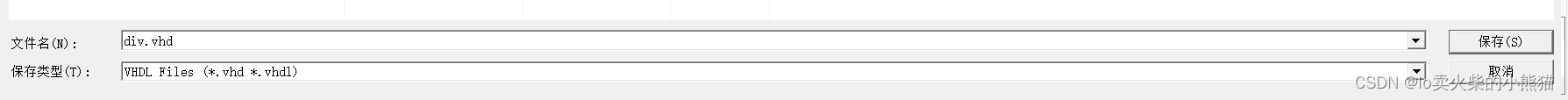

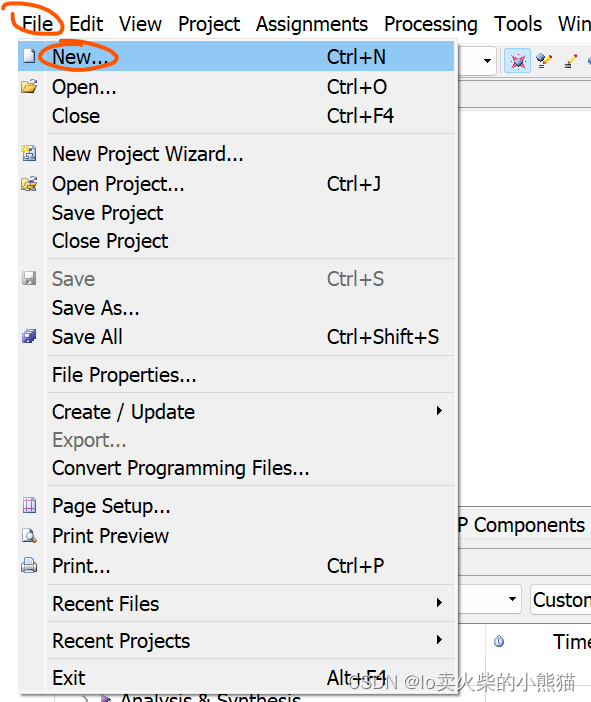

4.新建一个vhdl文件用来测试,复制测试代码进去,保存文件名为div(与entity同名)

测试代码(6分频)

library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_arith.all; use ieee.std_logic_unsigned.all; entity div is port(clk : in std_logic; rst : in std_logic; clkout :out std_logic ); end div; architecture rtl of div is constant n : integer range 0 to 10 := 6; --这里的n可以是任意值,当然要大于1. signal clk_p : std_logic; signal clk_n : std_logic; signal cnt_p : integer range 0 to n; signal cnt_n : integer range 0 to n; begin process(clk_p, clk_n) begin if((n mod 2) = 0)then clkout <= clk_p; else clkout <= clk_p or clk_n; end if; end process; process(clk, rst) begin if(rst = '0') then cnt_p <= 0; elsif(clk'event and clk = '1') then if(cnt_p = n-1) then cnt_p <= 0; else cnt_p <= cnt_p + 1; end if; end if; end process; process(clk, rst) begin if(rst = '0') then clk_p <= '0'; elsif(clk'event and clk = '1')then if (cnt_p < (n/2)) then clk_p <= '1'; else clk_p <= '0'; end if ; end if; end process; process(clk, rst) begin if(rst = '0') then cnt_n <= 0; elsif(clk'event and clk = '0')then if(cnt_n = n-1) then cnt_n <= 0; else cnt_n <= cnt_n + 1; end if; end if; end process; process(clk, rst) begin if(rst = '0') then clk_n <= '0'; elsif(clk'event and clk = '0')then if (cnt_n < (n/2)) then clk_n <= '1'; else clk_n <= '0'; end if ; end if; end process; end rtl; 5.保存后会跳出是否建立新工程,选择YES,进入工程建立指引界面

6.新建工程

(1)写入工程名,选择工程保存文件夹(建议新建空的不含中文文件夹)

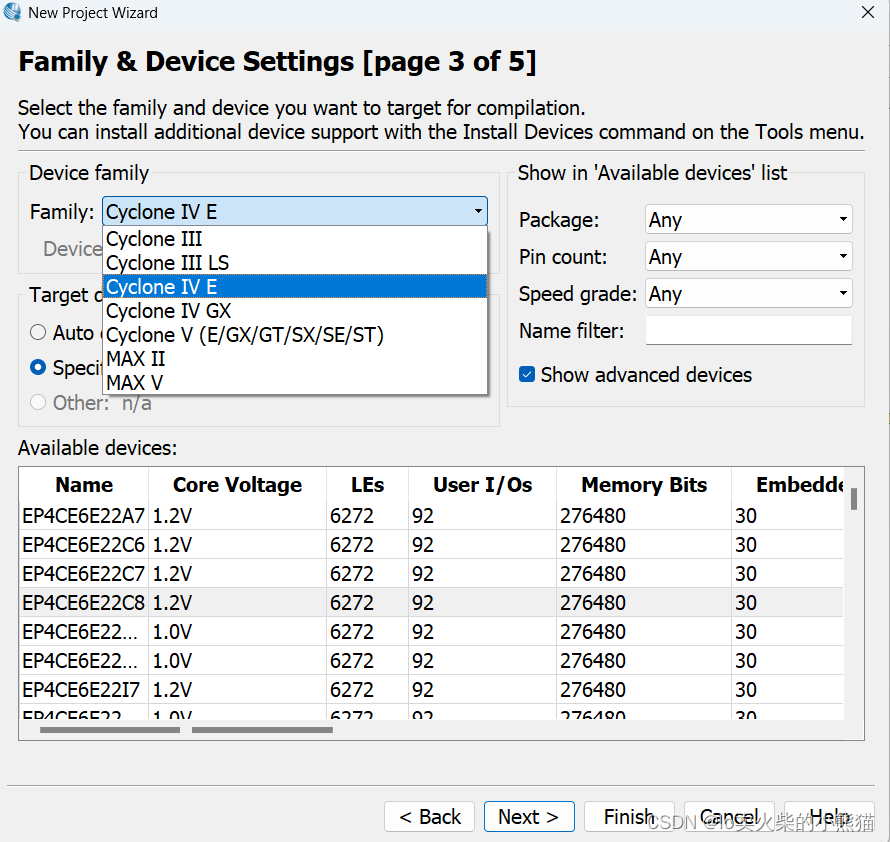

(2)完成后不加别的文件,只有div.vhd,点击next,来到芯片选择界面

(3)我这里的芯片选择是EP4CE6E22C8,先选择Famliy才会出现对应的devices,完成后next

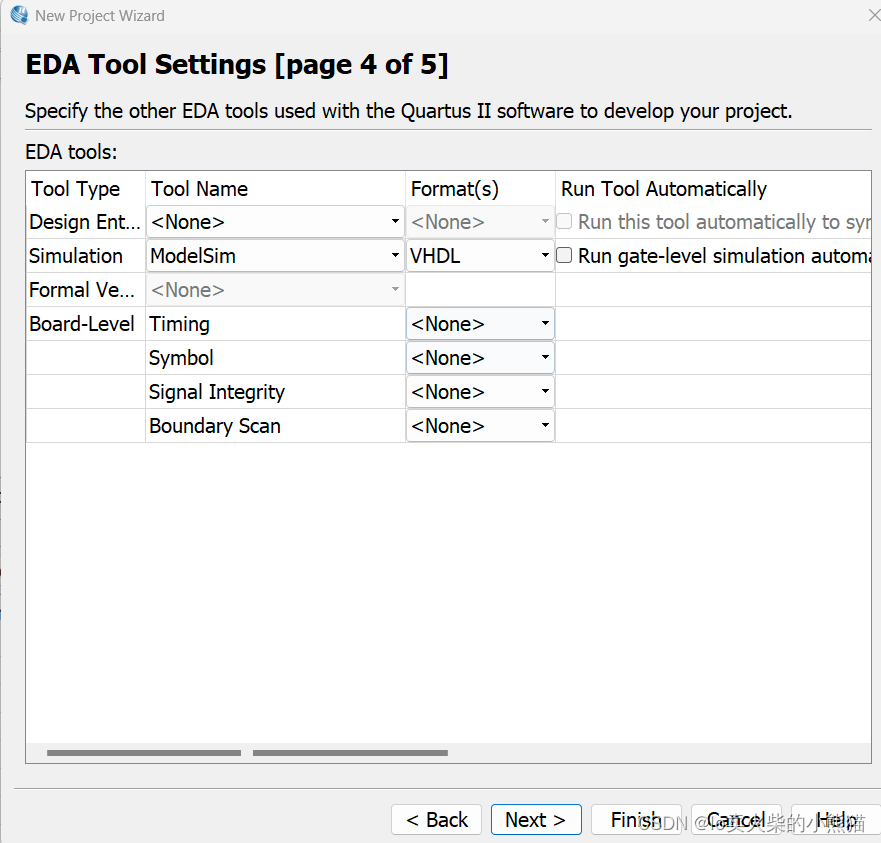

(4)Simulation选择vhdl的ModelSim,然后可以直接点击Finish,点Next的话是会显示Summary

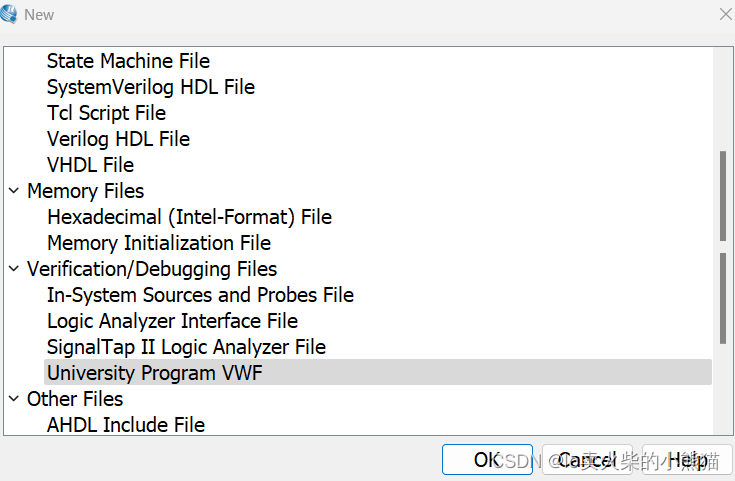

(5)在File->New->University Program VWF,最后点击OK,新建波形仿真文件VWF

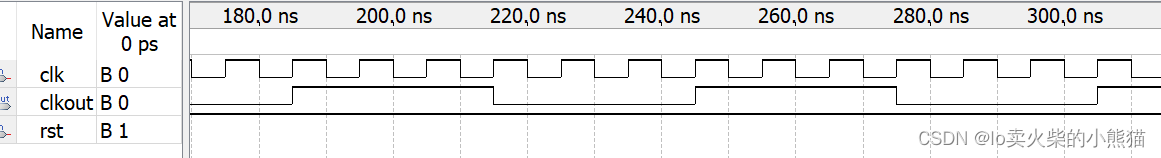

7.波形仿真

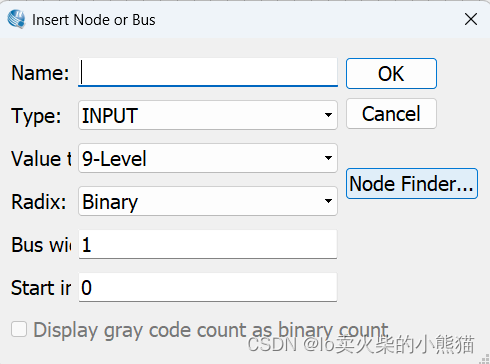

(1)右键左侧空白区域打开Insert Node or Bus

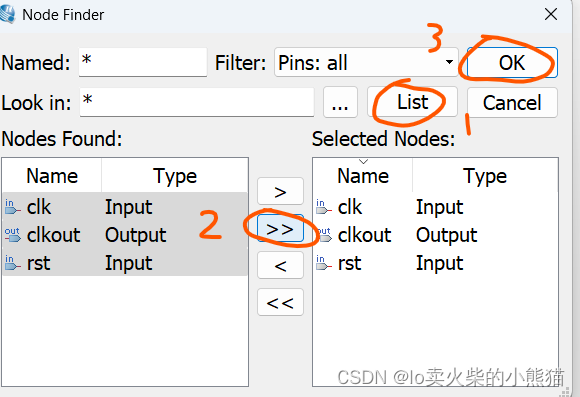

(2)选择Node Finder

(3)List相关引脚,点击>>进行全部选择移动,最后OK完成,返回后OK完成引脚插入

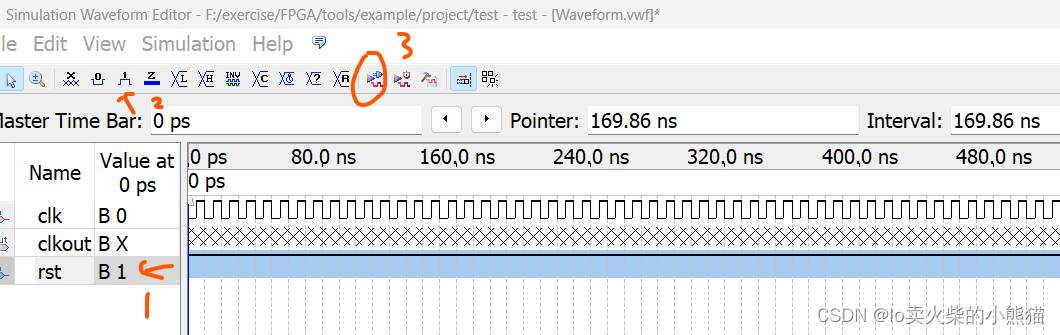

(4)接下来开始设置模拟引脚输入频率,同时将rst引脚拉高

(5)选择YES保存更改,待仿真结束即可得到结果,说明前面配置全部完成

五.遇到的问题

1.

** Error: (vdel-42) Unsupported ModelSim library format for "F:/FPGA_ FILE/FSM/simulation/modelsim/rtl _work". (Format: 4 )

. ** Warning: (vdel-57) Library 'F:/FPGA_ FILE/FSM/simulation/modelsim/rtl_ work' is missing or is not a valid ModelSim library.

** Error: D:/altera/13.0/modelsim_ ase/win32aloem/vdel failed.

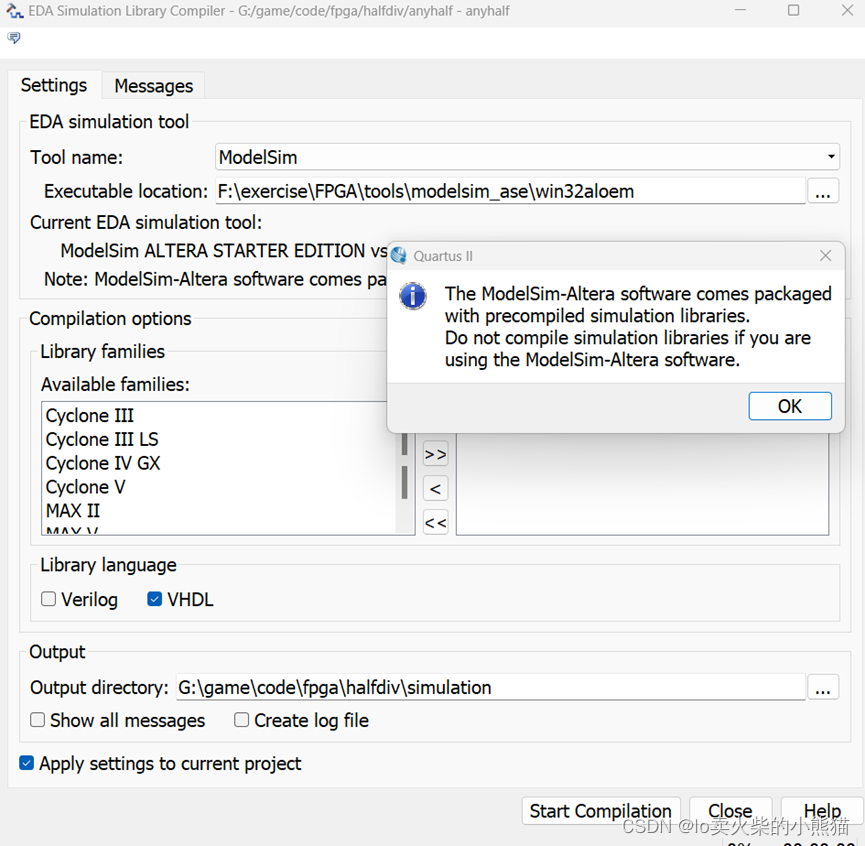

modelsim-altera软件附带了预编译的仿真库,如果使用modelsim-altera软件,则不会编译仿真库(错误中文翻译)

删除当前工程的simultaion文件夹重新仿真即可

2.

The ModelSim-Altera software comes packaged with precompiled simulation libraries

Executable location改为ModelSim的,而不是modelsim-altera

3.

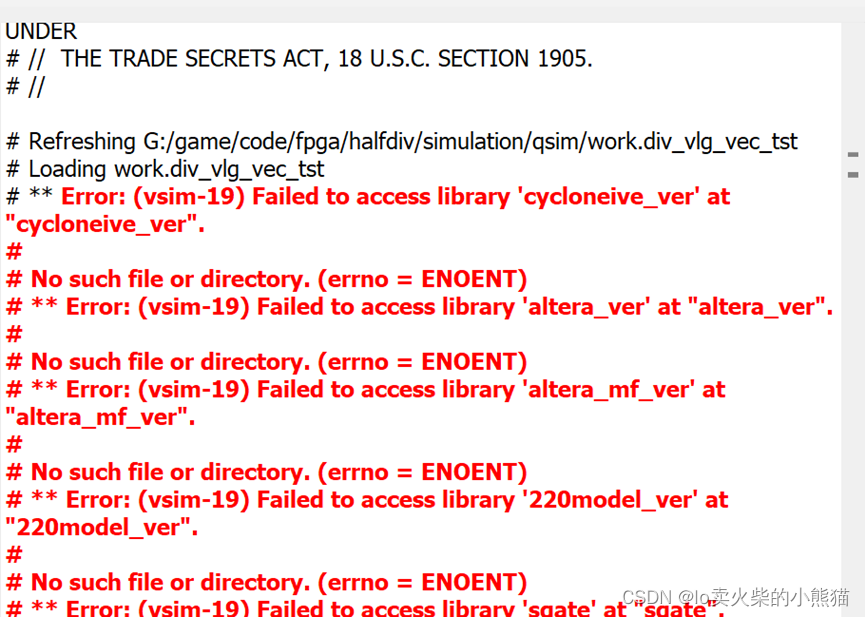

Failed to access library 'cycloneive_ver' at "cycloneive_ver"

EDA tools里面配置可能有误,可以试下加\,或者重配置

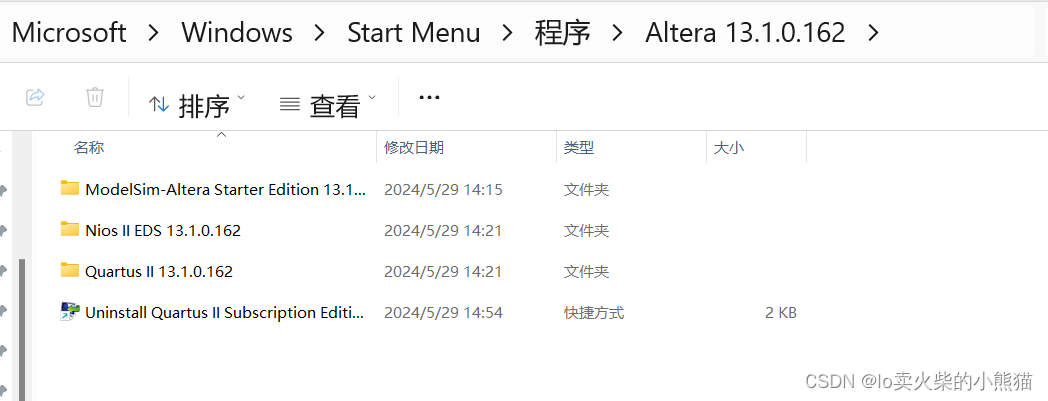

六.卸载

Modelsim是和开始界面的快捷方式放一起的,右键快捷方式打开文件所在位置即可找到,运行uninstall 即可卸载

quartus ii 卸载也是在开始的文件快捷方式当中,不过在文件外