目录

第一部分、不同的变量类型

1、wire和reg的区别

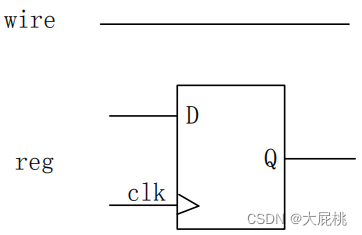

verilog中的变量类型有wire类型和reg类型。

在实际的电路中wire类型对应的就是一根导线,只存在传输的作用。而reg类型在实际电路中表示寄存器,可用来存储数据的。

如下图:

2、如何对变量进行赋值呢?

- 学习C语言可以知道赋值就是用=号,int a = 15;//将15赋值给a;

- 然而在verilog语法中也有 =(阻塞赋值) 这种赋值方式,当然除了这种方式还有 <=(非阻塞赋值)这种方式;

- 阻塞赋值 = (例如 a = b;):a的值在赋值语句执行完后立刻就改变的,用在组合逻辑;

- 非阻塞赋值 <= (例如 a <= b ;):a的值想要发生变化,必须要在时钟的上升沿/下降沿,用在时序逻辑;

3、什么是阻塞?什么是非阻塞?

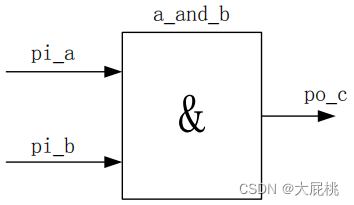

阻塞:假设信号pi_a在导线上传输的时间为5ns,pi_b在导线上传输的时间是10ns,而po_c的值因为pi_b晚到5ns而被阻塞。

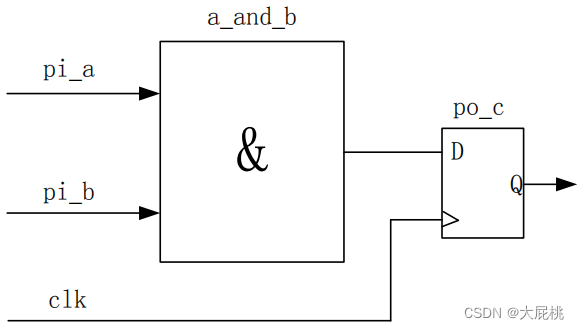

非阻塞:假设信号pi_a在导线上传输的时间为5ns,pi_b在导线上传输的时间是10ns,虽然po_c存在阻塞问题,但是Q端输出的结果只取决于clk上升沿/下降沿到来时D端的瞬时结果,因次Q输出不存在阻塞。

总结:

- 你想要在时钟的上升沿到来时才想要输出变化那就用非阻塞,你想要输出变化之取决与输入,输入变化,输出就变换那就用非阻塞。

- 组合逻辑只能用阻塞赋值,时序逻辑只能用非阻塞赋值。

第二部分、变量位宽的定义

1、各种系统默认情况

不注明位宽的情况下,默认位宽为1。

input a;//默认为wire类型,位宽为1位 reg clk; reg key1,key2;2、变量位宽声明方式

wire [高位:低位]变量名; reg [高位:低位]变量名; wire [高位:低位]变量名[denth:0];//表示数据深度 reg [高位:低位]变量名[denth:0];//表示数据深度 //上面这种定义调用时 变量名[i]; 默认认为是第几个数据,而不是该数据的第几位,除非再加一个括号,才表示第几位3、表明位宽的情况下,赋值方式

//wire类型的变量 wire [7:0] value; assign value = 8'd255 = 8'hff = 8'b1111_1111 = 'd255;//你是几位,那么赋值就一定要带上那个位数,不管你赋的什么值 assign value = 255;//系统默认255为32位的十进制数据,然后截取低8位数据到value中。 //reg类型的变量 reg [7:0] value; assign@ (posedge clk) begin value <= 8'd255; value <= 8'hff; value <= 8'b1111_1111; value <= 'd255; end4、两个模块之间例化,不定义变量直接用的方式

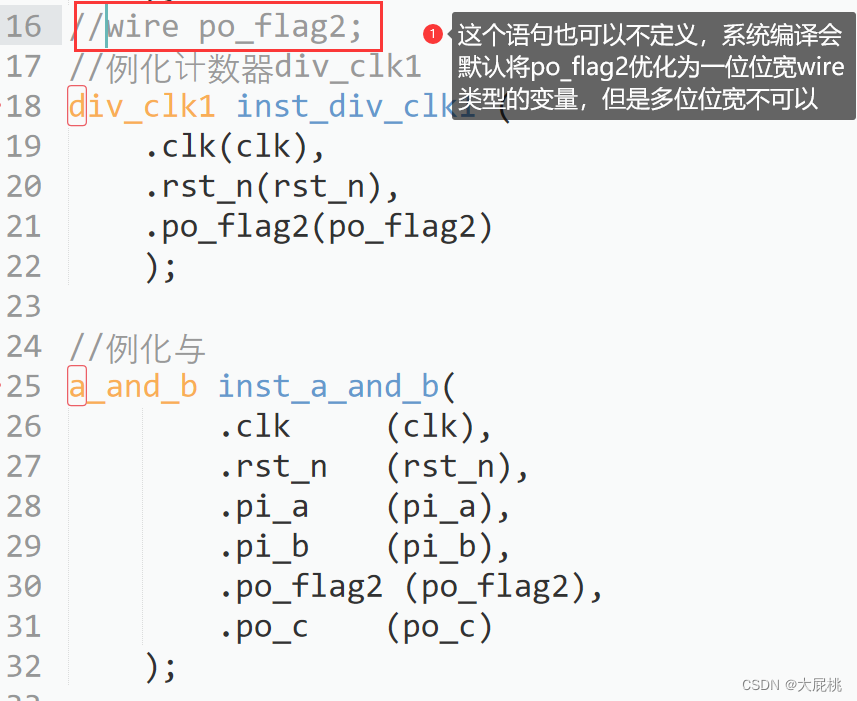

一位位宽的wire类型变量在不输入也不输出的情况下,可以不声明,但是这种做法不推荐,容易翻车,写的代码别人看不懂。

5、常用的变量定义为参数

注意:parameter后面的参数建议定义成大写字符

一般情况下,变量定义为小写字母,参数定义为大写字母。

parameter LEN 100;//相当于C语言中的#define LEN 100第三部分、赋值语句

1、assign和always赋值语句的区别

1、assign赋值语句:

- assign只能实现组合逻辑;

- assign语句后面只能跟一条语句;

- wire型变量,必须在assign中进行赋值。

assign 表达式;2、always赋值语句:

- always赋值语句不但能实现时序逻辑,还能实现组合逻辑;

- reg型变量,必须在always中进行赋值;

- always敏感信号可分为边沿触发和电平触发;

- 电平触发时always@(*) = always@(a or b) = always@(a ,b);

- 电平触发:敏感列表触发电平信号不全会导致锁存器的产生;

- always@(边沿触发):非阻塞赋值语句,对应时序逻辑电路。

- always@(电平触发):阻塞赋值语句,对应组合逻辑电路。

注意:一个变量只能在一个always语句块中被赋值,不能在两个语句块中赋值,因为always语句块是并行执行的,会产生冲突。

always@(敏感信号)begin 语句; end2、assign和always赋值语句的例子

module variable_assignment( input wire clk, input wire a, input wire b, output wire c, output reg c1, output reg c2 ); //assign combinatorial logic assign c = a & b; //always combinatorial logic always@(*)begin c1 = a & b; end always@(a,b)begin//equivalence c1 = a & b; end always@(a or b)begin//equivalence c1 = a & b; end //sequential logic always @(posedge clk)begin c2 <= a & b; end endmodule3、inital语句

- inital语句是初始化语句,但是不能写在可综合模块中,因为有些综合软件无法综合inital语句。

- inital语句中被赋值的变量必须是reg类型。

//举例子 initial begin clk = 0; a = 0; b = 0; end4、reg类型变量的初始值问题

- reg类型的变量是可以赋初始值,但是有个条件就是这个reg类型的变量不能在后面的语句中被综合为了组合逻辑,只有reg是时序逻辑才可以在fpga里赋值初始值。(最好是这样,记住就可以)

- reg变量既可以生成时序逻辑,也可以生成组合逻辑。

- reg赋初始值时要用阻塞赋值。

第四部分、运算符号

1、算数运算符(+,-,*,/,%)

注意:在功能模块中尽量减少使用*,/,%这三种运算。

2、关系运算符(>、=、<=、>=、==、!=)

注意:小于等于(<=),在条件判断语句中和非阻塞赋值有点像,所以一定要注意,不要犯错!!

3、逻辑运算符(&&、||、!)

返回的值要么为真,要么为假。

4、位运算符(&、|、~)

5、三目/条件运算符((x)?x:x)

6、赋值运算符(= 、<=)

7、移位运算符(>>、<<)

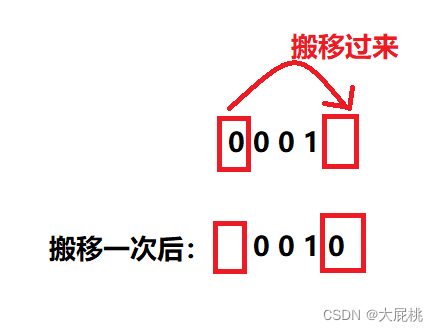

多次左移,会使数据溢出,例如0001,在左移4次后会变为0000,丢失一位数据,回到0。这在循环右移的代码中就会节约一个选择器。

8、位拼接运算符({})

一个非常巧妙的利用位拼接符实现循环左移的方法。

妙蛙种子吃了妙脆角妙进米奇妙妙屋,秒到家的移位操作!!!!!!

示例如下:

module operational_sign_homework( input wire clk, input wire rst, output reg [7:0]po_a = 1'b0//give an initial value ); //循环左移的方式 always@(posedge clk) begin if(rst == 1'b1) //这里采用同步复位的方式 po_a <= 8'd1; else if(po_a == 8'b1000_0000)//多消耗一个寄存器 po_a <= 8'b0000_0001; else po_a <= po_a << 1; //通过位拼接操作符来实现循环左移(太刁了,比上面的方法好) always@(posedge clk) begin if(rst == 1'b1) po_a <= 8'd1; else po_a <= {po_a[6:0],po_a[7]};//每来一次上升沿,我就搬移一次,就形成了循环 end endmodule第五部分、条件判断语句

条件判断语句有if else 和 case endcase这两种,这两种语句的赋值都必须放在always语句中。

1、if else语句的注意事项

1.1、if else语句叠加不能太多,老师的经验是不能大于8级,因为if else是串行执行的语句,如果太多就会导致线路的延时太多,进而导致时序违例。

1.2、if else语句书写的时候要考虑优先级。

1.3、if else语句结尾尽量以else结尾,这样可以避免锁存器的产生。

什么是时序违例?

也就是说:当前时钟上升沿我把信号给了当前的电路模块,因为当前个电路模块时延很严重,经过一个时钟周期后,到了下一个时钟的上升沿,正常情况下你这个模块就应该输出处理好的输出信号,结果因为时延,我在输出端口检测不到输出信号。

通常表现上是:建立时间不满足要求通常是因为组合逻辑处理时间太长、保持时间不满足要求通常是因为组合逻辑处理时间太短。

2、begin end问题

begin end就是括号等价于C语言中{}。

always@(posedge clk) begin if(rst == 1'b1) po_a <= 8'd1; else po_a <= 8'd0; end //需要注意的是,加begin end和不加begin end都是对的!!!! always@(posedge clk) if(rst == 1'b1) po_a <= 8'd1; else po_a <= 8'd0;3、case endcase语句的注意事项

- case语句结尾必须时endcase。

- case语句是并行执行,(多路选择器)所以多种条件时使用case endcase语句比使用if else速度要快,但是case endcase也不能非常多。

- case的条件在没有完全列清楚的情况下,要用default语句。

//可以带上begin end always@(posedge clk) case(po_a) 1: po_a <= 8'd1; 2: po_a <= 8'd2; default: po_a <= 8'd0; endcase //带上begin end always@(posedge clk) case(po_a) 1:begin po_a <= 8'd1; end 2: po_a <= 8'd2; default: po_a <= 8'd0; endcase 第六部分、赋值分隔符问题

当在数值前面声明了位宽以及进制,这种表达方式可以放数值的分隔符。

下面两种表达方式都可以,这两条语句完全等价:

parameter END_COUNT = 'd49_999_999; parameter END_COUNT = 26'd49_999_999;//这两条语句完全等价当数值前面没有带位宽以及进制,系统默认为32位的十进制数据,这个时候无法再对数据放置分隔符。

错误的表达方式:

parameter END_COUNT = 49_999_999;//错误的表达方式第七部分、编写测试代码时常用的语句

1、随机数产生代码

a = {$random}%256;//产生0~255的随机数据2、初始化代码模块

initial begin clk = 0; rst_n = 0; #100; rst_n = 1; end3、时钟产生代码

always #20 clk = ~clk;4、延时代码

#200;//延时200ns第八部分、总结

这些都是我在使用过程的一些总结,希望能够对你帮助🤓🤓🤓。

然后这篇文章将给大家带来一个新的系列那就是【FPGA入门】,我会在这个系列中记录一些有趣的实验和心得,虽然之前也写过FPGA的相关内容,但是那部分内容主要是学习Altera中的Nios II中的IP核。

而这个系列是我正式入门FPGA学习的过程,所以我会尽量保证接下来每一篇文章的质量,当然我也是一个比较笨的人,写博客的过程中总有一些错误,希望读者发现后及时告诉我,我们一起进步。

最后,希望大家可以继续关注后面的文章。冲!