阅读量:0

名称:基于FPGA的简易电子琴设计Verilog代码Quartus仿真(文末获取)

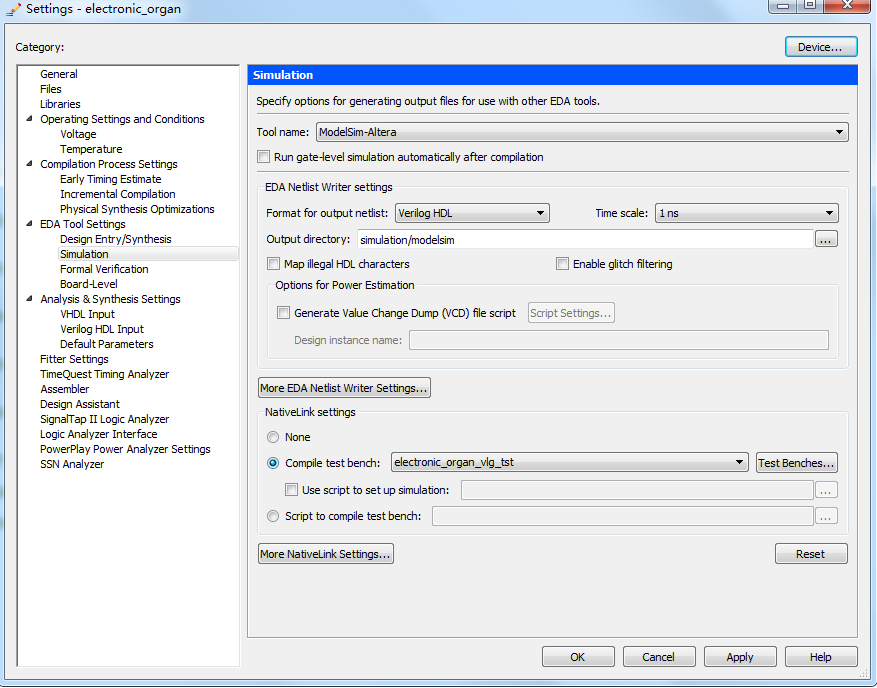

软件:Quartus

语言:Verilog

代码功能:

基于 Verilog HDL的简易电子琴设计

实验目的和要求

1、主要学习基于 Verilog HDL语言进行数字电路系统设计的基本方法;

2、学习 Quartusll软件平台、 Modelsim仿真平台和互联网+实验平台的使用方法。

二、实验原理

设计任务:学习中讲授的各种方法,查阅资料,设计一个简易的电子琴,并在实验平台上实现。该电子琴有7个按键,对应1234567七个音阶,1的对应频率是440Hz,2对应的频率是493.9Hz,…7对应的频率是830.61Hz。当有按键按下后,在一个数码管上显示对应的音阶。输出的声音可以接发光二极管。整个电子琴有一个开关能控制声音输出还是不输出。画出系统组成的框图,划分模块。

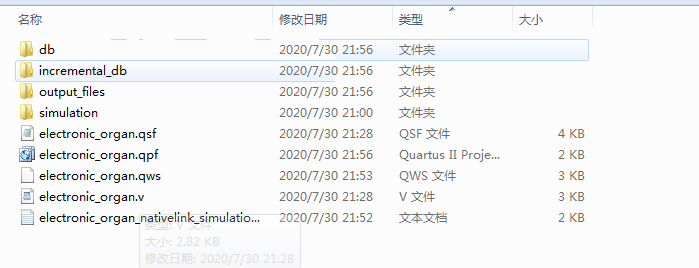

1. 工程文件

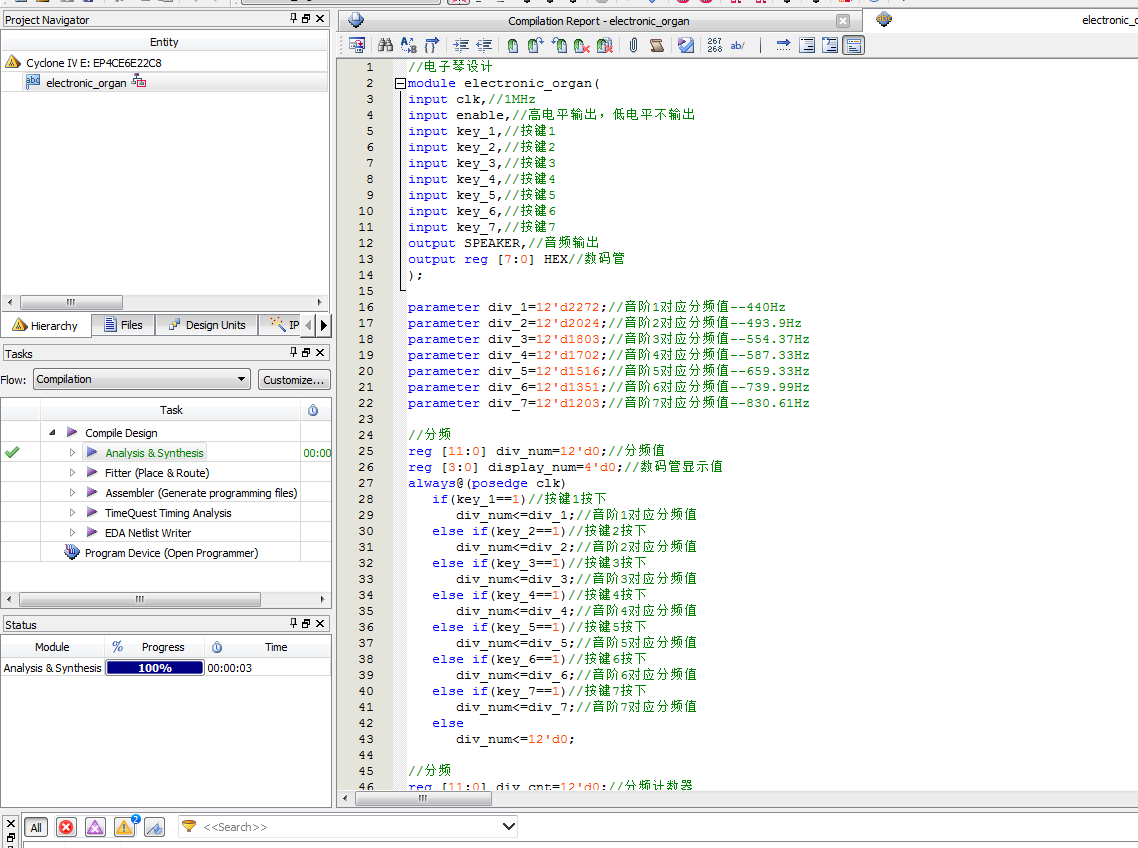

2. 程序文件

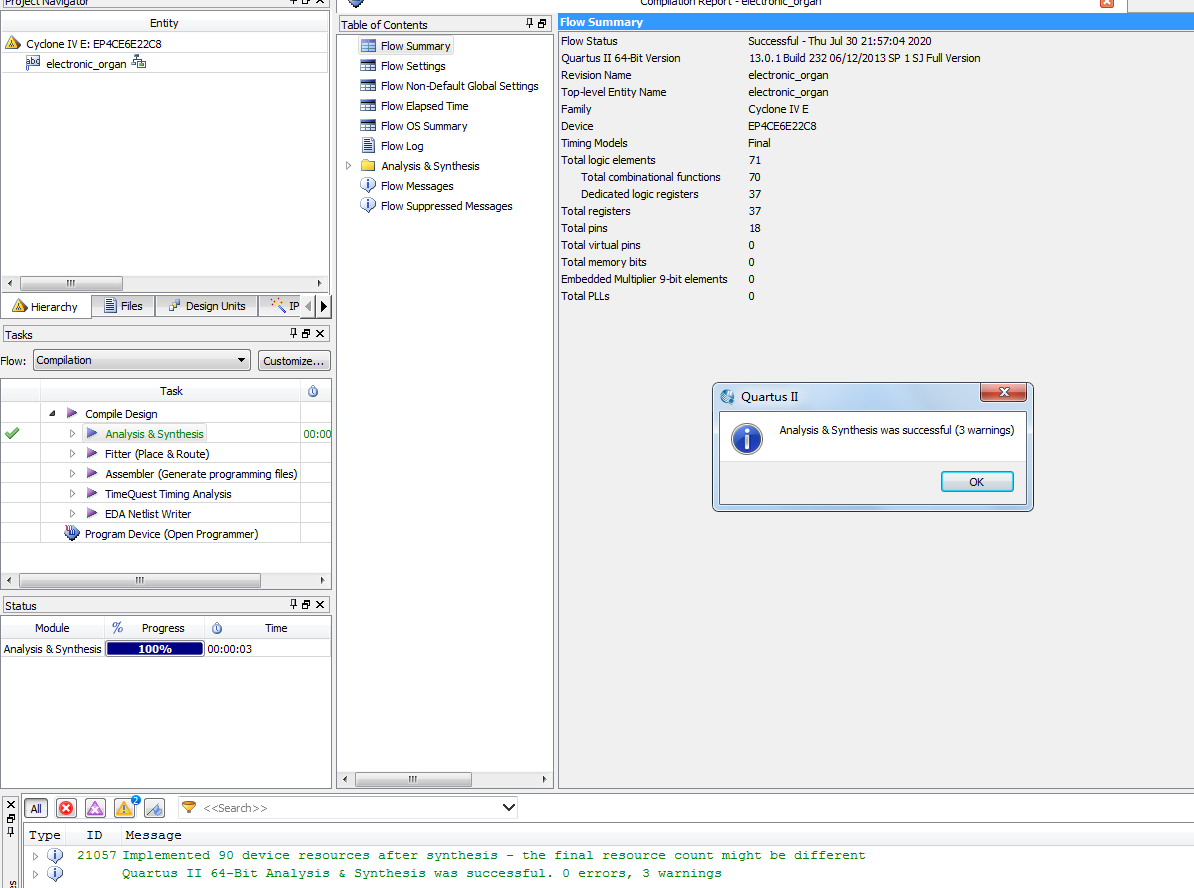

3. 程序编译

4. RTL图

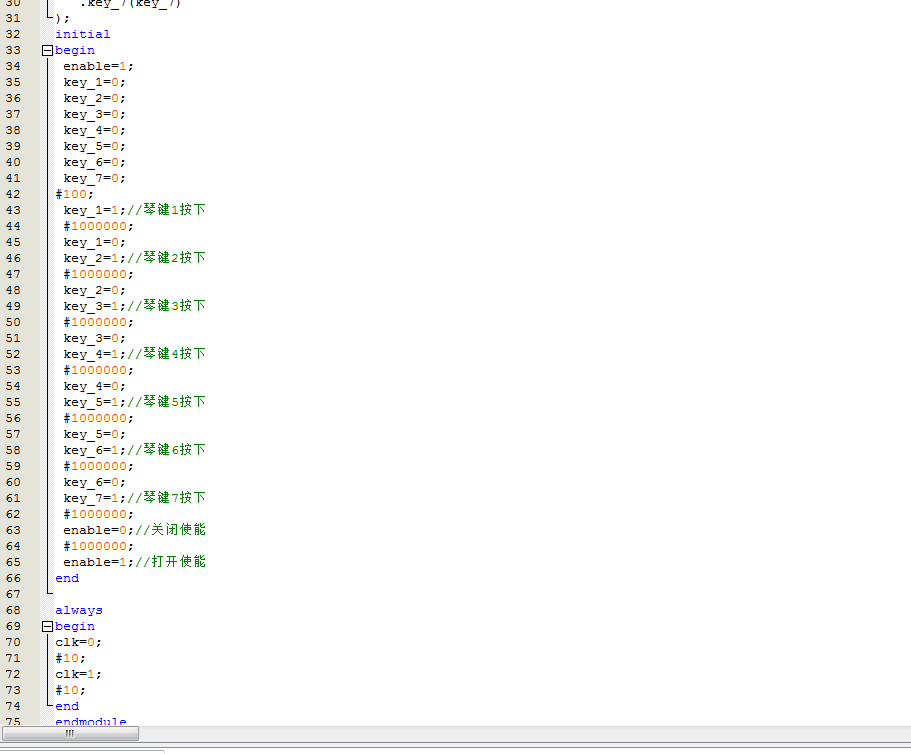

5. Testbench(仿真文件)

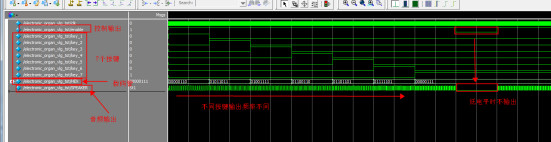

6. 仿真图

部分代码展示:

//电子琴设计 module electronic_organ( input clk,//1MHz input enable,//高电平输出,低电平不输出 input key_1,//按键1 input key_2,//按键2 input key_3,//按键3 input key_4,//按键4 input key_5,//按键5 input key_6,//按键6 input key_7,//按键7 output SPEAKER,//音频输出 output reg [7:0] HEX//数码管 ); parameter div_1=12'd2272;//音阶1对应分频值--440Hz parameter div_2=12'd2024;//音阶2对应分频值--493.9Hz parameter div_3=12'd1803;//音阶3对应分频值--554.37Hz parameter div_4=12'd1702;//音阶4对应分频值--587.33Hz parameter div_5=12'd1516;//音阶5对应分频值--659.33Hz parameter div_6=12'd1351;//音阶6对应分频值--739.99Hz parameter div_7=12'd1203;//音阶7对应分频值--830.61Hz //分频 reg [11:0] div_num=12'd0;//分频值 reg [3:0] display_num=4'd0;//数码管显示值 always@(posedge clk) if(key_1==1)//按键1按下 div_num<=div_1;//音阶1对应分频值 else if(key_2==1)//按键2按下 div_num<=div_2;//音阶2对应分频值 else if(key_3==1)//按键3按下 div_num<=div_3;//音阶3对应分频值 else if(key_4==1)//按键4按下 div_num<=div_4;//音阶4对应分频值 else if(key_5==1)//按键5按下 div_num<=div_5;//音阶5对应分频值 else if(key_6==1)//按键6按下 div_num<=div_6;//音阶6对应分频值 else if(key_7==1)//按键7按下 div_num<=div_7;//音阶7对应分频值 else div_num<=12'd0; //分频 reg [11:0] div_cnt=12'd0;//分频计数器 always@(posedge clk) if(div_cnt>=div_num)//计数最大值后回零 div_cnt<=12'd0; else div_cnt<=div_cnt+12'd1;//计数 reg beep=0;//频率信号 always@(posedge clk) if(div_cnt<=div_num/2)//计数最大值后回零 beep<=0;//音频输出 else beep<=1;//音频输出

源代码

扫描文章末尾的公众号二维码